# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# Stability, Reliability, and Robustness of GaN Power Devices: A Review

Kozak, Joseph Peter

Zhang, Ruizhe

Porter, Matthew

Song, Qihao

他

https://hdl.handle.net/2324/7330777

出版情報:IEEE Transactions on Power Electronics. 38 (7), pp.8442-8471, 2023-07. Institute of

Electrical and Electronics Engineers (IEEE)

バージョン:

権利関係: Creative Commons Attribution 4.0 International

# Stability, Reliability, and Robustness of GaN Power Devices: A Review

Joseph Peter Kozak , Member, IEEE, Ruizhe Zhang , Graduate Student Member, IEEE, Matthew Porter, Student Member, IEEE, Qihao Song, Graduate Student Member, IEEE, Jingcun Liu, Bixuan Wang, Graduate Student Member, IEEE, Rudy Wang, Senior Member, IEEE, Wataru Saito, Senior Member, IEEE, and Yuhao Zhang, Senior Member, IEEE

Abstract—Gallium nitride (GaN) devices are revolutionarily advancing the efficiency, frequency, and form factor of power electronics. However, the material composition, architecture, and physics of many GaN devices are significantly different from silicon and silicon carbide devices. These distinctions result in many unique stability, reliability, and robustness issues facing GaN power devices. This article reviews the current understanding of these issues, particularly those related to dynamic switching, and their impacts on system performance. Instead of delving into reliability physics, this article intends to provide power electronics' engineers the necessary information for deploying GaN devices in the existing and emerging applications, as well as provide references for the qualification evaluations of GaN power devices. The issues covered in this article include the dynamic instability of device parameters (e.g., ON-resistance, threshold voltage, and output capacitance), the device robustness in avalanche, overvoltage and short-circuit conditions, the device's switching reliability and lifetime, as well as the device's ruggedness under radiation and extreme (cryogenic and elevated) temperatures. Knowledge gaps and immediate research opportunities in the relevant fields are also discussed.

Index Terms—Cryogenic temperature, failure analysis, gallium nitride (GaN), high-electron mobility transistors (HEMTs), JFETs, MOSFETs, power electronics, power semiconductor devices, radiation, reliability, robustness, stability.

# I. INTRODUCTION

**P**OWER semiconductor devices are utilized as solid-state switches in power electronics' systems. To date, three

Manuscript received 18 October 2022; revised 26 January 2023; accepted 25 March 2023. Date of publication 11 April 2023; date of current version 19 May 2023. This work was supported by the Center for Power Electronics Systems Industry Consortium. Recommended for publication by Associate Editor S. Tian. (*Corresponding author: Yuhao Zhang.*)

Joseph Peter Kozak is with the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA 24060 USA, and also with Johns Hopkins University Applied Physics Laboratory, Laurel, MD 20723 USA (e-mail: jpkozak@vt.edu).

Ruizhe Zhang, Matthew Porter, Qihao Song, Jingcun Liu, Bixuan Wang, and Yuhao Zhang are with the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, VA 24060 USA (e-mail: rzzhang@vt.edu; maporter@vt.edu; qihao95@vt.edu; liujingcun0523@gmail.com; bixuanwang@vt.edu; yhzhang@vt.edu).

Rudy Wang is with the Milan Power Electronics Laboratory, Delta Electronics (Americas), Ltd., Durham, NC 27709 USA (e-mail: rudy.wang@deltaww.com).

Wataru Saito is with the Research Institute for Applied Mechanics, Kyushu University, Fukuoka 816-8580, Japan (e-mail: wataru3.saito@riam.kyushu-u.ac.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2023.3266365.

Digital Object Identifier 10.1109/TPEL.2023.3266365

power semiconductors have been commercialized, i.e., silicon (Si), silicon carbide (SiC), and gallium nitride (GaN) [1]. As compared with Si and SiC, GaN has superior properties, including the larger bandgap and higher critical electric field. Additionally, the AlGaN/GaN heterostructure forms two-dimensional electron gas (2DEG) with very high mobility, which can be further used to construct the high-electron mobility transistor (HEMT). GaN power HEMTs have been recently commercialized with the voltage classes from 15 to 900 V, and they are seeing rapid adoption in power supplies, data centers, Lidar systems, and fast chargers in consumer electronics [2], [3], [4], [5]. Benefitted from the smaller capacitances and charges, GaN power devices have enabled the lighter, smaller, and more efficient power electronics' systems. The market size of GaN power devices is projected to exceed \$1.26 billion by 2027 [5].

While GaN devices are currently being deployed in a variety of applications, there are still open questions to be answered regarding their stability, reliability, and robustness. This is largely because the architecture and physics of GaN HEMTs are very different from Si and SiC devices, such as MOSFETS, JFETS, and insultated gate bipolar transistors (IGBTs). GaN HEMT is a lateral device without p-n junction connected between source and drain, and its current is confined in a two-dimensional channel with a thickness of merely a few nanometers. Additionally, many GaN HEMTs are fabricated on foreign substrates, e.g., Si and sapphire, leading to a higher density of defects and traps as compared with Si and SiC devices built on native substrates.

Extensive efforts in academia and industry are ramping up to address the stability, reliability, and robustness issues facing GaN devices. For example, over 300 and 200 articles have been published on the topics of "GaN reliability" and "GaN power reliability" in the year 2021 according to the Web of Science database. In addition, while there has maintained a steady trend of publishing reliability studies on the R&D GaN devices demonstrated in research laboratories, an increase in publication on commercially available devices is observed. This trend converges with the industry's efforts on developing the standards for GaN qualification. For example, the "JEDEC" JC-70 committee has been providing insights into new test methodologies for GaN power devices [6].

In the previous literature, various aspects of GaN power HEMT reliability have been periodically surveyed [7], [8], [9], [10], [11], but most of these articles are from the device physics

Fig. 1. (a) Device electrical stressors in common stability, reliability, and robustness studies in comparison with the device's SOA. (b) Relationship between the stimulus stress and evaluation timescale for reliability and robustness tests. The scope of reliability tests, robustness tests, field test, and qualification test is illustrated.

perspective and are centric on R&D devices. The processing technology, material, and structure of R&D devices are usually immature compared with commercial devices, and some test conditions for reliability physics' studies are different from the device operations in practical converters. These situations make it difficult for power electronics' engineers to correlate the reliability physics and the nonideal behaviors of commercial GaN devices in converters. This challenge also hinders the further development of the health monitoring, prognosis, and protection systems.

This article attempts to address this gap by summarizing the current understanding on the stability, robustness, and reliability of GaN power devices, with an emphasis on reports of industrial devices. This article also tries to separate stability, robustness, and reliability issues, although in practice they often come interdependently with relatively ambiguous boundaries.

Fig. 1(a) illustrates the device electrical stressors in common stability, reliability, and robustness studies in comparison to the device's rating and safe-operating area (SOA). Stability usually refers to recoverable changes in device electrical characteristics as a result of the transient or sustained switching operation within the SOA [10]. Due to carrier trapping and detrapping within the device structure, the device characteristics can deviate from the static ones without leading to device failure.

Reliability and robustness often refer to nonrecoverable device degradation and failure. The stimulus (e.g., current or voltage) stress in reliability and robustness tests is usually near the SOA boundary and outside the SOA, respectively. Fig. 1(b) shows the other angle to differentiate reliability and robustness. Robustness tests often approach the destruction limits of device stimuli with a timescale much shorter than reliability tests. The timescale of robustness tests can be even down to a single cycle of switching, while that of reliability tests is usually at least hours up to weeks, months, and years.

The stability, reliability, and robustness overview for GaN power devices is motivated by three overarching questions.

- 1) What are additional power losses induced by the device parametric instability in conduction and switching?

- 2) What information do various device- and circuit-level reliability tests provide for practical applications?

- 3) What is the device's circuit-level resilience against surge energy, overvoltage, overcurrent, and their concurrence?

The answers of these questions ultimately help power electronics' engineers to achieve the desired efficiency in GaN converters and reserve proper margin during the design for desired lifetime of the GaN-based power product.

In addition to the conventional applications, GaN power devices are regarded as promising candidates for space, aeronautical, and defense applications. The devices for these applications are usually required to be rugged against radiation and at extremely high or low temperatures. Hence, the radiation and extreme temperature robustness have become increasingly important for power devices.

The rest of this article is organized as follows. Section II overviews the current commercial GaN power devices and common failure locations. Section III overviews the traditional qualification and reliability test results reported for GaN HEMTs, and Section IV surveys the extended reliability data from major GaN device vendors. Section V presents the stability issues of GaN HEMTs, including the dynamic ON-resistance, dynamic threshold voltage, and output capacitance losses, which are all critical to power applications particularly at high frequencies. Section VI details the robustness of GaN HEMTs in out-of-SOA conditions, such as overvoltage, short circuit (SC), and surge energy. Section VII discusses the research exploring the switching reliability and lifetime of GaN devices in converters and under mission profiles. While GaN HEMTs are discussed in prior sections, Section VIII introduces the robustness of the emerging vertical GaN devices that are being commercialized in the industry. Sections IX and X discuss the radiation and extreme temperature ruggedness of GaN devices, respectively. Section XI lists some immediate research needs. Finally, Section XII concludes this article.

Note that the reliability studies of nonindustrial emerging GaN devices are not covered in this article. Some multidimensional GaN devices [1], such as FinFETs [12], [13] and multichannel HEMTs [14], have demonstrated breakthrough performance in ultralow voltage classes down to a few volts [15], [16] and in higher voltage up to 10 kV [17], [18]. While reliability studies of these devices are ramping up [19], [20], [21], they are still at a relatively early stage of development.

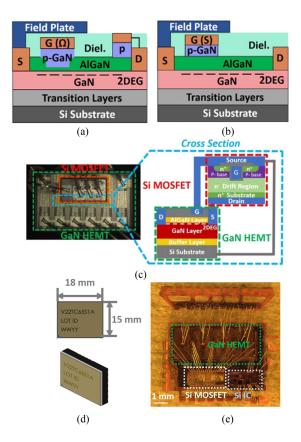

Fig. 2. Schematic of (a) GaN SP-HEMT and (b) GaN HD-GIT. (c) Photograph and schematic of a decapsulated cascode GaN HEMT. (d) Photograph of a packaged direct-drive GaN HEMT. (e) Photograph of a decapsulated direct-drive GaN HEMT from another vendor.

# II. CURRENT GAN DEVICES AND USUAL FAILURE LOCATIONS

# A. Current GaN Power Devices

Four types of device architectures are primarily employed in commercially available GaN products. Two of these include the hybrid-drain gate injection transistor (HD-GIT) and the Schottky p-gate HEMT (SP-HEMT). These technologies are discrete devices and utilize a p-GaN layer in the gate stack to realize the enhancement-mode (E-mode) operation. Their schematics are shown in Fig. 2(a) and (b).

The other two architectures can be considered composite devices where the cascode structure and direct-drive modules utilize multiple semiconductor dies of which the GaN HEMT is usually the depletion mode (D-mode). Fig. 2(c) shows a photograph of a decapsulated cascode HEMT and its schematics [22], [23]. Fig. 2(d) and (e) show the photographs of direct-drive GaN device/module from two different vendors [24].

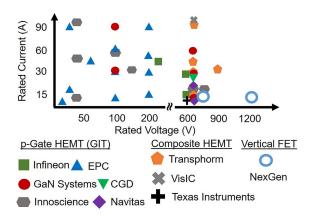

Fig. 3 depicts the current and voltage ratings of available commercial GaN devices from various vendors. The precommercial vertical GaN field effect transistor (FET) is also included and will be elaborated in Section VIII.

To be cost competitive, the majority of commercial GaN HEMTs are fabricated on Si substrates. Above this substrate includes a transition layer and then the primary GaN buffer layer. An AlGaN layer is deposited above the GaN buffer layer,

Fig. 3. Current and voltage ratings of commercial and precommercial GaN devices from various vendors.

and it is the interface between the AlGaN and GaN layers that creates the primary channel to conduct current. The lattice mismatch of these two layers creates a piezoelectric effect, which creates a 2DEG channel. The drain, gate, and source terminals are oriented laterally above the AlGaN layer. The p-GaN in the gate stack is key to realization of E-mode operation. This E-mode operation is the preferred choice for power electronics' applications.

The distinction between HD-GIT [see Fig. 2(a)] and SP-HEMT [see Fig. 2(b)] is mainly located in the gate and drain region. The gate metal forms an Ohmic contact to p-GaN in the HD-GIT and a Schottky contact in the SP-HEMT. The AlGaN layer in the HD-GIT is usually recessed, enabling a closer proximity of p-GaN to the 2DEG. The Ohmic contact and AlGaN recess in the HD-GIT favors hole injection into the 2DEG channel, enabling the conductivity modulation. In addition, the HD-GIT includes a p-GaN region connected to the drain, which enables the hole injection into the channel and buffer to alleviate the electron trapping. By contrast, the current conduction in the SP-HEMT only relies on electrons, and minimal holes are injected into the device channel and buffer regions.

In the cascode and direct-drive devices, the traditional high-voltage D-mode GaN devices are oriented with a lower voltage E-mode Si power MOSFET. Through the connection of the two devices [23], [25], a high-voltage E-mode device is created for the cascode device.

The direct-drive devices advance this principle further by incorporating integrated circuit (IC). In this way, a gate driver can be implemented with the power semiconductor to optimize the gate-loop performance and ease the requirements of additional components. Some devices also include sensing and protection ICs for added capabilities.

Overall, these two topologies allow for the use of D-mode HEMT, which usually has a simpler gate stack in comparison to the HD-GIT and SP-HEMT [26]. However, the inclusion of multiple chips in the package brings additional driving challenges as well as the introduction of new failure and instability mechanisms that could be triggered and coupled between the multiple chips [22]. These challenges will be elaborated in the later sections.

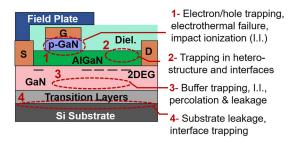

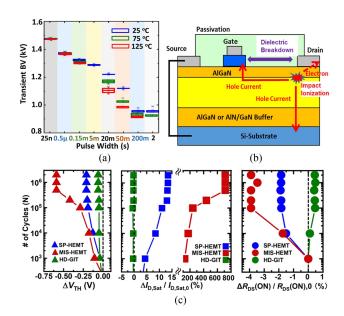

Fig. 4. Illustration of typical trapping locations and other physical processes that can lead to stability, reliability, and robustness issues.

#### B. Usual Failure Locations

Here, we list some common failure modes and locations in GaN HEMTs to provide an abstract, physical reference for understanding results in the following sections. In Si and SiC MOSFETs, there are known issues within the gate-oxide layer due to various stresses from the gate and drain biases [27], [28]. Additionally, the p-n junction of the MOSFET structure has shown various bipolar stability issues [29].

Differently, many reliability issues of GaN HEMTs are predominantly imposed by carrier trapping effects at various interfaces and layers within the device, as illustrated in Fig. 4. Severe trapping can greatly affect the local electric field and current density, thereby impacting the device ON-resistance, breakdown voltage, and capacitances. In addition to trapping, some other physical processes, such as impact ionization, electrothermal failure, and percolation path creation, can also lead to device failure under different stresses. For example, the carriers generated in impact ionization, if not removed efficiently, can induce the destructive device breakdown [30]. In the GaN HEMT, these processes usually occur at the gate region, AlGaN/dielectric interface, GaN buffer region, transitional layers, and Si substrates. In composite-type GaN devices, the failure locations can be more diverse, e.g., in the multichip interconnect or in Si chips.

#### III. TRADITIONAL QUALIFICATION AND RELIABILITY TEST

As illustrated in Fig. 1(b), traditional accelerated lifetime and reliability tests are designed to help in the qualification of packaged devices for industrial applications by evaluating two primary focuses stressing either the semiconductor-oriented or the packaging-oriented failure mechanisms. While there are international entities that have produced standards for testing semiconductors (e.g., JEDEC, IEC, AEC-Q, MIL-STD, etc.), many qualifications have a foundation from Si technologies. It is now largely an industrial consensus that these standard qualifications (e.g., JEDEC qualification) for GaN devices are necessary but not sufficient and must be followed up by other comprehensive tests. A few industry groups, such as the JEDEC JC-70 Committee [6] and the joint ZVEI European Center for Power Electronics (ECPE) group [31], are actively working to evaluate and update these standards, and provide guidelines for future device evaluations focused on the stresses that GaN devices would experience over the traditional Si transistors.

TABLE I EXEMPLAR LIST OF THE AEC Q101 QUALIFICATION TESTS FOR A 650 V,  $50~\text{m}\Omega$  Gan Cascode HEMT

| Test                                     | Symbol     | Conditions                                          |

|------------------------------------------|------------|-----------------------------------------------------|

| High-temperature reverse bias            | HTRB       | $T_{\rm J}$ = 150°C, $V_{\rm DS}$ = 650 V, 1000 hrs |

| Highly accelerated temp and humidity     | HAST       | 130 °C, 85% RH, 33.3 PSI,<br>Bias = 100 V, 96 hrs   |

| Temperature cycle                        | TC         | –66/150 °C, 2 Cycles/hr,<br>1000 Cycles             |

| Temperature cycling hot tests            | TCHT       | 125 °C Test after TC                                |

| Wire-bond integrity                      | WBG        | 150 °C, 500 hrs                                     |

| Power cycle                              | PC         | 25/125 °C, ΔT=100 °C,<br>15,000 Cycles              |

| High-temperature storage life            | HTSL       | 150 °C, 1000 hrs                                    |

| High-temperature gate bias (Cascode)     | HTGB       | 150 °C, 1000 hrs, $V_{GSS}$ = 18 V                  |

| High-temperature gate bias (HEMT only)   | HTGB<br>#2 | $150^{\circ}$ C, $1000$ hrs, $V_{GSS} = -35$ V      |

| High-humidity high-<br>temp reverse bias | H3TRB      | 85 °C, 85% RH, 1000 hrs, 100 V                      |

| Unbiased accelerated stress test         | UHAST      | 130 °C, 85% RH, 96 hrs                              |

| Destructive physical analysis            | DPA        | Post TC and HAST                                    |

Automotive qualification for GaN devices has attracted great traction recently. Traditional automotive qualification routines are usually based on the AEC-Q100/Q101/Q200 family for Si devices. Table I illustrates one of the first reported automotive qualifications for a 650 V, 50 m $\Omega$  cascode GaN HEMT based on the AEC-Q101 standard [32]. The AEC-Q101 qualification for other GaN devices (e.g., SP-HEMT) comprises similar tests except for using a positive gate bias (e.g., 6 V) in the relevant gate tests.

The ECPE recently released a comprehensive automotive qualification standard, namely LV324, expanded upon the AEC standard [31]. The standard comprises a large number of tests categorized into three groups, the qualification characterization tests (QC), qualification environment tests (QE), and qualification lifetime tests (QL). The QC consists of tests on the device's parasitic stray inductance, thermal resistance, and SC robustness. The QE tests involve thermal shock, vibration, and mechanical shock. The composition of the QL tests is similar to that shown in Table I.

While good qualification data have been released by many GaN device vendors, it would be still very useful for power electronics' engineers to know possible GaN device degradation under these qualification tests, particularly for the evaluation of future devices. Hence, we briefly summarize the reported GaN device degradation under several representative qualification and reliability tests, including the static dc-bias tests, such as high-temperature reverse bias (HTRB) and high-temperature gate bias (HTGB), as well as switching tests, such as power cycling.

# A. High-Temperature Reverse Bias

HTRB experiments used for device qualification usually apply a stress at 80% of the device rating (for some applications, such as the automotive, up to 100% of the rating) [33]. These qualifying experiments can take thousands of hours [34], [35], [36]. Under HTRB stress, a positive shift has been reported in the ON-resistance ( $R_{\rm DS,ON}$ ) and threshold voltage ( $V_{\rm TH}$ ), but the changes do not reach a failed state [37], [38], [39]. In more accelerated HTRB experiments (where the drain voltage is higher than the rated voltage), the  $V_{\rm TH}$  instability in some early GaN HEMTs has shown up to a 50% increase, which is above the notional 20% shift failure boundary but recoverable [40].

Determining the voltage stresses in the accelerated HTRB experiments is a challenge for GaN HEMTs because of their dynamic breakdown voltage [41]; this is in comparison with MOSFETs that have an inherently constant avalanche breakdown voltage [27], [42]. Additionally, when MOSFETs are stressed in HTRB experiments, they show an increase in gate-leakage current ( $I_{\rm GSS}$ ) but some GaN HEMTs show a decrease in  $I_{\rm GSS}$  and drain-leakage currents ( $I_{\rm DSS}$ ) [40], [43]. These shifts in electrical parameters are all related to electron trapping and detrapping [34], [35], [40].

# B. High-Temperature Gate Bias

HTGB experiments apply a high static bias onto the gate terminal of the GaN device. Similar tests with a static bias and step-stress processes have been used to determine the gate voltage rating of GaN HEMTs [37], [44], [45], [46], [47], which will be further discussed in Section VII.

HTGB experiments have also shown to cause shifting in  $V_{\rm TH}$  and  $R_{\rm DS,ON}$  [37], [43], [44] due to trapped charges in the gate stack. The type of contact formed on p-GaN, either Schottky or Ohmic, would impact these drifts [48]. The Ohmic contact is capable of more efficient hole injection in comparison with the Schottky contact, which would minimize the  $V_{\rm TH}$  shift [37].

# C. Power Cycling

Power cycling experiments are primarily used to stress the packaging of a commercial device and the interface between the device and package. The stress is created through the repeated, (self) heating of the device with ON-state current causing strain in the mechanical layers due to the differences in the coefficient of thermal expansion mismatch [49], [50], [51].

The p-gate GaN HEMTs have been reported to show  $V_{\rm TH}$  and  $R_{\rm DS,ON}$  increase in power cycling [49], [51]. Depending on the magnitude of the temperature swing,  $I_{\rm DSS}$  has also shown to increase as well [49], [52]. While solder fatigue has been reported and does impact the increase in  $R_{\rm DS,ON}$ , the changes in  $V_{\rm TH}$  and  $I_{\rm DSS}$  provide evidence that trapping effects cause further degradation in device [49].

Composite-type devices have a greater susceptibility to degradation and failure within the mechanical interconnections from power cycling stresses. Both Xu et al. [49] and Franke et al. [50] have reported that the cascode devices show an increase in  $R_{\rm DS,ON}$ . The  $V_{\rm TH}$ , however, was not identified as a sensitive

precursor parameter for cascode devices under power cycling experiments [49]. The final failure mechanism was attributed to bond-wire lift-off between the Si MOSFET and GaN HEMT [50].

#### IV. EXTENDED RELIABILITY DATA BY DEVICE VENDORS

While all GaN power devices from major vendors have passed the JEDEC and AEC-Q standards, additional reports have been published by these vendors to provide data regarding the device stability, reliability, and robustness beyond the Si qualification standards. Table II summarizes these extended test data from major GaN device vendors, including EPC, Infineon, GaN Systems, and Transphorm [53], [54], [55], [56].

As illustrated in the table, the common extended reliability data from various vendors mainly address several aspects:

- 1) dynamic  $R_{DS,ON}$  issue, which is related to device parametric stability and conduction loss in applications;

- 2) the accelerated lifetime extraction under various stimuli, including the drain-to-source bias  $(V_{\rm DS})$ , gate-to-source bias  $(V_{\rm GS})$ , and temperature;

- the accelerated lifetime testing under various mission profiles mimicking the device operations in some representative applications.

Examples of such switching stress include the hard-switched boost converter, double-pulse-based setup, and soft-switched converters. In some context, such test is named the high-temperature operating life (HTOL) test, and the test circuit topologies include a boost converter [32] and the half-bridge converters with *RC* load or *RL* load [57].

The extensive test data manifest the insufficient qualification of GaN HEMTs using the conventional Si standards. However, one can find that the data presented by different vendors are often obtained from different methods, and most of the derived reliability models are vendor specific. For example, the  $V_{\rm DS}$  overvoltage robustness is characterized by both dc stress and pulsed voltage by Infineon and only by dc stress by other vendors. Another example is the large variety of circuit topologies used to extract the switching stress lifetime by various vendors. Finally, critical device robustness, such as the SC capability, is only reported by one vendor, and some other parameters, such as avalanche (surge-energy) capability, are not reported by any vendor

To address these gaps, many studies have been performed by researchers and engineers in the academia and industry to do the following:

- 1) explore and compare various methods to characterize the stability, reliability, and robustness of GaN HEMTs;

- identify the common or distinct behaviors that are correlated to characteristic device structures instead of being vendor specific;

- generalize unified models for device dynamic parameters and lifetimes for various GaN HEMTs.

While not all of these gaps have been fully addressed, the summary of current understandings provides useful information for device users. The high-level explanation of the relevant physical mechanisms could help device users understand the potential problems of GaN devices and how they differ from

| Test                            | Vendor         | Test method                                  | Behavior                                                    | Mechanism                   | Major Results Reported                                                                                                            |

|---------------------------------|----------------|----------------------------------------------|-------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                 | EPC            |                                              | dynamic $R_{ m DS,ON}$<br>higher than static $R_{ m DS,ON}$ |                             | Charge trapping and $R_{\rm DS,ON}$ model established with factors of $V_{\rm DS}$ , $I_{\rm D}$ , $f_{\rm sw}$ , and $T_{\rm J}$ |

| Dynamic R <sub>DS,ON</sub> Test | Infineon       | Hard switch                                  |                                                             | Hot-electron trapping       | Minimal dynamic $R_{\rm DS,ON}$ up to 600 V at 10 MHz                                                                             |

| 1031                            | GaN<br>Systems |                                              |                                                             |                             | Dynamic $R_{DS,ON}$ impacted more by $T_J$ than by the trapping                                                                   |

|                                 | EPC            | DC stress                                    | serious $R_{\rm DS,ON}$ shift                               | Hot-electron trapping       | Nonmonotonic relationship with $T_{\rm J}$ . 1 ppm over 10 Years at rated $V_{\rm DS}$ at 150 $^{\circ}{\rm C}$                   |

| Drain<br>Acceleration           |                | DC stress                                    | catastrophic                                                | TDDB-like failure behavior  | 100 ppm for 15 Years at 480 V $V_{\rm DS}$ at 125 °C                                                                              |

| Lifetime                        | Infineon       | Pulsed voltage                               | breakdown                                                   | Electrical breakdown        | Transient voltage ratings identified to include in the datasheet                                                                  |

|                                 | Transphorm     | DC stress                                    | catastrophic<br>breakdown                                   | Dielectric breakdown        | >>20 Years lifetime at 650 V $V_{\rm DS}$ , 175 °C $T_{\rm J}$ .                                                                  |

| Gate Acceleration               | EPC            | DC stress                                    | catastrophic<br>failure                                     | Failure in Schottky contact | Failure insensitive to $T_{\rm J}$ , 1 ppm in 10 Years at recommended $V_{\rm GS}$                                                |

| Lifetime                        | GaN<br>Systems | DC stress                                    |                                                             |                             | 100 ppm in $> 10^{10}$ hrs at recommended $V_{\rm GS}$                                                                            |

|                                 | Infineon       | Hard-switch<br>boost                         | N/A                                                         | N/A                         | Lifetime model with the factors of $I_{\rm D},~V_{\rm DS}$ and $f_{\rm sw}$                                                       |

| Switching Stress<br>Lifetime    | GaN<br>Systems | LLC/PFC converter                            | catastrophic                                                | N/A                         | lifetime > 3 million Years for data center LLC and PFC applications                                                               |

|                                 | Transphorm     | Double-pulse<br>based setup                  | failure                                                     | N/A                         | Lifetime model with the acceleration factor $V_{\mathrm{DS}}$                                                                     |

| SC                              | EPC            | Hard-switch<br>fault and fault<br>under load | catastrophic<br>failure                                     | Thermal runaway             | Over 10 $\mu s$ SC withstanding time at 60 V $V_{DS}$ in both conditions                                                          |

| HTOL                            | Transphorm     | Hard-switch<br>boost                         | N/A                                                         | N/A                         | No degradation after 3000 HRs running at $T_{\rm J}$ of 175 °C and frequency of 300 kHz                                           |

TABLE II

SUMMARY OF EXTENDED RELIABILITY TEST METHODS AND RESULTS FROM MAJOR GAN DEVICE VENDORS

Si and SiC devices. These summaries and explanations will be provided in the next few sections.

# V. STABILITY IN SWITCHING

Parametric instability in GaN HEMTs is usually associated with the trapping behavior (trapping and detrapping). The accurate measurement of parametric shifts, particularly in high-frequency switching, is very challenging. This is because the occupation probability of traps depends on its electrical history and the trapping behavior usually spans the time constants over many orders of magnitude [10]. Here, we first scrutinize various measurement methods [58], [59] and clarify the time constant range associated with each method. This allows us to understand how the results from these measurements correlate to device switching operation in practical converters.

Generally, three types of stability and reliability tests have been widely used for power devices, i.e., the dc stress test, pulse I-V test, and circuit test. Table III summarizes the key features of these tests. The dc stress test usually characterizes the relatively long-term parametric shifts after an OFF-state dc stress. It cannot capture the parametric shifts that recover within the poststress measurement time (usually at least  $\sim 10$  s). Therefore, the measured shifts are not representative of those present in transient switching. The pulse I-V test can probe the dynamic parametric shifts in a short time (down to 1  $\mu$ s) right after the switching stress. However, the pulse I-V condition is still different from converters, as it is based on the square wave with a resistive load and has a limited dv/dt.

TABLE III

COMPARISON OF THREE TEST APPROACHES THAT ARE COMMONLY USED FOR

EVALUATING THE STABILITY AND RELIABILITY OF POWER DEVICES

| Method                                 | DC stress test                                                     | Pulse I–V test                                                                             | Circuit test                                                                                           |

|----------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Stress Time                            | seconds to hours                                                   | 1 μs–100 ms<br>[PW(1–D)/D]*                                                                | 10 ns–10 μs                                                                                            |

| Stress Type                            | DC; OFF-state                                                      | Square-wave<br>switching<br>(resistive load);<br>OFF-state                                 | Inductive<br>switching; ON-<br>and OFF- state                                                          |

| Measured<br>Parameter                  | $R_{ m ON},V_{ m TH},I_{ m GSS},\ I_{ m DSS},C$                    | $R_{ m ON},V_{ m TH},I_{ m GSS},\ I_{ m DSS},C$                                            | $R_{\mathrm{ON}}, C(V_{\mathrm{TH}})$                                                                  |

| Time of<br>Measurement                 | > 10 s                                                             | 1 μs–100 ms<br>(PW)                                                                        | 10 ns–1 μs                                                                                             |

| Key<br>information for<br>applications | parametric shifts<br>that cannot<br>recover within<br>seconds      | dynamic<br>parametric shifts<br>in square-wave<br>pulses                                   | parametric shifts<br>under<br>application-use<br>conditions                                            |

| Note and limitations                   | used to monitor<br>long term and<br>permanent<br>parametric shifts | usually resistive<br>loads; pulse rise<br>time > 100 ns for<br>high bias, limited<br>dv/dt | distinction may<br>exist in single<br>pulse and steady<br>state; in situ<br>measurement<br>challenging |

<sup>\*</sup>PW: pulsewidth; D: duty cycle.

Circuit tests allow for characterization of device's parametric shifts under the application-use conditions. Additionally, benefitted from the small time constant of the stress that can be implemented in circuits, the switching stress of interest is no longer limited to the OFF-state stress but can also

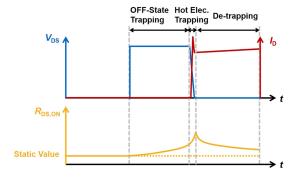

Fig. 5. Schematic of  $R_{\rm DS,ON}$  variation during a switching event of GaN HEMTs due to trapping and detrapping effects.

accommodate the ON-state stresses (e.g., SC and gate overvoltage). The challenges in circuit tests are on the in situ measurement of the parametric shift of interest with a minimal disturbance on the converter operation. Finally, one should be careful about the parametric shifts evaluated in the single-event and steady-state switching, which could be different due to the distinction in trapping states. This will be further explained in the evaluation of  $D-R_{DS,ON}$  and dynamic breakdown voltage.

In the remaining part of this section, we will present three major parametric stability issues in GaN HEMTs during their normal switching operations (i.e., within the SOA).

# A. Dynamic ON-Resistance

Dynamic  $R_{\rm DS,ON}$  (D- $R_{\rm DS,ON}$ ) is a well-known issue in various types of GaN HEMTs, where the  $R_{\rm DS,ON}$  is higher than its measured dc value after high blocking voltage stress. D- $R_{\rm DS,ON}$  leads to undesirable increases in the device conduction loss and junction temperature, yet it is not commonly specified in datasheets. This D- $R_{\rm DS,ON}$  poses serious challenges in designing GaN-based power converters, especially for high-frequency applications. Over the past decade, extensive studies have been devoted toward understanding and addressing different aspects of the D- $R_{\rm DS,ON}$  phenomenon, including its physical origin, dependency factors, characterization method, etc.

1) Physical Origin: D- $R_{\rm DS,ON}$  roots from the trapping effect in various possible regions of the GaN HEMT structure, as shown in Fig. 4. Leakage current electrons injected under high drain bias [60] and hot electrons generated during switching transitions due to the overlap of high voltage and high current [61] could cause charge trapping in the buffer layer, GaN channel and gate region, as well as near the surface and/or in the dielectric. Each of these can decrease the 2DEG conductivity and increases  $R_{\rm DS,ON}$ . The physical mechanisms have been thoroughly reviewed in [62] and will not be elaborated in this article. At the device level, various technologies, such as surface passivation optimization [63], elaborately designed GaN buffer [64], and optimal field-plate structure [65], have been proposed to reduce the trapping effects and eliminate the D- $R_{\rm DS,ON}$  issue.

Fig. 5 illustrates the typical  $R_{\rm DS,ON}$  variation during a switching event of GaN HEMTs. The increase in D- $R_{\rm DS,ON}$  (electron-trapping effect) mainly exists in two stages: the first one is

induced in the OFF-state, and the second is related to the hard turn-ON process. In the ON-state, detrapping of these electrons allows the  $R_{\rm DS,ON}$  to gradually settle back to its static value. Note that the soft turn-ON process is not expected to induce significant D- $R_{\rm DS,ON}$  in most GaN HEMTs.

As the review [62] published in 2019, many recent studies on SP-HEMTs and HD-GITs have reported consistently new understandings on the D- $R_{\rm DS,ON}$  issue. First, the D- $R_{\rm DS,ON}$  is more strongly affected by the hard turn-ON process than the OFF-state [66], [67], [68], [69]; Second, the OFF-state stress primarily induces electron trapping in the buffer, while the hard turn-ON stress induces electron trapping in both the buffer and the interface between AlGaN and passivation layer [67], [70]. Some studies report the interface/surface trapping to dominate in the hard turn-ON process while observing the impact of buffer region design [66], [67] and drain field-plate design [71] on surface trapping. Studies have also shown that the traps relevant to the hard turn-ON process possess a broadly distributed but relatively shallow energy level [72], [73].

2) Dependency Factors: As D- $R_{\rm DS,ON}$  is caused by the device switching transition, numerous research articles have reported the influence of varying operating conditions in power converters on the D- $R_{\rm DS,ON}$ .

The number of trapped electrons depends very much on the blocking voltage, and a nonmonotonic relation between D- $R_{\rm DS,ON}$  and OFF-state and drain-to-source voltage ( $V_{\rm DS,OFF}$ ) has been identified in [74], [75], and [76]. It has been shown that D- $R_{\rm DS,ON}$  increases with  $V_{\rm DS,OFF}$  until it reaches a maximum at typically 100–300 V (for a ~600-V rated device). However, the D- $R_{\rm DS,ON}$  recovers to smaller values at higher  $V_{\rm DS,OFF}$ due to partial neutralization of buffer traps [74]. Additionally, the load current  $(I_L)$  affects the hot-electron acceleration, and thus trapping efficacy, particularly in the hard turn-ON process. Therefore, a higher D- $R_{DS,ON}$  is observed as  $I_L$  increases [77], [78]. Switching speed (and duration) determines the quantity of trapped hot electrons, so a larger gate resistance could induce the more serious D- $R_{\rm DS,ON}$  issue [79]. Higher gate current/gate voltage [80] can facilitate a faster detrapping process during the ON-state and contributes to a smaller D- $R_{DS,ON}$ .

As the time constant of trapping behavior can span from nanoseconds to seconds [81], [82], D- $R_{\rm DS,ON}$  is dependent on the switching frequency and duty cycle [83]. The probability of electron trapping and detrapping is also related to junction temperature ( $T_J$ ). Inconsistent reports are present for various devices that the D- $R_{\rm DS,ON}$  either increase [84] or decrease [85] at higher  $T_J$  or show more complex dependences [86]. For example, the D- $R_{\rm DS,ON}$  of HD-GITs is found to increase with  $T_J$  at low  $V_{\rm DS,OFF}$  but decrease with  $T_J$  at high  $V_{\rm DS,OFF}$ , which is related to the effectiveness of hole injection in HD-GITs [86]. The dependence between D- $R_{\rm DS,ON}$  on  $T_J$  may be device specific and impacted by  $V_{\rm DS,OFF}$  and switching schemes.

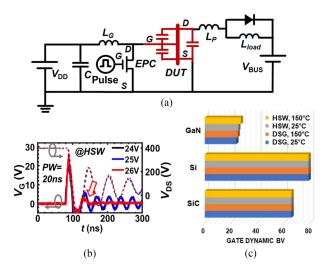

Finally, the D- $R_{\rm DS,ON}$  differs in hard switching (HSW) and soft switching [87], [88], [89], but its dependency could be device specific [90]. Soft switching leads to a lower D- $R_{\rm DS,ON}$  in SP-HEMTs [91] by eliminating the impact by hot-electron effects; in HD-GITs, injected holes from the drain p-GaN layer

| Method      | Type of device | Circuit topology   | Type of load | Note and limitations                                                                                                            | Reference                 |

|-------------|----------------|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Pulsed I-V  | On-wafer       | /                  | Resistive    | Nonrealistic switching locus and slew rate;<br>limited frequency; pulse overlap is changed<br>to accommodate HSW/soft switching | [60], [82]                |

| DPT         | Packaged       | Half-bridge        | Inductive    | Usually does not specify the stress time before the first pulse; may underestimate                                              | [79], [86], [87],<br>[95] |

|             | C              | Full-bridge        |              | the actual D- $R_{\rm DS,ON}$ in repetitive switching                                                                           | [85]                      |

|             | Packaged       | Half-bridge        |              |                                                                                                                                 | [78], [90], [96]          |

|             |                | Buck               | Inductive    | Working on packaged devices; may add                                                                                            | [83], [97]                |

| Continuous  | rackageu       | Resonant converter |              | cycle (packaging) time for R&D devices                                                                                          | [85]                      |

| Switching _ |                | Resonant inverter  | Resistive    | _                                                                                                                               | [98]                      |

|             | On-wafer       | Boost              | Inductive    | Need careful parasitic control; very hard to<br>reach high switching speed and high<br>voltage/current at wafer level           | [66], [99]                |

TABLE IV Comparison of Characterization Methods Commonly Used for Evaluating D- $R_{

m DS,ON}$  of GaN Power HEMTs

during HSW effectively release the trapped electrons, so soft switching may even result in a higher D- $R_{\rm DS,ON}$  [90].

3) Characterization Method and Results: Despite extensive efforts in D- $R_{DS,ON}$  characterizations, large discrepancies have been reported in the literature from a minimal increase to a ten times higher gain over static  $R_{\rm ON}$  [92], even for commercial devices. It was recently pointed out that this inconsistency largely originates from the characterization methods [92]. Table IV summarizes the key aspects of three most commonly used D-R<sub>DS,ON</sub> characterization methods, including pulsed I-V test, double-pulse test (DPT), and steady-state continuousswitching test. By employing source measure units to modulate the voltage bias at multiple device terminals, the pulse I-V test is usually performed at wafer level with resistive load and used in many trapping physics' studies [82], [93], [94]. The overlap of current and voltage could be changed to simulate HSW/soft switching, but it cannot mimic the switching locus and slew rate (e.g., dv/dt) in real applications.

The classic DPT method, as recommended by the JEDEC standard [95], has been used in various circuit topologies with inductive load [79], [85], [86], [87], [95]. However, DPT could miscalculate the device  $D-R_{\rm DS,ON}$  in continuous-switching power converters [96] because it ignores the accumulation effects in repetitive switching cycles. In addition, DPT usually does not specify the OFF-state stress time before the first pulse, which could lead to uncertainties in  $D-R_{\rm DS,ON}$ .

More recently, state-of-the-art  $D-R_{DS,ON}$  test design has been focusing on the continuous-switching method where the GaN devices are switched to the steady state in power converters, including half-bridge topology [78], [90], [96], buck converter [83], [97], resonant converter [85], [98], etc. With the realistic application profile, steady-state continuous-switching test is the best practice to perform a  $D-R_{DS,ON}$  characterization. It is noteworthy that  $D-R_{DS,ON}$  in continuous-switching converter (boost converter circuit [99]) has been performed at the wafer level, which could significantly shorten the R&D process of GaN HEMTs. The key to achieve this ON-wafer dynamic characterization is the accurate control of parasitics in the whole system, e.g., probe tip, connectors, and cables, which allows for reaching high switching speed and switching voltage/current.

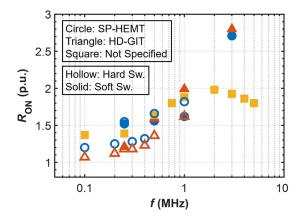

Fig. 6. Literature values of normalized D- $R_{\rm DS,ON}$  to the static value of commercial GaN HEMTs under steady-state switching conditions.

Fig. 6 and Table V show the normalized D- $R_{\rm DS,ON}$  measurement results of commercial GaN HEMTs under the steady-state switching conditions, characterized from hundreds of kilohertz up to several megahertz [80], [90], [97], [100]. Target devices include both SP-HEMTs and HD-GITs, whereas measurements of composite devices are still lacking. These devices were tested at nominal voltage levels ( $\sim$ 67% voltage rating, e.g., 400 V for 600/650-V devices) and nominal current level (~50% current rating, e.g., 8 A for 15-A devices). With a steady-state switching measurement protocol, the worst-case D- $R_{\rm DS,ON}$  of commercial GaN HEMTs was found to be less than three times higher than the static value. For the same device, D- $R_{\rm DS,ON}$  generally increases as the switching frequency goes up. Below 1 MHz, the D- $R_{DS,ON}$  among all tested devices was within twice the static value, regardless of switching mode (hard or soft). In multi-MHz switching, D- $R_{DS,ON}$  of certain devices presented a saturation with frequency (e.g., 2 MHz in Fig. 6). This could be a result that the time constant of the combination of trapping and detrapping effects is exceeded [97].

From the application viewpoint, the D- $R_{\rm DS,ON}$  characterized in application-use conditions provide valuable references for converter design and performance evaluation. The efficiency of GaN-based converters is directly affected by D- $R_{\rm DS,ON}$  due to the increased conduction loss. Thermal management needs

| TABLE V                                                       |

|---------------------------------------------------------------|

| SUMMARY OF THE NORMALIZED D-RDS.ON TEST RESULTS OF COMMERCIAL |

| GAN HEMTS UNDER STEADY-STATE SWITCHING CONDITIONS             |

| Device<br>Technolo | Device<br>Rating | Tes                 | Normaliz<br>ed D- |                |                              |

|--------------------|------------------|---------------------|-------------------|----------------|------------------------------|

| gy                 | -                | Voltage/<br>Current | Type of<br>Sw.    | Freq.<br>(kHz) | R <sub>DS,ON</sub><br>Result |

| SP-                | 650 V/           | 400 V/              | Hard              | 250            | 1.55                         |

| HEMT               | 30 A [90]        | 15 A                |                   | 500            | 1.66                         |

|                    |                  |                     |                   | 1000           | 1.82                         |

|                    |                  | 400 V/              | Soft              | 250            | 1.52                         |

|                    |                  | 10 A                |                   | 500            | 1.56                         |

|                    |                  |                     |                   | 1000           | 1.62                         |

|                    | 650 V/           | 400 V/              | Hard              | 100            | 1.2                          |

|                    | 15 A [80]        | 8 A                 |                   | 200            | 1.25                         |

|                    |                  |                     |                   | 300            | 1.28                         |

|                    |                  |                     |                   | 400            | 1.32                         |

|                    | 650 V/           | 400 V*              | Soft              | 3000           | 2.71                         |

|                    | 15 A [100]       |                     |                   |                |                              |

| GIT                | 600 V/           | 400 V/              | Hard              | 250            | 1.18                         |

|                    | 13 A [90]        | 7.5 A               |                   | 500            | 1.36                         |

|                    |                  |                     |                   | 1000           | 1.62                         |

|                    |                  | 400 V/              | Soft              | 250            | 1.21                         |

|                    |                  | 5 A                 |                   | 500            | 1.59                         |

|                    |                  |                     |                   | 1000           | 1.99                         |

|                    | 600 V/           | 400 V/              | Hard              | 100            | 1.07                         |

|                    | 13 A [80]        | 8 A                 |                   | 200            | 1.12                         |

|                    |                  |                     |                   | 300            | 1.18                         |

|                    |                  |                     |                   | 400            | 1.23                         |

|                    | 600 V/           | 400 V*              | Soft              | 3000           | 2.8                          |

|                    | 15 A [100]       |                     |                   |                |                              |

| Not                | <200 V,          | <135 V/             | Soft              | 100            | 1.37                         |

| specified          | current          | 1 A                 |                   | 250            | 1.39                         |

|                    | rating           |                     |                   | 500            | 1.64                         |

|                    | hidden           |                     |                   | 750            | 1.8                          |

|                    | [97]             |                     |                   | 1000           | 1.88                         |

|                    |                  |                     |                   | 2000           | 1.98                         |

|                    |                  |                     |                   | 3000           | 1.93                         |

|                    |                  |                     |                   | 4000           | 1.86                         |

|                    |                  |                     |                   | 5000           | 1.8                          |

<sup>\*</sup>Current stress not specified

careful consideration, and the device SOA may be shrunk (where the upper left boundary is limited by  $R_{\rm DS,ON}$ ). The possibly higher  $T_J$  and reduced SOA of GaN HEMTs could further affect the lifetime projection of GaN-based power converter.

# B. Output Capacitance Loss

In addition to  $R_{\rm DS,ON}$ , GaN HEMTs produce the losses generated from the output capacitance ( $C_{\rm OSS}$ ). The  $C_{\rm OSS}$  loss is generated when the equivalent output capacitance of the OFF-state power device is subsequently charged and discharged; this loss is equal to zero in an ideal capacitor. In GaN HEMTs, output charge versus  $V_{\rm DS}$  characteristics show hysteresis in large signal, dynamic double sweep, producing power loss in a cycle of charging and discharging. This  $C_{\rm OSS}$  loss issue first gained attention in Si superjunction devices [101], [102] and recently in GaN HEMTs.

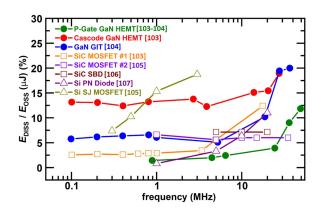

Fig. 7 shows a comprehensive comparison of  $C_{\rm OSS}$  losses reported in various types of GaN HEMTs as compared with some Si and SiC devices [103], [104], [105], [106], [107]. GaN HEMTs are experiencing considerable  $C_{\rm OSS}$  losses, e.g.,

Fig. 7. Comparison of the ratios of the reported  $C_{\rm OSS}$  loss over the total  $C_{\rm OSS}$  stored energy in various GaN HEMTs, SiC MOSFETs, SiC diodes, Si diodes, and Si superjunction (SJ) MOSFETs.

larger than 20% of the total  $C_{\rm OSS}$  stored energy ( $E_{\rm OSS}$ ) at the frequencies above 20 MHz, which is rarely observed in other types of power devices. From the system viewpoints, this loss starts to become a significant portion of the device total loss in high-frequency (>MHz) soft-switching applications [103]. In HSW or low-frequency applications, this loss is typically much lower than the other device losses (e.g., I-V overlap loss). It can induce an unexpected junction temperature climb-up [104], [108] and significantly impair the system efficiency [98], [109].

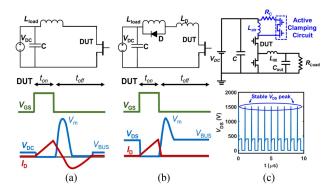

Several approaches have been utilized to characterize the  $C_{\rm OSS}$  loss, which are summarized in Table VI. In general, researchers attempted to quantify this loss by using either the calorimetric (thermal) method [108] or the electrical methods, including the Sawyer–Tower method, nonlinear resonance method, and unclamped inductive switching (UIS) method [104], [110], [111].

All these methodologies have advantages and limitations. For example, in the calorimetric approach, the device under test (DUT) is placed in parallel with an active switch; the DUT is turned OFF all the time with the  $V_{\rm DS}$  set by the active switch, and the DUTs  $C_{\rm OSS}$  loss is derived from its  $T_J$  change. This method allows for measuring the device  $C_{\rm OSS}$  loss in working soft-switched converters without frequency limitation. In this method, however, the system calibration could be laborious and the separation of device  $C_{\rm OSS}$  losses from other losses could be challenging and time-consuming. Also, the accuracy of the calorimetric measurement can be lesser at low power levels.

By contrast, the implementation of an electrical method and the relevant data processing is usually simpler. The Sawyer–Tower method relies on a network consisting of the DUT, a reference capacitor, and a power amplifier that generates the sinusoidal excitation. The DUT is always OFF; its large-signal charge–voltage waveforms can be obtained from the network's input voltage ( $v_{\rm IN}$ ) and the capacitor voltage ( $v_{\rm REF}$ ), followed by the  $C_{\rm OSS}$  loss extraction from the hysteresis of charge-voltage waveforms. In the nonlinear resonance and UIS methods, the DUT operates in both ON and OFF states. In its OFF-state, a resonance is produced between the load inductor and the DUTs  $C_{\rm OSS}$ ; the  $C_{\rm OSS}$  loss is extracted by analyzing the loss in this resonance process based on the DUTs  $V_{\rm DS}$  or  $I_{\rm DS}$  waveforms.

| Methodology                     |                  | Fe                                  | atures                               |                                     | Advantages                                                                                                                                                                                   | Limitations                                                                                                                                                                            |  |  |

|---------------------------------|------------------|-------------------------------------|--------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -                               | DUT<br>State     | Number of<br>Required<br>Components | Key Device<br>Parameter<br>Monitored | C <sub>OSS</sub> Loss<br>Extraction | •                                                                                                                                                                                            |                                                                                                                                                                                        |  |  |

| Calorimetric<br>[108]           | OFF              | Many                                | $T_{ m J}$                           | Maybe<br>complex                    | <ul> <li>Application-use condition: soft-switch, high-frequency converters.</li> <li>Immune to limitations of electrical approaches, e.g., distorted waveforms at high frequency.</li> </ul> | <ul> <li>DUT constant OFF; System setup and calibration could be complicated and time-consuming.</li> <li>The separation of Coss loss from other losses can be challenging.</li> </ul> |  |  |

| Sawyer-<br>Tower [104]          | OFF              | Medium                              | $v_{ m REF}, v_{ m IN}$              | Relatively<br>Convenient            | <ul> <li>Small number of components<br/>required.</li> <li>Can generate Q-V and C-V curves<br/>of the DUT in large-signal switch.</li> </ul>                                                 | DUT constant OFF.     Selection and implementation of the key components may affect the loss extraction accuracy.                                                                      |  |  |

| Nonlinear<br>Resonance<br>[110] | ON<br>and<br>OFF | Few                                 | DUT's $V_{ m DS}$                    | Convenient                          | <ul> <li>Very small number of components involved.</li> <li>Can evaluate the impact of ON-state current on Coss loss</li> </ul>                                                              | Accuracy sensitive to waveform distortion and data processing.     Does not account for C <sub>OSS</sub> loss due to the conduction of leakage current.                                |  |  |

| UIS<br>[111], [112]             | ON<br>and<br>OFF | Few                                 | DUT's $I_{ m DS}$                    | Convenient                          | Very few components involved.     Can evaluate the impact of ON-state current on Coss loss     Account for conductive and                                                                    | Need to carefully calculate the ESR losses of inductors, capacitors, and parasitics                                                                                                    |  |  |

capacitive Coss losses

TABLE VI SUMMARY OF THE PROPOSED  $C_{OSS}$  Loss Measurement Approaches as Well as Their Features, Advantages, and Limitations

Despite the simpler setup, the accuracy of these electrical approaches may be compromised due to the variability and noise of waveforms and equipment, e.g., limited probe bandwidth, probe delays, and waveform distortion at high frequencies [113], [114]. In addition to the tradeoff between thermal and electrical approaches, the Calorimetric and Sawyer–Tower methods only involve the device OFF-state, which disallows for the study of the impact of ON-state current on  $C_{\rm OSS}$  loss. All these tradeoffs need to be considered when interpreting the  $C_{\rm OSS}$  loss data from various methods.

Finally, the origin of  $C_{\rm OSS}$  loss in GaN HEMTs is still contentious [108], [112], [115], [116], while a consensus is reached that the carrier trapping/detrapping induced  $C_{\rm OSS}$  hysteresis is a key root cause. However, the location, time constant, energy level, and physical origins of the relevant traps remain unclear [112]. The leakage current in the epitaxial structure [108] and the resonance on the Si substrate [116] have been reported to contribute to the  $C_{\rm OSS}$  loss. With the origin of  $C_{\rm OSS}$  loss remaining not fully clear, there have been relatively few reports on its reduction strategies. An experimental work has shown that the  $C_{\rm OSS}$  losses can be reduced by re-engineering the GaN HEMT architecture and epitaxial stack [108].

From the application viewpoint, the  $C_{\rm OSS}$  loss significantly impacts the device selection for high- and very high frequency power converters [105]. In parallel to understanding its origin and mitigation from device perspectives, an immediate need for applications is to provide such information in the device datasheet and the relevant models in the device application note. To facilitate this to happen soon, a widely accepted characterization method is preferable, which should ideally involve the device ON- and OFF-states and best represents the device's steady-state switching in converters [111], [112].

# C. Dynamic Threshold Voltage in SP-HEMT

Bias-temperature  $V_{\rm TH}$  instability has been a crucial research topic of Si and SiC MOSFETs for decades. It was also studied for GaN HEMTs with various gate architectures. Early studies focused on GaN metal-insulator-semiconductor (MIS) HEMTs. The  $V_{\rm TH}$  instability in MIS-HEMTs is due to the trapping at the insulator/GaN interface or in the bulk dielectric, which are similar to Si and SiC MOSFETs. A thorough review of the  $V_{\rm TH}$  instability in GaN MIS-HEMTs is provided in [117].

In recent years, as p-gate gradually becomes the prevailing E-mode GaN technology, the research focus shifts to commercial p-gate HEMTs [87], [118], [119], [120], [121], [122], [123]. Unlike the  $V_{\rm TH}$  instability in MOSFETs and MIS-HEMTs, the dynamic  $V_{\rm TH}$  is an intrinsic property related to the floating p-GaN layer in SP-HEMT. As shown in Fig. 4, the SP-HEMT gate stack consists of a p-GaN Schottky junction back-to-back series connected with a p-GaN/AlGaN/GaN p-n junction. As the bias condition (forward or reverse) of these two junctions is opposite, the charges in the p-GaN layer cannot be effectively supplied or extracted in fast switching, making a "floating" p-GaN layer.

Latest progress in the  $V_{\rm TH}$  instability studies for SP-HEMTs is reviewed in [124]. The charge storage process in p-GaN usually leads to a positive dynamic  $V_{\rm TH}$  shift [120]. This  $V_{\rm TH}$  shift increases with the OFF-state blocking voltage and the switching frequency [122]. It is worth mentioning that the GIT features an Ohmic contact on p-GaN, allowing for effective charge supply/extraction and thereby a stable  $V_{\rm TH}$ .

In addition to the floating p-GaN, trapping may also contribute to the dynamic  $V_{\rm TH}$ . Under a forward  $V_{\rm GS}$ , a  $V_{\rm TH}$  shift can be impacted by two trapping mechanisms [125], [126], [127]. The

first mechanism is hole trapping and recoverable, which creates a negative  $V_{\rm TH}$  shift. The second mechanism is electron trapping and slow in recovery, causing a positive  $V_{\rm TH}$  shift [125], [127].

The dynamic  $V_{\rm TH}$  shift could considerably impact the device switching operations [124]. With a positive shift, the reverse conduction voltage of SP-HEMT increases, leading to higher power loss. The dynamic  $V_{\rm TH}$  will primarily impact the turn-ON loss of SP-HEMTs [43]. It also demands a sufficiently high gate-drive voltage to fully turn-ON the device, which reduces the safety margin for the gate reliability. Hence, circuit simulations should consider the dynamic  $V_{\rm TH}$  to depict the practical circuit characteristics. Recently, a SPICE model with dynamic  $V_{\rm TH}$  is developed [121] and used to analyze the switching transients in a phase-leg circuit [128].

#### D. Other Issues Associated With Composite Devices

Since composite devices are combinations of multiple chips, they may face instability issues not only on GaN HEMTs but also associated with the interconnection between Si devices and GaN HEMTs. For example, some instability issues have been reported in cascode GaN HEMTs. During high-current, turn-OFF conditions, a divergent oscillation can occur because of the capacitance mismatch between the GaN and Si switches [129]. Additionally, the added inductance to the bond wires between the switches and the Si avalanche can also cause an increase in the internal switching losses [130]. To minimize the interconnection induced loss, the latest generation of commercial cascode GaN HEMTs eliminates the internal bond wires between the two chips by directly stacking the Si chip onto the source pad of GaN HEMT [22]. However, in some extreme instances, false turn-ON events can occur [131], and SC oscillations can cause catastrophic failures [132]. On the other hand, the gate instability is usually not an issue in the cascode GaN HEMT or direct-drive device because an Si MOSFET is primarily driving the device or additional protection circuits are copackaged with the GaN HEMT.

# VI. ROBUSTNESS

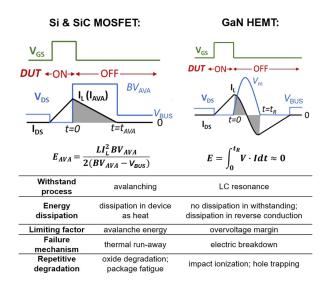

A critical robustness requirement of power devices in many applications, such as motor drives, automotive powertrains, and electric grids, is the capability of withstanding overvoltage, overcurrent, and surge-energy events before the protection circuitry intervenes. The robustness is usually characterized by UIS (i.e., avalanche) and SC tests for Si and SiC power transistors. GaN HEMTs are known to possess limited SC robustness and no avalanche capabilities. Moreover, under some out-of-SOA conditions, GaN HEMTs withstand the stress or degrade/fail very differently as compared with Si and SiC devices. This section will present the SC, surge energy, and overvoltage robustness of GaN HEMTs. Note that the gate robustness is also very relevant to p-gate GaN HEMTs. Due to its close correlation with the gate lifetime, we will discuss it in Section VII.

# A. SC Robustness

SC fault events occur when a conduction path with minimum impedance is present between the switching transistor and the

TABLE VII SUMMARY OF SC ROBUSTNESS REPORTED FOR COMMERCIAL AND R&D GAN POWER TRANSISTORS

| Status       | Туре        | Rated<br>voltage<br>(V) | $R_{\mathrm{G}}\left(\Omega\right)$ | V <sub>GS</sub> (V) | L <sub>para</sub> (nH) | V <sub>BUS</sub> (V) | t <sub>SC</sub> (μs) |

|--------------|-------------|-------------------------|-------------------------------------|---------------------|------------------------|----------------------|----------------------|

|              |             |                         |                                     |                     |                        | 300                  | 308 [138]            |

|              |             | 650                     |                                     | 5                   | -                      | 350                  | 0.7 [138]            |

|              | CD          |                         | 10                                  |                     | •                      | 360                  | 0.66 [138]           |

|              | SP-<br>HEMT |                         |                                     |                     | ~10                    | 360                  | 0.5-0.9 [139]        |

|              | IILIVII     |                         | _                                   |                     |                        | 320                  | 0.5-0.9 [139]        |

|              |             |                         | N/A                                 | 6                   |                        | 350                  | 0.7 [140]            |

|              |             |                         |                                     |                     |                        | 400                  | 0.6 [140]            |

| Comm.        | •           | 80                      |                                     |                     | N/A                    | 60                   | 12.1 [53]            |

|              | GIT         | 600                     | RC driver                           |                     | N/A -                  | 350                  | >10 [141]            |

|              | GH          | 600                     | KC di                               | iver                | IN/A                   | 360                  | 0.2 [141]            |

|              | Cascode     | 650                     | 1                                   | 8                   | 50                     | 100                  | 12 [142]             |

|              |             |                         |                                     |                     |                        | 200                  | 5 [142]              |

|              |             |                         |                                     |                     |                        | 300                  | 4.4 [142]            |

|              |             |                         | 8                                   | 12                  | 48                     | 300                  | 1.80 [143]           |

|              |             |                         | 16                                  | 6.5                 | 7.5                    | 250                  | 7.60 [144]           |

|              | D-mode      | 650                     | 50                                  | 8                   | N/A                    | 400                  | 0.50 [147]           |

| R&D          | SP-         | 600                     | 6.3                                 | 5                   | 48                     | 200                  | 2.00 [143]           |

|              | HEMT        | N/A                     | 15                                  | 6                   | <10                    | 400                  | >10 [148]            |

|              | Cascode     |                         | 45                                  | 9                   | N/A                    | 400                  | >3 [145]             |

| Vertical GaN |             | 650                     | RC dı                               | iver                | 48                     | 400                  | 30.5 [146]           |

$R_{\rm G}$  and  $\,L_{\text{para}}$  are the resistance and parasitic inductance in the gate driver.  $V_{\rm BUS}$  is the bus voltage.

power supply. The SC events usually drive devices into the saturation mode of operation, with both a high voltage and a high conduction current stressing the device [133]. A typical SC robustness requirement is the 10  $\mu s$  SC withstanding time ( $t_{SC}$ ) under the bus voltage ( $V_{BUS}$ ) and driving conditions identical to the application-use operation [134]. If the 10  $\mu s$   $t_{SC}$  is unattainable, according to the U.S. Department of Energy 2025 Vehicle Drive Roadmap [135], a 2  $\mu s$   $t_{SC}$  of the power device together with the ultrafast protection circuit is needed.

There are generally four types of SC conditions that can happen in a power electronics system: the arm SC, which is also called the hard-switching fault (HSF) or SC type I, the series arm SC, the output SC, and the ground SC [136], [137]. Among these conditions, HSF is usually employed for the evaluation of the power device SC robustness [134]. This section summarizes the single-event  $t_{SC}$ , failure mechanisms, and repetitive SC test results recently reported for GaN HEMTs.

From the application viewpoint, it is critical to measure the SC capability under the application-use driving conditions (e.g., the same driving circuitry and voltage). Table VII summarizes the reported  $t_{\rm SC}$  of various GaN HEMTs under the driving condition similar to their normal operation [138], [139], [140], [141], [142], [143], [144], [145], [146], [147], [148]. Note that the  $t_{\rm SC}$  variation seen in some articles is believed to be due to distinct driver conditions. For example, a large gate resistor ( $R_G$ ) is used in [149] and [150], leading to long  $t_{\rm SC}$ . The large  $R_G$  slows down the device turn-ON, resulting in a smaller peak SC current. Additionally, the device gate-leakage current increases in the SC withstanding process due to the temperature elevation.

The leakage current across the large  $R_G$  could make the device  $V_{\rm GS}$  significantly lower than the usual operation [151], leading to even lower SC current and a thermal stress much lower than practical SC scenarios.

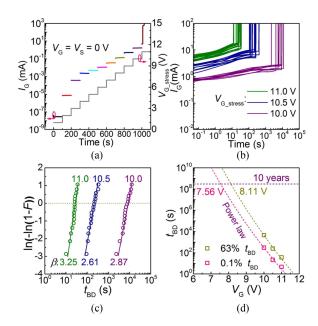

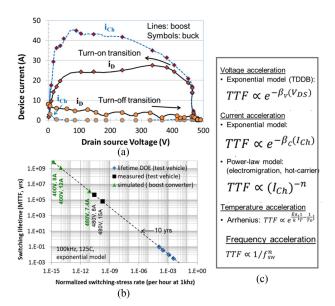

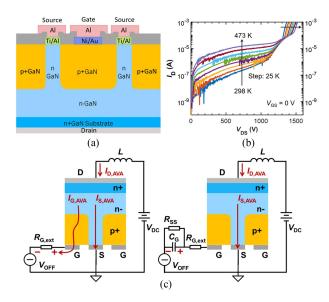

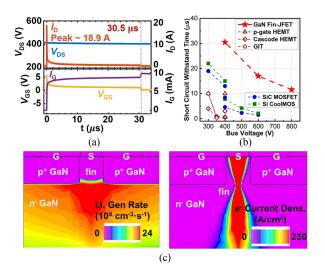

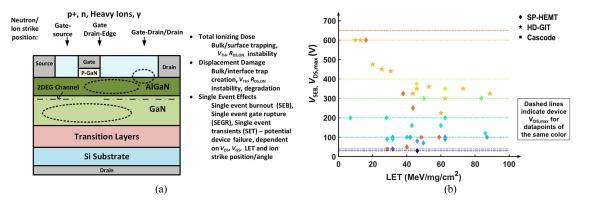

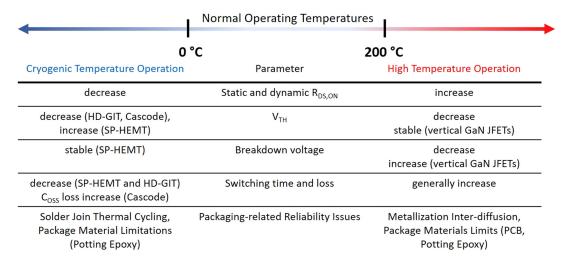

The reported  $t_{\rm SC}$  for 650 V SP-HEMTs is generally below 1  $\mu$ s at  $V_{\rm BUS}$  higher than 350 V [133], [139], [140], [150], [151], [152]. For HD-GITs, an RC driving circuit is employed with a large  $R_G$  (100+  $\Omega$ ) to minimize the quiescent gate current [141]. This suppresses the device  $V_{\rm GS}$  under the SC stress, leading to a fast  $I_D$  drop and a  $t_{\rm SC} > 10~\mu{\rm s}$  at  $V_{\rm BUS}$  below 350 V [141], [153], [154]. However, similar to SP-HEMTs, the  $t_{\rm SC}$  drops drastically to  $< 1~\mu{\rm s}$  at  $V_{\rm BUS} > 350$  V [141], [151], [153]. Cascode devices also show limited SC robustness. As the cascode gate is the Si MOS, the  $t_{\rm SC}$  is not sensitive to  $R_G$  [143], [151]. Very few SC reports are available on direct-drive device. Song et al. [24] report the SC tests of a 650 V, 100 A direct-drive GaN HEMT, which is intentionally stopped in 100 ns. The device can withstand an SC current up to 358 A within this SC duration.