# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# A Multilevel Supply Modulator for RF Power Amplifier using 130nm CMOS Technology: Comparator Based Approach

Gangadharan, Shaina Department of EECE, SET, Sharda University

Khanam, Ruqaiya Department of EECE/Centre for AI in Medicine, Imaging & Forensic, Sharda University

Thangasamy, Veeraiyah

Department of Electrical and Electronics Engineering, MITS

https://doi.org/10.5109/7183379

出版情報: Evergreen. 11 (2), pp. 974-983, 2024-06. 九州大学グリーンテクノロジー研究教育センター

バージョン:

権利関係: Creative Commons Attribution 4.0 International

# A Multilevel Supply Modulator for RF Power Amplifier using 130nm CMOS Technology: Comparator Based Approach

Shaina Gangadharan<sup>1</sup>, Ruqaiya Khanam<sup>2,\*</sup>, Veeraiyah Thangasamy<sup>3</sup>

<sup>1</sup>Department of EECE, SET, Sharda University, India

<sup>2</sup>Department of EECE/Centre for AI in Medicine, Imaging & Forensic, Sharda University, India <sup>3</sup>Department of Electrical and Electronics Engineering, MITS, Chitoor, India

> \*Author to whom correspondence should be addressed: E-mail: dr.kruqaiya@gmail.com

(Received December 29, 2023: Revised March 08, 2024: Accepted April 11, 2024).

Abstract: Energy-efficient power amplifiers (PAs) that preserve battery life for extended periods of time, without sacrificing linearity are becoming increasingly important for mobile devices. The supply modulator in the envelope tracking (ET) design affects the efficiency enhancement in radio frequency (RF) PAs. This paper presents design of a comparator-based supply modulator that dynamically controls the supply voltage required to drive the PA. A preamplifier has been designed to amplify the RF input signal and an envelope detector tracks the amplified signal within the comparator's swing of 0 - 3.3 V. A single-bit comparator has been designed that works at 2.1 GHz frequency with a minimal rise-time delay of 0.2 ns and it is cascaded to operate as an 8-bit comparator. The multilevel supply modulator receives the input from the 8-bit comparator. This determines the amount of current flow to the PA by limiting current flow through the transistors that are turned OFF by the comparator. Hence the comparator based envelope tracking system is aimed at designing the ET circuit and improving the power added efficiency to approximately 45% Moreover the ET circuit does not comprise of bulky components like the inductors, thus expected to consume lesser chip area.

Keywords: Radio Frequency Power Amplifier; 5G mobile communication; 130nm CMOS; eight-bit comparator; envelope tracking; multilevel supply-modulator; linearity; efficiency

#### 1. Introduction

Modern technology electronic circuits have shrunk in size during the past century, but their power density has grown dramatically as the industry shifted toward digitization and miniaturization. In modern electronic industry, designing an effective thermal management system to transfer heat away from the electronic chips becomes crucial 1). High battery power consumption has been a major concern apart from low quality signals when using data services in mobile technology. The reason for high battery power consumption at specified output power level is due to poor efficiency of power amplifier in the mobile transceiver, which dissipates a major portion of the power drawn from the battery in the form of heat and goes unutilized. It has therefore become necessary to reduce power dissipation by controlling the power drawn by the transceiver circuit in the mobile phones. Mobile communication has gained a great momentum since the 80's and has been evolving itself in decades. The use of mobile phones and internet has increased rapidly in the past two to three years in India 2), thus looking into implementing 5G has become a need to maintain the requirement of the consumers. Mobile technology has evolved from using analog technology (1G) in the 80's to successive usage of digital technology (2G, 3G, 4G and 5G) supporting additional features<sup>3)</sup>. The vast opportunities for optimization and efficiency gains will be the next area of study for widely used smart devices and a variety of applications in 5G networks 4). Therefore to stay active in the market, data service providers have to ensure high signal strength and the mobile companies have to take care of the high power consumption without compromising on the features provided by them like usage of social networking, video streaming, web browsing, music downloads, and many more to attract market. Long Term Evolution (LTE), which is the actual 4G used technologies like orthogonal frequency division multiplexing (OFDM), multiple input multiple output (MIMO), adaptive beam-foaming antennas that help reducing network congestion 5).

Linearity of the transmitter is compromised upon due to the high peak to average power ratio (PAPR) due to which the PA is forced to work in the back-off region resulting in high power consumption <sup>6)</sup>. This has led to research in the areas of efficient power enhancement techniques in the power back-off region. In the work depicted in <sup>7)</sup> the supply

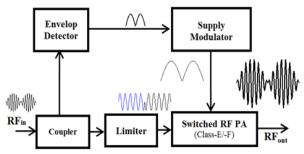

voltage was varied using DC - DC converter to modulate the supply voltage to the RF power amplifier (PA) and showed that the efficiency of the RF PA can be improved effectively. Power amplification is the final stage in the transceiver block which deals with high power level signals for transmission 8) and dissipates about 50% 9) of the total power, hence reducing the power efficiency and in turn the battery life. The performance of a power amplifier is characterized by the output power and gain without compromising on the linearity and efficiency. Studies have revealed that envelope tracking 6) 10) is a reliable method to improve the efficiency of the power amplifier, where the principle adopted is "tracking the RF signal voltage and modulating the supply voltage according to the signal power" as shown in Fig. 1. The envelope tracking further operate a supply modulator circuit which is responsible to dynamically control the current to the power amplifier and in this way the power efficiency is improved.

Fig. 1: Conventional ET system

Two primary considerations in any circuit design, whether digital or analog, are power efficiency and speed 11) 12). The most effective strategies to obtain low power are to lower the supply voltage (  $V_{DD}$ ) and have all chip components function in the subthreshold zone 13) CMOS transistors have been considered as most reliable in the design of high performance IC such as transceivers, analog to digital converters, memories etc.<sup>14)</sup>. With the advent of 4G and moving towards 5G, there is an involvement of complex modulation methods like CDMA, OFDM etc. The RF transmitter has been becoming more and more complex while moving from 3G to 5G and future generation communication system which requires further miniaturization of transceivers, high data rates, high modulation bandwidth etc. 6). In analog design scaling of transistors cannot be done abruptly, as intrinsic circuit capacitances and interconnect parasitic capacitances play a major role in reducing the speed and bandwidth of analog circuits 15).

A wide bandwidth hybrid supply modulator for LTE-A application was designed by <sup>16</sup>, using 0.18 µm CMOS technology, which tracks the envelope at a speed of 100MHz and also controls the bandwidth at low bandwidth envelope region. Since the modulator controls the power loss in the PA, the overall efficiency of the ET PA is the product of the RF power amplifier efficiency and the

modulator efficiency. In the architectures 17) 18), the switching transistor, employed as the power modulator has higher switching losses resulting in decreased overall efficiency. A review conducted by 17) on various architectures integrated with Pas indicate that ET is preferable over EER or the Doherty methods when used in linear mode and 5G technologies, due to the wide intermediate frequency requirements. Moreover, when the RF amplifier is operated near the maximum output power region, the output power is more sensitive to drain bias; and any noise developed by the supply modulator at the drain of the RF power amplifier, possibly fall into the receiver band 19), which requires a low noise supply modulator design. Recently work done by 20) used a modulated rapid load pull system which showed good linearity, but with reduced efficiency.

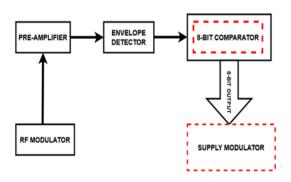

.The focus in this work is the design of a comparator based supply modulator. The emphasis lies in the concept of turning only appropriate number of transistors ON to control the current flowing through the load

Fig. 2: Block Diagram of proposed system

The proposed design as shown in Fig. 2 is suitable for implementation in a conventional radio frequency integrated circuit (RFIC) design flow using CADENCE platform.

# 2. Methodology

For supply modulation in PA architecture, two well-known techniques have been found in the literature, namely envelope elimination and restoring (EE&R) and envelope tracking (ET). The EE&R works better on constant amplitude non-linear PAs with dynamically controlled supply voltage. The ET is preferable for the linear Pas whose poor power efficiency especially at low power levels can be mitigated by applying the supply voltage accordingly <sup>21</sup>. The main challenges that have to be overcome for an ET circuit are:

• A high efficiency supply modulator has to be designed

- Has to consider the fact that the efficiency at lower envelope voltage is low in comparison to high envelope voltage due to its inability to compress the low power region.

- Minor distortion in the supply modulator will be modulated on to the output of the RF PA. Hence the supply modulator has to be designed with high precision.

In essence, an ET circuit is made up of a PA circuit and a bias modulator. The supply modulator is in charge of dynamically regulating the bias voltage applied to the PA. In order to keep up with the rapid variations in voltage levels, the supply modulator needs to be extremely effective and quick. Simultaneously, the switching frequency must be kept constant to accommodate the signal's instantaneous variations in voltage level. Furthermore, it is also important to keep in view that the change in supply voltage is appropriate with the transistor operating conditions <sup>18</sup>). Ensuring compliance with all of these is also essential to guarantee that the PA's linearity is not compromised.

The proposed system in Fig. 2 shows that the input RF signal is amplified by a preamplifier circuit to make it compatible with the comparator circuit which is designed to compare voltage levels from 0-3.3V. This signal is then passed through an envelope detector circuit which captures the voltage level of the signal from the preamplifier, thus forming an envelope over the bandwidth of the RF signal. The amplitude of the envelope is compared by a high speed 8-bit comparator that turns on individual output bits based on the input amplitude of the envelope. The 8 output bits of the 8-bit comparator controls the bias conditions of the transistorized supply modulator circuit. The supply modulator circuit controls the current flowing into the PA circuit, thus reducing the power loss by reducing the DC input power to the PA prior to being consumed.

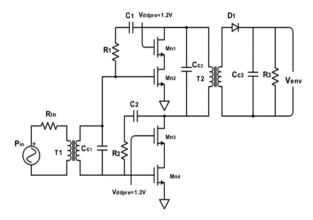

#### 2.1 Preamplifier and envelope detector circuit

It was noticed that when the input RF signal of the range from -20 dBm to 10 dBm was applied to the envelope detector circuit, its output was not sufficient enough to be compared with the reference voltage levels of the – 8-bit comparator circuit. The comparator operates at the reference voltage range from 0 V to 3.3 V. Therefore, a single stage Cascode Class AB amplifier as shown in Fig.3 has been designed to amplify the input RF signal into the desired range from 0 V to 3.3 V.

The purpose of using an envelope detector is to lock the signal voltage by continuously monitoring RF signal voltage fluctuations. Envelope shaping is seen to be a crucial component for increasing linearity and efficiency while reducing the load on the supply modulator. <sup>22</sup> Envelope detectors designed in <sup>19) 23)</sup> have emphasized on maintaining the supply voltage greater than the knee voltage in order to avoid nonlinearities in the PA characteristics. The envelope detector designed in this

work comprises of a diode acting as a rectifier and a resistor-capacitor combination acting as a filter.

Fig. 3: Pre-amplifier and Envelope Detector

The envelope detector designed can track the input RF signal up to the modulation bandwidth of 40MHz and is much above the suggested bandwidth of the LTE signal. The diode acts as a rectifier which allows positive signals to pass through it and the conduction has been optimized for 0 V to 3.3 V by adjusting the device area to 200  $\mu m^2$  (square micrometers) with a W/L ratio of 100  $\mu m$  by 2  $\mu m$  for the diode.

The resistor and capacitor which contributes to the RC time constant is adjusted so that the capacitor discharges slowly. The W/L ratio for both the components has been adjusted to obtain a resistance of  $258\Omega$  and a capacitance of 40 pF respectively.

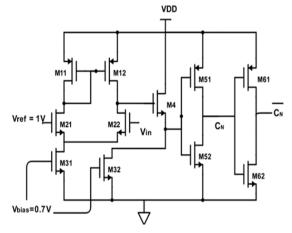

#### 2.2 Single bit high speed comparator

Analog comparators act as checkers which are basically cascaded inverters followed by latches <sup>24)</sup>. <sup>25)</sup> proposed an analog comparator which uses as many as 24 transistors resulting in device degradation and transient faults leading to large circuit size.

Fig. 4: Single-bit comparator

In this work, a comparator design using as low as 7 transistors is proposed as shown in Fig.4, in a 130 nm CMOS technology providing smaller sized foot print, and still yielding compatible results. The comparator output is followed by two inverters to provide inverted and buffered output needed for the supply modulator circuit. The comparator compares the envelope signal input ( $V_{\text{env}}$ ) (represented as  $V_{\text{in}}$  in the Fig.4) with the pre-determined reference voltage ( $V_{\text{ref}}$ ) which is equal to 1V. If  $V_{\text{env}}$  is greater than  $V_{\text{ref}}$ , the comparator circuit goes to saturation thus producing an output which is `1', or else the output is `0'The reference value is finalised as 1V by varying the operating frequencies upto 100 MHz.

For comparator design, the permissible delay for the rise time is 10% of the total time. The RF signal for LTE modulation has a maximum bandwidth of 40 MHz; giving 2.5 ns delay time with 25 ns total time. The work in confirms that propagation delay of up to 10 ns is acceptable for RF communication applications at high frequencies..

# 2.3 8-bit comparator circuit

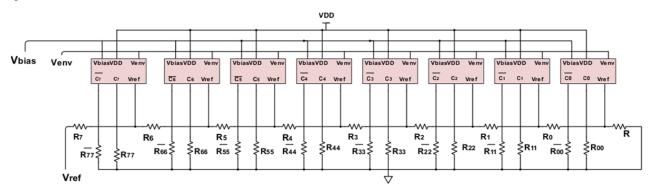

The 8-bit comparator circuit comprises of 8 single-bit comparator circuits cascaded together as shown in Fig. 5. It was noticed that the value of V<sub>ref</sub> in the single bit comparator affected the output adversely in a way that when it was increased beyond 2.7V the maximum output saturation voltage started reducing. Hence the reference voltage for the cascaded 8-bit comparator is set to 2.7V which is divided by a potential divider circuit to provide 8 levels of reference voltages to the individual comparator. The output of the envelope detector (Venv) is applied as the input to the comparator. We will compare the input, which is the output signal from the envelope detector circuit, to the reference voltage at each comparator block. The comparator outputs are saturated to 3.3 V, logic "1" is produced for all of the outputs where the reference signal is greater than or equal to the envelope signal value. These are the inputs that the supply modulator receives.

Fig 5: 8 - bit comparator circuit

#### 2.4 Supply modulator

In ET PA circuits, supply modulator design is regarded as a key technique. Supply modulators can be classified as linear and discrete. Linear modulators which are designed as Class AB/B and Class G/H amplifiers requires differential input excitation and very good symmetry both in matching circuits and active devices. Discrete modulators, on the other hand can use pulse width modulation techniques. Multilevel discrete supply modulators are based on multiple switching levels and is advantageous for ET circuits due to high efficiency and high bandwidth tracking <sup>27)</sup>.

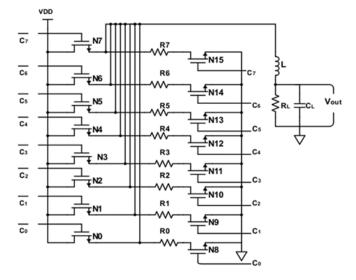

The supply modulator circuit design comprises of two arrays of 8 NMOS transistors as shown in Fig. 6. The uncomplemented and complemented outputs from the  $-\,8$ -bit comparator circuit serve as inputs to the transistors. The output is measured across a tank circuit comprising of a resistor  $(R_L)$  and a capacitor  $(C_L)$ . By this arrangement of the transistors discrete levels of voltage are obtained at the output. The output signal strength is determined by the number of transistors that are ON at a particular instant of time.

Fig 6: Supply modulator circuit

| Table 1: Dev | 11CE \$17 | res and | values |

|--------------|-----------|---------|--------|

| Device     | Preamplifier                             | Envelope<br>Detector            | Comparator                                                  | Supply modulator             |

|------------|------------------------------------------|---------------------------------|-------------------------------------------------------------|------------------------------|

|            | Mn1, Mn3 (W = 120μm, L= 130nm            |                                 | M11, M12. M51, M61<br>(W = 5μm, L = 130nm                   | N0 -N15 (W = 1μm, L = 130nm) |

| Transistor | Mn2, Mn4 (W = 120μm, L = 130nm)          |                                 | M21, M22, M31, M32,<br>M52, M62, M4 (W=<br>2.5μm, L= 130nm) |                              |

| Resistor   | $R1, R2 = 1K\Omega$                      | $280\Omega$                     |                                                             | $R_L = 10\Omega$             |

| Capacitor  | C1, C2 = 2 pF, Cc1=<br>1pF, Cc2 = 0.64pF | 40pF                            |                                                             | $C_L = 1pF$                  |

| Diode      |                                          | $W = 100 \mu m ,$ $L = 2 \mu m$ |                                                             |                              |

| Inductor   |                                          |                                 |                                                             | L = 190pH                    |

#### 3. Results and discussion

Varying voltage levels and sources (AC/DC) are needed for different power utilities to function. Because switching and conduction losses in components lose a significant amount of power, an alternative method is required <sup>1)</sup>. The whole idea of carrying out this work has been aimed at designing a supply modulator that would dynamically control the current flowing into the PA circuit. As expected the supply modulator has been designed using an 8-bit comparator approach.

# 3.1 Preamplifier and envelope detector

An Amplitude Modulated RF signal has been provided at the input of the preamplifier. The input signal strength was varied from -12 dBm to 6 dBm (105 mv to 765 mV approx.). It was noticed that the signal strength increased from 1.4 V to 5.1 V peak for the corresponding signal inputs as shown in Table 2.

Table 2: Preamplifier and Envelope detector

| rable 2. I reamplifier and Envelope detector |                      |                |                      |  |  |

|----------------------------------------------|----------------------|----------------|----------------------|--|--|

| P <sub>in</sub> (dBm)                        | V <sub>in</sub> (mv) | $V_{(pre)}(V)$ | V <sub>env</sub> (V) |  |  |

| -12                                          | 105                  | 1.4            | 0.8                  |  |  |

| -10                                          | 175                  | 2.3            | 1.25                 |  |  |

| -8                                           | 205                  | 2.6            | 1.5                  |  |  |

| -6                                           | 276                  | 3.1            | 1.75                 |  |  |

| -4                                           | 336                  | 3.4            | 2                    |  |  |

| 0                                            | 395                  | 3.8            | 2.37                 |  |  |

| 4                                            | 595                  | 4.6            | 2.9                  |  |  |

| 6                                            | 765                  | 5.1            | 3.2                  |  |  |

The envelope detector circuit is used to process the preamplifier's output. For every value of the input RF signal the output of the envelope detector is measured. The observations are recorded in Table 1 and the two waveforms for minimum value and maximum value of the input signals can be viewed in the Fig. 7. As observed the output voltage of the envelop detector exactly follows the input signal voltage. In Fig. 7 (a) and (b), it can be noticed that for the input power, Pin = -12 dBm, the envelope voltage is 0.8 V and for Pin = 6dBm the envelope voltage is 3.2 V, and so it is for the intermediate readings

Fig. 7: RF input and envelope output for (a) Pin = -12 dBm (b) Pin = 6 dBm

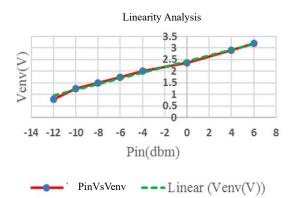

The linearity graph in Fig. 8. shows that the output voltage of the envelope detector ( $V_{env}$ ) circuit varies almost linearly with the input signal power ( $P_{in}$ ). This is a basic requirement to ensure that the supply modulator and the PA outputs are linear, thus improving the efficiency of the PA. The green dash line graph indicates the expected linear plot and the red line plot with blue dots indicate the output plot obtained from the envelope detector circuit and the two plots almost overlap each other

Fig. 8: Linearity graph for the envelope detector

#### 3.2 Single bit comparator results

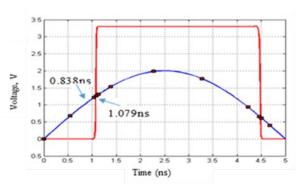

The reference voltage determines how wide the pulses produced by the single-bit comparator circuit are. 1 volt is the fixed reference voltage. Figure 9 shows that the comparator output saturates at the reference voltage with a delay as short as 0.2 ns. The time it reaches saturation is 1.079 ns, and the time measured at the reference voltage of 1 V is 0.838 ns. In response to variations in the RF signal's input signal power, the delay is thus roughly 0.2 ns, demonstrating a very rapid switching speed with a very minimal delay. The comparator's efficacy is confirmed for frequencies up to 2.1 GHz, and it has been noticed that the switching delay is less than 10ns. performance for ET application. The switching speed of the comparator in this design is very high, with a rise time delay approximately 0.2 ns and thus is found suitable for the intended envelop tracking design.

Fig. 9: Single bit comparator propagation delay

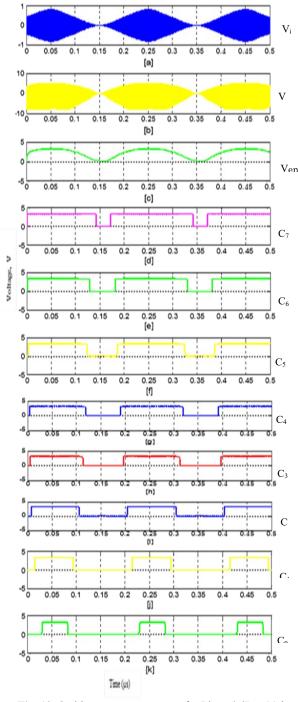

# 3.3 8-bit comparator results

The 8-bit comparator circuit was tested by applying input signals with signal power varying from -12 dBm to 6 dBm. As the signal strength increases, more number of comparators tend to turn ON, until all the comparator outputs are ON, indicating maximum signal strength. It has been noticed from the graphs in Fig. 10 that for an input signal voltage as low as 100 mV only one comparator

output is ON and for the input signal approximately equal to 765mV all the comparators turn ON.

Table 3 shows the outputs as the input signal strength varies from approximately 100 mV to 800 mV. The plot in Fig. 10 reflects the condition when all the comparator's outputs are ON for the maximum input signal of 765 mv ( $\approx$  6 dBm recorded from the CADENCE).

**Fig. 10:** 8 - bit comparator outputs for Pin = 6 dBm (a) input RF signal; (b) preamplifier output; (c) envelope detector output (d) - (k) 8-bit comparator outputs C0 through C7

| Table 3: Comparator output for varying input voltage |          |            |          |    |                   |    |    |    |    |    |    |

|------------------------------------------------------|----------|------------|----------|----|-------------------|----|----|----|----|----|----|

| Bm)                                                  | nv)      | (V)        | (V)      | 3  | Comparator output |    |    |    |    |    |    |

| Pin (dBm)                                            | Vin (mv) | V(pre) (V) | Venv (V) | C0 | Cl                | C2 | C3 | C4 | C5 | 9D | C7 |

| -12                                                  | 105      | 1.4        | 0.8      | 1  | 0                 | 0  | 0  | 0  | 0  | 0  | 0  |

| -10                                                  | 175      | 2.3        | 1.2      | 1  | 1                 | 0  | 0  | 0  | 0  | 0  | 0  |

| -8                                                   | 205      | 2.6        | 1.5      | 1  | 1                 | 1  | 0  | 0  | 0  | 0  | 0  |

| -6                                                   | 276      | 3.1        | 1.7      | 1  | 1                 | 1  | 1  | 0  | 0  | 0  | 0  |

| -4                                                   | 336      | 3.4        | 2        | 1  | 1                 | 1  | 1  | 1  | 0  | 0  | 0  |

| 0                                                    | 395      | 3.8        | 2.3      | 1  | 1                 | 1  | 1  | 1  | 1  | 0  | 0  |

| 4                                                    | 595      | 4.6        | 2.9      | 1  | 1                 | 1  | 1  | 1  | 1  | 1  | 0  |

| 6                                                    | 765      | 5.1        | 3.2      | 1  | 1                 | 1  | 1  | 1  | 1  | 1  | 1  |

## 3.4 Results from the Supply modulator

All the outputs from the 8-bit comparator are fed to the input of the supply modulator as shown in Fig. 6. After performing the simulation, the required input and output waveforms are selected from the Cadence Virtuoso simulation window for every value of the input signal. These selected waveforms are extracted in the .csv form from cadence and further processed in the MATLAB to generate the waveforms as shown in Fig. 11.

From Fig. 11 (a) it is noted that for an input equal to -8dBm (205mV), there are only two steps indicating that only two transistors are ON and the maximum output voltage is 1.72V as also recorded in Table 3. Similarly, in the subsequent Figures (b) and (c) it has been noticed that as the input voltage increases the number of steps in the output signal increases indicating the number of transistors that are active at that value of input power. It can also be noted that at ascending levels of input power the output voltage at the supply modulator also increases from 1.05V to 3.2V which is an indication of dynamic supply voltage that has been obtained.

In Table 3 the value of the output voltage corresponding to the input voltage has been recorded. The output voltage ( $V_{out}$ ) gradually increases with increase in input voltage ( $V_{in}$ ). It is clear that only the transistors that get the active signal from the comparator are activated, and that the supply modulator's output determines the voltage applied to the PA. As the equivalent input voltage rises, it has been observed that the output power increases steadily. The input voltage displayed in Table 3 and Fig. 12 is derived from the waveforms acquired by CADENCE analysis.

Fig. 11: Supply modulator results for : (a) Pin=-8dBm (b) Pin=-7dBm (c) Pin=-5dBm

Table 4: Supply modulator results

| $V_{DD} = 3.3 \text{ V}$ |                      |                        |                      |       |                      |

|--------------------------|----------------------|------------------------|----------------------|-------|----------------------|

| P <sub>in</sub> (dBm)    | V <sub>in</sub> (mv) | V <sub>(pre)</sub> (V) | V <sub>env</sub> (V) | Steps | V <sub>out</sub> (V) |

| -10                      | 175                  | 2.3                    | 1                    | 1     | 1.05                 |

| -8                       | 205                  | 2.6                    | 1.5                  | 2     | 1.72                 |

| -7                       | 237                  | 2.9                    | 1.6                  | 3     | 2.21                 |

| -6                       | 276                  | 3.1                    | 1.75                 | 4     | 2.5                  |

| -5                       | 330                  | 3.4                    | 2.3                  | 5     | 2.8                  |

| -4                       | 336                  | 3.4                    | 3                    | 6     | 3                    |

| -3                       | 395                  | 4                      | 3.3                  | 7     | 3.1                  |

| -2                       | 412                  | 5.3                    | 3.6                  | 8     | 3.2                  |

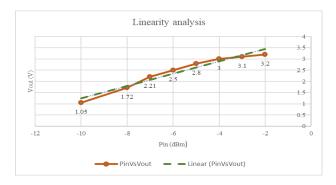

A graph is obtained by plotting the values of the input power to the output voltage of the supply modulator, using Excel and the values recorded from the results which are tabulated in Table 3. The outputs seem to be following the reference linearity plot as can be seen in Fig. 12. the The output voltage varies linearly and in proportion to the input power (Pin). The green dotted line in the plot in Fig. 12 is the linearity analysis plot from Excel which indicates if the

inputs and outputs are linear in their responses. The plot of the input power to the preamplifier to the output voltage at the supply modulator almost coincide with each other which is a clear indication of linearity of the circuits involved.

Fig. 12: Linearity Graph for supply modulator

# 3.5 Results from PA with dynamic supply

The output from the supply modulator was provided as  $V_{DD}$  to the PA. For experimental purpose the preamplifier circuit itself was used as the PA. The results were obtained for fixed supply voltage and dynamic supply voltage. This was done in order to obtain the power added efficiency

(PAE) which is calculated as shown in equation 1 for the dynamic PA supply. For the fixed DC supply voltage biased PA the denominator is the  $P_{dcPA}$  alone.

$$PAE = \frac{P_{out} - P_{in}}{P_{dcPA} - P_{dc}}$$

equ 1

where,

$P_{out}$  is the power obtained at the output of PA  $P_{in}$  is the RF input power

$P_{dcPA} - P_{dc}$  is the difference in the power with varying supply voltages (referred as Pdc (dynamic) in Table 5.

This has been calculated after each iteration using the calculator function in the Cadence Virtuoso. It can be noticed in Table 5 that the PAE of the dynamically controlled PA is comparatively higher than the one using fixed VDD. The PAE is approximately 45% which is higher than the fixed biased PA by approximately 10%. It is also noticed that depending on the number of comparators that are turned ON, the dynamic input DC power also increases. The PA performs linearly upto 6dBm and then saturates.

Table 5: Comparative analysis for fixed and dynamic PA

| $V_{DD} = 3.3 \text{ V}$ |                                                          |           |           |                        |           |         |           |       |        |

|--------------------------|----------------------------------------------------------|-----------|-----------|------------------------|-----------|---------|-----------|-------|--------|

| $P_{in}$                 | $\mathbf{P}_{in}$                                        | $P_{out}$ | $P_{out}$ | P <sub>dc</sub> (fixed | $P_{dc}$  | PAE     | PAE       | Comp. | Output |

| (dBm)                    | (mW)                                                     | (fixed)   | (dynamic) | Vdd) (W)               | (dynamic) | (fixed) | (dynamic) | ON    | (S/L)  |

|                          |                                                          | (W)       | (W)       |                        | (W)       | (%)     | (%)       |       |        |

| -10                      | 0.1                                                      | 68.5m     | 19.12m    | 2.027                  | 711.9m    | 3.3     | 2.6       | 1     | L      |

| -8                       | 0.158                                                    | 99.1m     | 39.41m    | 2.028                  | 782.6m    | 4.8     | 5         | 2     | L      |

| -6                       | 0.25                                                     | 118.4m    | 72.22m    | 2.028                  | 856.9m    | 5.8     | 8.3       | 3     | L      |

| -5                       | 0.3                                                      | 141.1m    | 93.17m    | 2.028                  | 894.3m    | 6.9     | 10.41     | 4     | L      |

| -4                       | 0.4                                                      | 167.6m    | 123.4m    | 2.028                  | 959.7m    | 8.2     | 12.81     | 5     | L      |

| -3                       | 0.5                                                      | 198.6m    | 151.6m    | 2.027                  | 995.3m    | 9.7     | 15.23     | 6     | L      |

| -2                       | 0.63                                                     | 234.8m    | 189.9m    | 2.027                  | 1.052     | 11.56   | 17.9      | 7     | L      |

| 0                        | 1                                                        | 323.5m    | 259.3m    | 2.027                  | 1.103     | 16.03   | 23.41     | 8     | L      |

| 2                        | 1,59                                                     | 478.9m    | 354.3m    | 2.027                  | 1.185     | 23.06   | 29.7      | 8     | L      |

| 4                        | 2.5                                                      | 523m      | 438.2m    | 2.027                  | 1.247     | 26.96   | 34.9      | 8     | L      |

| 6                        | 3.98                                                     | 556m      | 516.5m    | 2.025                  | 1.32      | 27.2    | 38.8      | 8     | L      |

| 8                        | 6.3                                                      | 643m      | 590.7m    | 2.021                  | 1.373     | 31.5    | 42.5      | 8     | S      |

| 10                       | 10                                                       | 694.5m    | 663m      | 2.011                  | 1.464     | 34.03   | 44.6      | 8     | S      |

| S- PA go                 | es into S                                                | aturation | L-I       | A remains Lin          | ear       |         |           |       |        |

| Comp. C                  | Comp. ON indicates the number of comparators in ON state |           |           |                        |           |         |           |       |        |

Fixed refers to Fixed V<sub>DD</sub> and dynamic refers to results after supply has been modulated

Table 6: Comparison with previous work

| Ref       | Technology | Power(Psat) | Gain  | PAE (%) | Frequency | Bandwidth | Efficiency |

|-----------|------------|-------------|-------|---------|-----------|-----------|------------|

|           |            | (dBm)       | (dB)  |         | (GHz)     | (MHz)     | (%)        |

| 28        | 65nm CMOS  | 19.2        | 16    | 55      | 2.4-2.6   | -         | -          |

| 29        | 65nm CMOS  | 24.5        | -     | -       | 2.4       | -         | 52         |

| This Work | 130nm CMOS | 28.21       | 18.21 | 44.6    | 2.1       | 40        | 66.3       |

#### 4. Conclusion

The objective of the paper was to design - 8-bit comparator based multilevel supply modulator for envelop tracking in RF power amplifier which has been successfully demonstrated. The whole circuit was designed on a 130 nm CMOS framework and simulated using CADENCE tools. Transient analysis was carried out and the output of each block in the circuit has been tested. The envelope detector circuit had been tested for various values of the input voltages and it could ceil the output at the required value of voltage. The 8-bit comparator could turn ON the output lines in accordance to the input power in order to activate the corresponding transistors in the supply modulator circuit. The output of the supply modulator has shown that the output voltage dynamically changes with change in the input signal strength. This work thus, puts light on a very efficient method to modulate the supply voltage to the PA. The Envelope Tracking circuit was tested on a PA circuit and the results obtained are quite encouraging with a good efficiency of 66.3%, maximum saturated power equal to 28.21 dBm, power gain of 18.21dB and a PAE of 44.6%. The future work will focus on designing a PA suitable for this envelope tracking model so that the PAE can be further increased. Efforts will be towards designing PA by eliminating the transformer so as to reduce bulkiness and reduce chip area.

## Acknowledgements

NIL

#### **Nomenclature**

| G           | Generation                     |

|-------------|--------------------------------|

| CMOS        | Complementary Metal Oxide      |

|             | Semiconductor                  |

| nm          | Nano meter                     |

| RF          | Radio Frequency                |

| PA          | Power Amplifier                |

| GHz         | Giga Hertz                     |

| PAE         | Power Added Efficiency         |

| ET          | Envelope Tracking              |

| LTE         | Long Term Evolution            |

| MIMO        | Multiple input multiple output |

| OFDM        | Orthogonal Frequency Division  |

|             | Multiplexing                   |

| $C_0 - C_7$ | Comparator Outputs             |

| V           | Voltage                        |

| dBm         | Millimeter-decibel             |

| P           | Power                          |

| G           | Generation                     |

|             |                                |

# Greek symbols

$\mu s$  Unit of time

#### $\Omega$ unit of resistnce

| Subscripts |              |

|------------|--------------|

| pre        | Preamplifier |

| env        | envelope     |

| in         | input        |

| out        | output       |

| L          | detector     |

#### References

- Kumar, R. & Agarwal, A. Space Vector Modulation for Nine-Switch Converter Employing Three Phase Loads. Evergr. Jt. J. Nov. Carbon Resour. Sci. Green Asia Strateg. 10, 1034–1040 (2023). https://doi.org/10.5109/6793659

- Yadav, P., Upadhyay, A., Prasath, V. B. S., Ali, Z. & Khare, B. B. Evolution of Wireless Communications with 3G, 4G, 5G, and Next Generation Technologies in India. Lecture Notes in Electrical Engineering vol. 709 (Springer Singapore, 2021).

- 3) Solar Ruiz, H. & Berenguer Pérez, R. *Linear CMOS RF Power Amplifiers: A Complete Design Workflow*. (2014). doi:10.1007/978-1-4614-8657-2.

- 4) Utama, I., Hasian Aruan, Y. R., Rochmawati, Sari, R. F. & Harwahyu, R. 5G MMWave Network Performance Evaluation with Blockage Simulation. Evergreen 9, 1236–1243 (2022). https://doi.org/10.5109/6625735

- Juneja, S., Pratap, R. & Sharma, R. Semiconductor technologies for 5G implementation at millimeter wave frequencies – Design challenges and current state of work. *Eng. Sci. Technol. an Int. J.* 24, 205– 217 (2021).

- Mukai, K., Okabe, H. & Tanaka, S. Recent Progress in Envelope Tracking Power Amplifiers for Mobile Handset Systems. *IEICE Trans. Electron.* E104.C, 516–525 (2021).

- Kim, E. J., Kim, H., Cho, C. H., Lee, C. H. & Laskar, J. A switching frequency modulated DC-to-DC converter with reduced spurious noise for a RF power amplifier in microwatts transmitters. *Analog Integr. Circuits Signal Process.* 107, 263–272 (2021).

- 8) Shrestha, R., Van Der Zee, R., De Graauw, A. & Nauta, B. A wideband supply modulator for 20 MHz RF bandwidth polar PAs in 65 nm CMOS. *IEEE J. Solid-State Circuits* 44, 1272–1280 (2009).

- Ge, T. et al. Envelope Tracking RF Power Amplifiers: Fundamentals, Design Challenges, and Unique Opportunities Offered by LEES-SMART InGaAs-on-CMOS Process. Procedia Eng. 141, 94–97 (2016).

- 10) Wu, K. et al. A New Wide-Bandwidth Hybrid Supply Modulator for LTE-A Power Amplifiers. in International Conference on Applied System Innovation: Applied System Innovation for Modern Technology 1387–1390 (Institute of Electrical and

- Electronics Engineers Inc., 2017).

- 11) Dhandapani, V., Mishra, A. K., Thakur, R., Chopra, U. & J, B. P. Performance Analysis of Pulse Triggered Flip-Flop. *Evergr. Jt. J. Nov. Carbon Resour. Sci. Green Asia Strateg.* 10, 1010–1016 (2023). https://doi.org/10.5109/6793656

- 12) Jain, A., Kumar, C. S. & Shrivastava, Y. Fabrication and Machining of Fiber Matrix Composite through Electric Discharge Machining: A short review. *Mater. Today Proc.* 51, 1233–1237 (2021).

- 13) Sahi, N. & Bharti, M. Design and Implementation of Soft Error Resilient 14T SRAM Cell. Evergr. Jt. J. Nov. Carbon Resour. Sci. Green Asia Strateg. 10, 1100–1105 (2023). https://doi.org/10.5109/6793669

- 14) Khaleqi Qaleh Jooq, M., Mir, A., Mirzakuchaki, S. & Farmani, A. Design and performance analysis of wrap-gate CNTFET-based ring oscillators for IoT applications. *Integration* 70, 116–125 (2020).

- 15) Kajal & Vijay Kumar Sharma. FinFET: A Beginning of Non-planar Transistor Era. in *Nanoscale VLSI Devices, Circuits and Applications* 139–159 (Springe Nature Singapore, 2020). doi:10.1007/978-981-15-7937-0.

- 16) Wu, K. Da et al. A new wide-bandwidth hybrid supply modulator for LTE-A power amplifiers. Proc. 2017 IEEE Int. Conf. Appl. Syst. Innov. Appl. Syst. Innov. Mod. Technol. ICASI 2017 1387–1390 (2017) doi:10.1109/ICASI.2017.7988166.

- 17) Vasjanov, A. & Barzdenas, V. A review of advanced CMOS RF power amplifier architecture trends for low power 5G wireless networks. *Electron.* 7, (2018).

- 18) Lee, C.-I., Lin, W.-C. & Lin, Y.-T. A 2.4GHz high output power and high efficiency power amplifier operating at inductive breakdown in CMOS technology. *Microelectronics J.* 45, 449–453 (2014).

- 19) Hassan, M., Larson, L. E., Leung, V. W. & Asbeck, P. M. A Combined Series-Parallel Hybrid Envelope Ampli fi er for Envelope Tracking Mobile Terminal RF Power Ampli fi er Applications. *IEEE J. Solid-State Circuits* 47, 1185–1198 (2012).

- 20) Alsahali, S. *et al.* Modulated rapid load pull system for the emulation of envelope tracking power amplifiers. *Electron. Lett.* 56, 325–328 (2020).

- 21) Kimball, D. *et al.* Efficient and wideband envelope amplifiers for envelope tracking and polar transmitters. *PAWR 2013 Proc. 2013 IEEE Top. Conf. Power Amplifiers Wirel. Radio Appl. 2013 IEEE Radio Wirel. Week, RWW 2013* 13–15 (2013) doi:10.1109/PAWR.2013.6490173.

- 22) Kang, D. *et al.* Envelope-Tracking CMOS power amplifier module for LTE applications. *IEEE Trans. Microw. Theory Tech.* 61, 3763–3773 (2013).

- 23) Kim, D. *et al.* Optimization for envelope shaped operation of envelope tracking power amplifier. *IEEE Trans. Microw. Theory Tech.* 59, 1787–1795 (2011).

- 24) Askari, S., Nourani, M. & Namazi, A. Fault-tolerant A/D converter using analogue voting. *IET Circuits*,

- Devices Syst. 5, 462-470 (2011).

- 25) Lubaszewski, M., Mir, S., Kolarik, V., Nielsen, C. & Courtois, B. Design of self-checking fully differential circuits and boards. *IEEE Trans. Very Large Scale Integr. Syst.* 8, 113–128 (2000).

- 26) Maassen, D. et al. An 60 w average power wideband amplifier with envelope tracking for DVB-T applications. Eur. Microw. Week 2016 'Microwaves Everywhere', EuMW 2016 Conf. Proceedings; 46th Eur. Microw. Conf. EuMC 2016 823–826 (2016) doi:10.1109/EuMC.2016.7824470.

- 27) Casañas, C. W. V., Souza, G. A. F., Saotome, O. & Moreno, R. L. Low power current comparator circuit using a cascode transistor structure for bias generation. *Microelectronics J.* 121, 105359 (2022).

- 28) Bhardwaj, S., Moallemi, S. & Kitchen, J. A Linearity Enhancement Technique for Envelope Tracked Cascode Power Amplifier. in *IEEE Texas Symposium on Wireless and Microwave Circuits and Systems* (2020).

- 29) Kayyil, A. V., Qiao, B. & Allstot, D. J. Linearity improvement techniques for CMOS switched-capacitor power amplifiers. *Proc. IEEE Int. Symp. Circuits Syst.* 2021-May, 1–5 (2021).