## 九州大学学術情報リポジトリ Kyushu University Institutional Repository

Enhanced mobility of Sn-doped Ge thin-films (≤50 nm) on insulator for fully depleted transistors by nucleation-controlled solid-phase crystallization

Xu, Chang Department of Electronics, Kyushu University

Gong, Xiangsheng

Department of Electronics, Kyushu University

Miyao, Masanobu Department of Electronics, Kyushu University

Sadoh, Taizoh

Department of Electronics, Kyushu University

https://hdl.handle.net/2324/7172262

出版情報: Applied Physics Letters. 115 (4), pp.042101-, 2019-07-23. AIP Publishing

バージョン:

権利関係: © 2019 Author(s).

# **Enhanced mobility of Sn-doped Ge thin-films** ( $\leq$ 50 nm) on insulator for fully depleted transistors by nucleation-controlled solid-phase crystallization

Cite as: Appl. Phys. Lett. 115, 042101 (2019); doi: 10.1063/1.5096798 Submitted: 19 March 2019 · Accepted: 7 July 2019 · Published Online: 23 July 2019

Chang Xu, Xiangsheng Gong, Masanobu Miyao, and Taizoh Sadoh<sup>a)</sup> 🙃

### **AFFILIATIONS**

Department of Electronics, Kyushu University, 744 Motooka, Fukuoka 819-0395, Japan

a) Electronic mail: sadoh@ed.kyushu-u.ac.jp

### **ABSTRACT**

High-speed fully depleted thin-film transistors (TFTs) for low-power consumption are required for next-generation electronics, such as three-dimensional large-scale integrated circuits and advanced system-in-displays. For this purpose, high-carrier-mobility semiconductor thin-films (thickness:  $\leq \sim 50$  nm) on insulator structures should be fabricated under low-temperature processing conditions ( $\leq 500$  °C). To achieve this, solid-phase crystallization of amorphous GeSn (a-GeSn) with low Sn concentration (2%) is investigated for a wide range of film thicknesses (30 - 200 nm), where thin a-Si underlayers (thickness: 0 - 20 nm) are introduced between a-GeSn films and substrates. GeSn is polycrystallized by annealing at 450 °C, keeping Si underlayers amorphous. Crystal grains of almost identical sizes are obtained for GeSn thicknesses of 30 - 50 nm, though grain sizes significantly decrease for thicknesses exceeding 50 nm owing to enhanced bulk nucleation. A detailed analysis of GeSn films (thickness: 50 nm) reveals that grain sizes are decreased by introducing a-Si underlayers (thickness: 3-20 nm), e.g., from  $\sim 10 \, \mu \text{m}$  to  $2-3 \, \mu \text{m}$ . This phenomenon is attributed to the change in dominant nucleation sites from the interface to the bulk, which significantly decreases grain-boundary scattering of carriers through a decrease in the barrier heights at grain boundaries. As a result, a high carrier mobility of  $200 - 300 \,\mathrm{cm^2/V}$  s is realized for GeSn thin-films (thickness:  $30 - 50 \,\mathrm{nm}$ ) grown with a-Si underlayers. The mobility  $(200 - 300 \text{ cm}^2/\text{V s})$  is the largest ever reported data for Ge and GeSn thin-films (thickness: 30 - 50 nm) grown at low temperatures (≤500 °C). This technique will facilitate the realization of high-speed fully depleted TFTs for next-generation electronics.

Published under license by AIP Publishing. https://doi.org/10.1063/1.5096798

Germanium is attracting much attention as channel materials for high-speed transistors, owing to its higher carrier mobility compared with Si. 1-5 To realize next-generation electronics, such as threedimensional large-scale-integrated circuits (3D-LSIs) and advanced system-in-displays, Ge thin-film transistors (TFTs) should be fabricated on an insulator at low temperatures (≤500 °C). Thus, the lowtemperature formation of Ge-on-insulator (GOI) is a hot topic for semiconductor processing.<sup>6,7</sup> To achieve high speed and low-power operation, the development of fully depleted TFTs is desired. For this purpose, Ge thin-films with thicknesses below  $\sim$ 50 nm are required.

Various formation methods, e.g., metal-induced lateral crystallization (MILC),<sup>8,9</sup> melt-growth by laser-annealing (LA),<sup>10,11</sup> flashlamp annealing (FLA), 12 and solid-phase crystallization (SPC), 13,14 have been investigated to obtain high quality GOIs. Among them, SPC has the advantages of no metal contamination or melting-induced surface ripple. These are very important advantages for high-density integration of TFTs.

We have therefore developed two-step SPC of amorphous Ge (a-Ge), i.e., 425 °C growth followed by 500 °C annealing, enabling independent control of grain growth and defect annihilation. This yields a GOI (Ge thickness: 50 nm) with a mobility of 140 cm<sup>2</sup>/V s.<sup>14</sup> Although this value is higher than that  $(\leq \sim 20 \text{ cm}^2/\text{V s})$  of oxide<sup>15</sup> and organic semiconductors, <sup>16</sup> the improvement in mobility ( $\geq 200 \,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s}$ ) is needed for the application of not only display-pixel drivers but also advanced electronic circuits such as information processors. Recently, Imajo et al. investigated the densification of a-Ge on GeO2-coated substrates by substrate heating during Ge-deposition and obtained poly-Ge thick films (thickness: 500 nm) with high mobility (620 cm<sup>2</sup>/V s).<sup>17</sup> However, owing to their large thickness (500 nm), the films cannot be used for fully depleted transistors.

On the other hand, Sn-doping into Ge is attracting much attention.  $^{18-20}$  An important effect of Sn doping is the passivation of vacancy-related defects. Nakatsuka *et al.*<sup>21</sup> reported that the introduction of a small amount of Sn ( $\sim$ 2%) eliminates vacancy-related defects in Ge. Takeuchi *et al.*<sup>22</sup> investigated the effects of Sn-doping on mobility in poly-GeSn (thickness: 300 nm) grown by SPC (450 °C) and demonstrated mobility improvement from 30 to 130 cm²/V s by Sn doping (2%).

We comprehensively investigated SPC of a-GeSn on an insulator (fused quartz substrates) and clarified that the competition between interface nucleation and bulk nucleation significantly affects the electrical properties of grown films. Consequently, we achieved high mobility (320 cm²/V s) by selecting a Sn concentration (2%) and thickness (200 nm) to control competition between them. However, in this previous study, mobility still degraded near insulating substrates ( $\leq \sim 120$  nm). This indicates that crystal grains initiated from interface nucleation degrade mobility.

For the realization of fully depleted transistors with high mobility, mobility in Ge thin-films (thickness:  $\leq\!50\,\text{nm}$ ) should be improved. The above-mentioned finding in our previous study^2³ leads to an idea that mobility can be improved by suppressing interface nucleation. Here, interface nucleation can be modulated by changing the interface energy. Because the interface energy of two materials depends on the surface energy of the respective materials,²⁴ interface energy can be changed by the surface energy of the substrates. The surface energy of fused quartz ( $\sim\!70$  mJ/m²)²⁵ is significantly smaller compared with Ge (1.1 – 1.8 J/m²).²⁶ However, a-Si has a surface energy ( $\sim\!1$  J/m²)²⁻ similar to that of Ge. Thus, introduction of a-Si underlayers into a-GeSn/ substrate interfaces will modulate interface nucleation in a-GeSn.

To examine this, in the present study we investigate the effects of introducing a-Si underlayers into a-GeSn/substrate interfaces on SPC characteristics and the electrical properties of grown films. We clarify that introduction of a-Si underlayers effectively suppresses interface nucleation. Consequently, poly-GeSn having very high mobility ( $\sim$ 300 cm<sup>2</sup>/V s), which is the highest ever among reported data on Ge and GeSn thin-films (thickness:  $\leq$ 50 nm) grown at low temperatures ( $\leq$ 500 °C),  $^{12,14,23}$  is achieved.

In the experiment, a-Si (thickness: 0-20 nm) and a-GeSn (Sn concentration: 2%, thickness: 30-200 nm) were deposited on fused quartz substrates at room temperature using a molecular-beam deposition system (base pressure:  $\sim 5 \times 10^{-10}$  Torr), then they were annealed at 350 °C for 10 min in the deposition chamber without breaking a vacuum. The sample structure is shown in Fig. 1. The samples were annealed (450 °C, 1-40 h) to induce SPC in the nitrogen environment using an electric furnace, where the sample temperatures were controlled using a thermocouple attached to the sample holder.

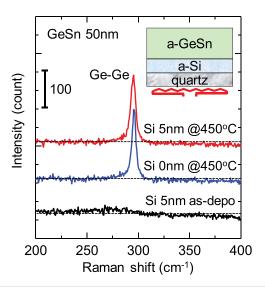

The crystallinity of the grown layers was investigated using Raman spectroscopy. Raman spectra of samples (GeSn thickness: 50 nm, Si thickness: 5 nm) before and after annealing (450 °C, 20 h) are shown in Fig. 1, together with the data on an annealed sample without a Si underlayer. After annealing, Raman peaks caused by Ge-Ge bonding in crystalline GeSn are observed. The spectra shown in Fig. 1 were obtained from the top-side of samples, and similar spectra were obtained from the top-side of other samples (Si thickness: 3, 10, and 20 nm). In addition, similar spectra were obtained from the back-side of samples through transparent substrates for all samples (Si thickness:

**FIG. 1.** Raman spectra of samples (GeSn thickness: 50 nm, Si thickness: 0 and 5 nm) before and after annealing (450  $^{\circ}$ C, 20 h). Raman measurements were performed from the top-side of the samples. The inset shows a schematic initial sample structure. The dotted lines show the baselines of the respective spectra.

0-20 nm), and no peaks due to crystalline Si or SiGe were detected. This indicates that Si underlayers remain amorphous, and intermixing with GeSn is not generated by annealing for samples with a wide range of Si thicknesses (3-20 nm).

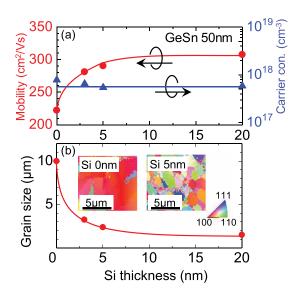

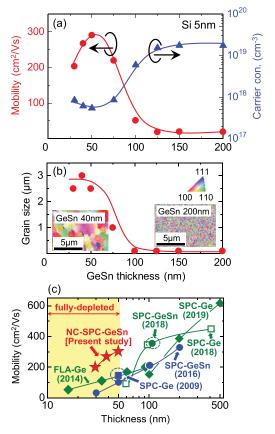

Electrical properties of grown GeSn layers were evaluated using Hall effect measurements. The measurements indicated p-type conduction for all samples, which was attributed to acceptor levels of vacancy-related defects in Ge.  $^{28,29}$  The mobility and the carrier concentration in grown films (GeSn thickness: 50 nm) are summarized as a function of Si thickness in Fig. 2(a). The mobility of samples with a-Si underlayers (thickness:  $3-20\,\mathrm{nm}$ ) becomes high  $(280-300\,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s})$  compared with that without an a-Si underlayer ( $\sim\!220\,\mathrm{cm}^2/\mathrm{V}\,\mathrm{s})$ ). However, carrier concentrations are constant ( $\sim\!5\times10^{17}\,\mathrm{cm}^{-3}$ ) for all samples with or without a-Si underlayers in a wide range of a-Si thicknesses (0 $-20\,\mathrm{nm}$ ). Because holes in grown films are generated from vacancy-related defects,  $^{28,29}$  this result indicates that concentrations of vacancy-related defects in grown films are not changed by introduction of a-Si underlayers.

Grain structures were analyzed using electron backscattering diffraction (EBSD) measurements. Grain sizes for samples (GeSn thickness: 50 nm) are summarized as a function of a-Si underlayer thickness in Fig. 2(b), where typical EBSD images (Si thickness: 0 and 5 nm) are also shown. Grain sizes decreased from  $\sim\!10$  to  $2-3\,\mu\mathrm{m}$  upon introducing a-Si underlayers (thickness: 3-20 nm). Simultaneously, preferentially (100)-oriented grains for the sample without an a-Si underlayer change into randomly oriented grains, as shown in the EBSD images. This suggests that preferentially oriented interface nucleation is suppressed by the modulation of the interface energy through the introduction of a-Si underlayers, which makes randomly oriented bulk nucleation dominant. Interestingly, these results indicate that randomly oriented small-grain films of samples with a-Si underlayers show higher mobility than the preferentially oriented large-grain film of the sample without an a-Si underlayer.

**FIG. 2.** Si underlayer thickness dependence of (a) carrier mobility and carrier concentration and (b) grain size for samples (GeSn thickness:  $50 \, \text{nm}$ ) after annealing ( $450 \,^{\circ}\text{C}$ ,  $20 \, \text{h}$ ). EBSD images of the samples (Si thickness:  $0 \, \text{and} \, 5 \, \text{nm}$ ) are also shown in (b).

Figure 2 indicates that the carrier mobility and grain sizes weakly depend on the a-Si thickness in the region of  $3-5\,\mathrm{nm}$ . One possible reason is the local mixing of very thin a-Si films and GeSn films, which results in local direct contact of GeSn with the quartz substrates. However, no Raman peaks due to Si-Ge bonding were detected by Raman measurements. Further investigation is needed to reveal these phenomena.

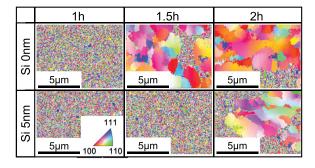

To demonstrate that interface nucleation is retarded by the introduction of a-Si underlayers, crystal structures were investigated after short-time annealing. EBSD images (GeSn thickness: 50 nm, Si thickness: 0 and 5 nm) after annealing (450 °C) for 1, 1.5, and 2 h are shown in Fig. 3. It is noted that randomly colored small dots observed in the EBSD images for the sample without an a-Si underlayer (annealing time: 1 h) and the samples with an a-Si underlayer (annealing time: 1 and 1.5 h) were caused by errors in identifying the orientation of the EBSD analysis, and similar small dots were observed for a-GeSn films before annealing. For the sample without an a-Si underlayer,

**FIG. 3.** EBSD images of samples (GeSn thickness: 50 nm) with different Si underlayer thicknesses (0 and 5 nm) after annealing at 450 °C for 1, 1.5, and 2 h.

preferentially (100)-oriented grains are observed from an annealing time of 1.5 h, where almost the whole area is covered with large crystal grains. However, a long annealing time (2 h) is required to detect crystal grains for the sample with an a-Si underlayer. Here, randomly oriented grains are dominant. Moreover, the fraction of the surface area covered with crystal grains for the sample (annealing time: 2 h) with an a-Si underlayer is smaller than that without an a-Si underlayer. These results clearly indicate that interface nucleation, dominant for the sample without an a-Si underlayer, is suppressed by the introduction of a-Si underlayers. Here, grain sizes become small by introducing a-Si underlayers, though nucleation becomes slow. This suggests that the areal density of interface nucleation is lower than that of bulk nucleation, and grain growth from interface nucleation is almost complete before bulk nucleation started.

To reveal the mechanism of mobility improvement, the electrical properties of grain boundaries are analyzed using a model proposed by Seto.<sup>30</sup> The mobility  $\mu$  of polycrystalline semiconductors is expressed by the following equation:<sup>30</sup>

$$\mu = \frac{Lq}{\sqrt{2\pi m^* kT}} \exp\left(-\frac{E_B}{kT}\right),\tag{1}$$

where L is the crystal grain size, q the elementary charge,  $m^*$  the effective mass of carrier, k the Boltzmann constant, T the absolute temperature, and  $E_B$  the energy barrier height at grain boundaries. Here, the energy barrier height  $E_B$  is generated by trapping states with density  $Q_t$  at grain boundaries, and is given by the following equation:<sup>30</sup>

$$E_B = \frac{q^2 Q_t^2}{8\varepsilon N},\tag{2}$$

where  $\varepsilon$  is the dielectric constant of the semiconductor and N the carrier concentration.

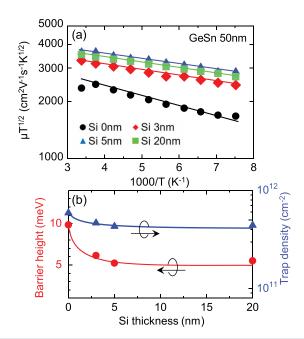

Figure 4(a) shows the Arrhenius plot of  $\mu T^{1/2}$  (GeSn thickness: 50 nm, Si thickness: 0, 3, 5, and 20 nm). Respective data are fitted with straight lines, where slopes of lines are decreased for samples introduced with a-Si underlayers. From the slopes, the energy barrier height  $E_B$  is evaluated using Eq. (1), and the trapping state density  $Q_t$  is evaluated from  $E_B$  using Eq. (2).  $E_B$  and  $Q_t$  are summarized in Fig. 4(b).  $E_B$  for the sample without an a-Si underlayer is  $\sim$ 10 meV. The values significantly decreased to ~5 meV upon introducing a-Si underlayers. The figure also shows that  $Q_t$  decreased from  $\sim 6 \times 10^{11}$  to  $\sim 4$  $\times$  10<sup>11</sup> cm<sup>-2</sup> upon introducing a-Si underlayers. These findings reveal that mobility improvement by the introduction of a-Si underlayers is caused by a significant decrease in energy barrier heights at grain boundaries because of a decrease in trapping state densities. Because bulk nucleation becomes dominant over interface nucleation by the introduction of a-Si underlayers, as revealed in Fig. 3, these results indicate that the boundaries of crystal grains initiated from interface nucleation show a higher density of trapping states compared with bulk nucleation. Further investigation is necessary to clarify the reason.

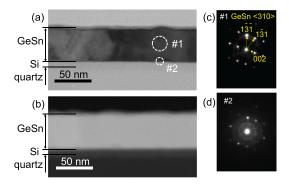

Crystal structures were investigated in more detail by transmission electron microscopy (TEM). Bright-field TEM and high-angle annular dark-field (HAADF) images of a sample (GeSn thickness: 50 nm, Si thickness: 5 nm) after annealing (450 °C, 20 h) are shown in Figs. 5(a) and 5(b), respectively. In addition, selected area electron diffraction (SAED) patterns obtained from regions #1 and #2 indicated in Fig. 5(a) are shown in Figs. 5(c) and 5(d), respectively. The SAED

**FIG. 4.** (a) Arrhenius plot of  $\mu T^{1/2}$  and (b) a-Si underlayer thickness dependence of the energy barrier height and the trapping state density at grain boundaries for samples (GeSn thickness: 50 nm, Si thickness: 0, 3, 5, and 20 nm) after annealing (450 °C, 20 h).

pattern shown in Fig. 5(c) indicates that the observed area consists of (131)-oriented crystal GeSn. However, the SAED pattern in Fig. 5(d) was obtained from region #2, where both GeSn and Si layers were included. The SAED pattern [Fig. 5(d)] consists of a diffraction pattern of (131)-oriented crystal GeSn and a halo pattern of amorphous Si. This indicates that Si underlayers remain amorphous, which agrees with the Raman measurement results.

The bright-field image [Fig. 5(a)] shows the flat top and bottom of the GeSn layer, and the HAADF image [Fig. 5(b)] indicates that Sn segregation, as reported for GeSn with a high Sn concentration ( $\geq$ 4.5%),<sup>31</sup> does not occur. These results clearly indicate that the

**FIG. 5.** (a) Bright-field TEM image, (b) HAADF image, and [(c) and (d)] SAED patterns of a sample (GeSn thickness: 50 nm, Si thickness: 5 nm) after annealing (450 °C, 20 h). The SAED patterns shown in (c) and (d) were obtained from regions #1 and #2, respectively, indicated by the circles in (a).

introduction of a-Si underlayers does not deteriorate surface morphologies of grown GeSn layers or generate Sn segregation.

For advanced fully depleted TFTs with short channel lengths ( $\leq 100$  nm), thinner GOI layers (thickness:  $\leq \sim 30$  nm) are required. Thus, we investigate the effects of GeSn thickness. The mobility and the carrier concentration of samples (GeSn thickness: 30-200 nm, Si thickness: 5 nm) are summarized as a function of GeSn thickness in Fig. 6(a). Upon decreasing GeSn thickness from 50 to 30 nm, mobility is decreased from  $\sim \! 300$  to  $\sim \! 200$  cm²/V s, which suggests that the carrier mobility is limited by the interface scattering in addition to the grain-boundary scattering. Further study is needed to separate these scattering mechanisms. In the GeSn thickness region of 30-50 nm, carrier concentrations are almost constant at  $\sim \! 5 \times 10^{17}$  cm $^{-3}$ . However, mobility is significantly decreased by increasing the GeSn

**FIG. 6.** GeSn thickness dependence of (a) mobility and carrier concentration and (b) grain size for samples (Si thickness: 5 nm) after annealing (450 °C), and (c) mobility of semiconductors grown on an insulator as a function of thickness. Annealing times for samples shown in (a) and (b) are 40 h (thickness: 30 nm) and 20 h (thickness: 40 – 200 nm). EBSD images of samples (GeSn thickness: 40 and 200 nm) are shown in (b). The mobility obtained in the present study [nucleation-controlled SPC (NC-SPC)] indicated by red symbols is compared with our previously reported data for SPC ( $\leq$ 500 °C) of pure a-Ge in 2009  $^{14}$  and a-GeSn (Sn concentration: 2%) in 2016  $^{23}$  indicated by blue symbols and other groups' data for SPC ( $\leq$ 500 °C) of pure a-Ge in 2013  $^{32}$  and 2019  $^{17}$  and a-GeSn (Sn concentration: 3%) in 2018,  $^{33}$  and FLA of pure-Ge in 2014  $^{12}$  indicated by green symbols in (c). The yellow hatching area in (c) indicates the thickness range for fully depleted transistors

thickness above 50 nm. Simultaneously, carrier concentrations are increased toward  ${\sim}2\times10^{19}\,\text{cm}^{-3}.$

Grain sizes of these samples, evaluated using EBSD, are summarized in Fig. 6(b), together with EBSD images (GeSn thickness: 40 and 200 nm). The grain sizes are almost constant  $(2.5-3\,\mu\text{m})$  for a GeSn thickness of 30-50 nm; however, they decreased below  $1\,\mu\text{m}$  for GeSn thicknesses above 50 nm due to the increase in areal densities of bulk nucleation with increasing GeSn thickness. These results explain well the decrease in mobility for GeSn thickness above 50 nm, shown in Fig. 6(a). However, the decrease in grain sizes for GeSn film thicknesses above 100 nm is very significant. Here, grain sizes ( $\sim$ 0.1  $\mu$ m) for GeSn thicknesses of 100-200 nm obtained in the present study are almost equal to that of a thicker sample (GeSn thickness: 500 nm) without an a-Si underlayer. This indicates that bulk nucleation becomes more dominant by the introduction of a-Si underlayers in the present study. Further study is needed to clarify details.

Figure 6(c) shows mobility obtained in the present study, and a comparison with the literature values for semiconductors directly grown on an insulator, 12,14,17,23,32,33 as a function of thickness, where data obtained by FLA12 are shown together with those by SPC (≤500 °C). Since 2009, many researchers have intensively studied the growth techniques of Ge thin-films on an insulator. These efforts significantly improve the mobility of Ge films from  $\sim 140^{14}$  to  $\sim$ 620 cm<sup>2</sup>/V s.<sup>17</sup> However, most previous works employed Ge films with thicknesses above 100 nm, and no improvement has been obtained for thicknesses below 50 nm, essential to fully depleted devices. Figure 6(c) clearly shows that the mobility obtained using the present technique is the highest among the literature for thin (≤50 nm) Ge<sup>12,14</sup> and GeSn<sup>22</sup> films. In addition, the values of mobility  $(200 - 300 \text{ cm}^2/\text{V s})$  are significantly higher than those ( $\leq \sim 20 \text{ cm}^2/\text{V s}$ ) of other TFT channel materials, such as oxide semiconductors<sup>15</sup> and organic semiconductors. <sup>16</sup> Thus, the present technique is applicable to high-performance electronic circuits directly fabricated on LSIs and glass panels.

In summary, we have developed nucleation controlled SPC of GeSn on an insulator. By low-temperature annealing (450 °C) of a-GeSn/a-Si/fused quartz stacking structures, GeSn layers are polycrystallized while keeping Si underlayers amorphous. Introduction of a-Si underlayers (thickness: 3 - 20 nm) suppresses interface nucleation in a-GeSn layers and makes bulk nucleation dominant over interface nucleation. Although this decreases grain sizes, e.g., from ~10 to  $2-3 \mu m$  for a GeSn thickness of 50 nm, the energy barrier height at grain boundaries is significantly decreased, which remarkably increases the mobility. These phenomena are attributed to lower trapping state densities at the boundaries of crystal grains initiated from bulk nucleation compared with interface nucleation. Consequently, a very high mobility of  $200 - 300 \,\mathrm{cm^2/V}$  s is realized for thin GeSn films (thickness: 30 - 50 nm). This technique will facilitate the realization of high-speed fully depleted TFTs for low-power consumption essential to next-generation electronics, such as 3D-LSIs and systems-indisplay.

The authors wish to thank Professor T. Asano of Kyushu University for providing opportunity to use the EBSD analysis system. Part of this work was supported by Grants-in-Aid (Nos.

JP25289089, JP26630133, JP15H03976, and JP16K14234) for Scientific Research from the Ministry of Education, Culture, Sports, Science, and Technology in Japan.

#### **REFERENCES**

- <sup>1</sup>M. Miyao, E. Murakami, H. Etoh, K. Nakagawa, and A. Nishida, J. Cryst. Growth 111, 912 (1991).

- <sup>2</sup>K. C. Saraswat, C. Chui, T. Krishnamohan, A. Nayfeh, and P. McIntyre, Microelectron. Eng. 80, 15 (2005).

- <sup>3</sup>R. Zhang, P.-C. Huang, J.-C. Lin, N. Taoka, M. Takenaka, and S. Takagi, IEEE Trans. Electron Devices **60**, 927 (2013).

- <sup>4</sup>C. H. Lee, T. Nishimura, T. Tabata, D. D. Zhao, K. Nagashio, and A. Toriumi, Appl. Phys. Lett. **102**, 232107 (2013).

- <sup>5</sup>A. Toriumi and T. Nishimura, Jpn. J. Appl. Phys., Part 1 57, 010101 (2018).

- <sup>6</sup>M. Miyao and T. Sadoh, Jpn. J. Appl. Phys., Part 1 56, 05DA06 (2017).

- <sup>7</sup>K. Toko, R. Yoshimine, K. Moto, and T. Suemasu, Sci. Rep. 7, 16981 (2017).

- <sup>8</sup>H. Kanno, K. Toko, T. Sadoh, and M. Miyao, Appl. Phys. Lett. **89**, 182120 (2006).

- <sup>9</sup>J.-H. Park, M. Tada, P. Kapur, H. Peng, and K. C. Saraswat, J. Appl. Phys. **104**, 064501 (2008).

- <sup>10</sup>H. Watakabe, T. Sameshima, H. Kanno, and M. Miyao, Thin Solid Films 508, 315 (2006).

- <sup>11</sup>W. Yeh, H. Chen, H. Huang, C. Hsiao, and J. Jeng, Appl. Phys. Lett. **93**, 094103 (2008).

- <sup>12</sup>K. Usuda, Y. Kamata, Y. Kamimuta, T. Mori, M. Koike, and T. Tezuka, Appl. Phys. Express 7, 056501 (2014).

- <sup>13</sup>S. Yamaguchi, N. Sugii, S. K. Park, K. Nakagawa, and M. Miyao, J. Appl. Phys. 89, 2091 (2001).

- <sup>14</sup>K. Toko, I. Nakao, T. Sadoh, T. Noguchi, and M. Miyao, Solid-State Electron. 53, 1159 (2009).

- <sup>15</sup>H. Hosono, Jpn. J. Appl. Phys., Part 1 52, 090001 (2013).

- <sup>16</sup>G. Kim, S.-J. Kang, G. K. Dutta, Y.-K. Han, T. J. Shin, Y.-Y. Noh, and C. Yang, J. Am. Chem. Soc. **136**, 9477 (2014).

- <sup>17</sup>T. Imajo, K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Appl. Phys. Express 12, 015508 (2019).

- <sup>18</sup>S. Gupta, B. Magyari-Köpe, Y. Nishi, and K. C. Saraswat, J. Appl. Phys. 113, 073707 (2013).

- <sup>19</sup>S. Wirths, R. Geiger, N. von den Driesch, G. Mussler, T. Stoica, S. Mantl, Z. Ikonic, M. Luysberg, S. Chiussi, J. M. Hartmann, H. Sigg, J. Faist, D. Buca, and D. Grützmacher, Nat. Photonics 9, 88 (2015).

- <sup>20</sup>C. Chang, T.-W. Chang, H. Li, H. H. Cheng, R. Soref, G. Sun, and J. R. Hendrickson, Appl. Phys. Lett. 111, 141105 (2017).

- <sup>21</sup>O. Nakatsuka, N. Tsutsui, Y. Shimura, S. Takeuchi, A. Sakai, and S. Zaima, Jpn. J. Appl. Phys., Part 1 49, 04DA10 (2010).

- <sup>22</sup>W. Takeuchi, N. Taoka, M. Kurosawa, M. Sakashita, O. Nakatsuka, and S. Zaima, Appl. Phys. Lett. 107, 022103 (2015).

- <sup>23</sup>T. Sadoh, Y. Kai, R. Matsumura, K. Moto, and M. Miyao, Appl. Phys. Lett. 109, 232106 (2016).

- <sup>24</sup>F. M. Fowkes, Ind. Eng. Chem. **56**, 40 (1964).

- <sup>25</sup>I. Zgura, R. Moldovan, C. C. Negrila, S. Frunza, V. F. Cotorobai, and L. Frunza, J. Optoelectron. Adv. Mater. 15, 627 (2013).

- <sup>26</sup>R. J. Jaccodine, J. Electrochem. Soc. **110**, 524 (1963).

- <sup>27</sup>S. Hara, S. Izumi, T. Kumagai, and S. Sakai, Surf. Sci. 585, 17–24 (2005).

- <sup>28</sup>E. A. Fitzgerald and S. B. Samavedam, Thin Solid Films **294**, 3 (1997).

- <sup>29</sup>H. Yang, D. Wang, and H. Nakashima, Appl. Phys. Lett. **95**, 122103 (2009).

- 30 J. Y. W. Seto, J. Appl. Phys. 46, 5247 (1975).

- 31Y. Shimura, N. Tsutsui, O. Nakatsuka, A. Sakai, and S. Zaima, Jpn. J. Appl. Phys., Part 1 48, 04C130 (2009).

- <sup>32</sup>R. Yoshimine, K. Moto, T. Suemasu, and K. Toko, Appl. Phys. Express 11, 031302 (2018).

- 33K. Moto, R. Yoshimine, T. Suemasu, and K. Toko, Sci. Rep. 8, 14832 (2018).