# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# A New Method of The Active Gate Driver for Current Balancing in The Parallel MOSFET Circuits

# Meiyanto Eko Sulistyo

Department of Electrical Engineering, Universitas Sebelas Maret

# Kaleg, Sunarto

Research Center for Transportation Technology, National Research and Innovation Agency, Indonesia

## Damaris Adi Waskitho

Department of Electrical Engineering, Universitas Sebelas Maret

# Ristiana, Rina

Research Center for Transportation Technology, National Research and Innovation Agency, Indonesia

他

https://doi.org/10.5109/7151765

出版情報: Evergreen. 10 (3), pp. 1997-2005, 2023-09. 九州大学グリーンテクノロジー研究教育セン

ター

バージョン:

権利関係: Creative Commons Attribution-NonCommercial 4.0 International

# A New Method of The Active Gate Driver for Current Balancing in The Parallel MOSFET Circuits

Meiyanto Eko Sulistyo<sup>1,\*</sup>, Sunarto Kaleg<sup>2</sup>, Damaris Adi Waskitho<sup>1</sup>, Rina Ristiana<sup>2</sup>, Aam Muharam<sup>2</sup>, Alexander Christantho Budiman<sup>2</sup>, Sudirja<sup>2</sup>, Amin<sup>2</sup>, Kristian Ismail<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Universitas Sebelas Maret, Indonesia <sup>2</sup>Research Center for Transportation Technology, National Research and Innovation Agency, Indonesia

> \*Author to whom correspondence should be addressed: E-mail: mekosulistyo@staff.uns.ac.id

(Received May 8, 2023; Revised September 15, 2023; accepted September 22, 2023).

Abstract: MOSFETs are used in electronic circuits because they have high switching efficiency. Typically, MOSFETs are wired in parallel for applications that require high power. Theoretically, this circuit can multiply the current capability of parallel MOSFETs. However, even if all the MOSFETs in a parallel circuit have the same serial number and manufacturer, they might not necessarily have the same current characteristics. This could lead to issues with current imbalances, potentially causing harm to the MOSFETs, especially under severe circumstances. This study introduces a new Active Gate Driver (AGD) technique to balance the current in a parallel MOSFET circuit. The current difference can be used to modulate each MOSFET duty cycle. Specifically, the MOSFET with the smallest current capacity is configured as the Master, while the MOSFET following it is designated as the Slave. The interrupt time value for the duty cycle of each Slave MOSFET is influenced by the current differential between the Master and Slave. Consequently, different duty cycles for the Master and Slave MOSFETs can maintain the same current level. Based on the results of experiments conducted on three MOSFETs, it is evident that the AGD approach can effectively balance the current to an optimum level.

Keywords: Active gate driver; Current imbalance; MOSFET; Parallel circuit

# 1. Introduction

The development of electronic technology plays an important role in supporting a majority demand in various sectors, ranging from industry1), household needs, renewable energy2), electrical machines drivers3), and transportation<sup>4)</sup>. This development requires high-power and reliable electronic components. Sometimes, these power electronic components should function properly in harsh environments and have greater capabilities than other applications<sup>4-7)</sup>. Recently, MOSFETs have shown potential for high-power applicants due to high switching efficiency, high input impedance, fast switching speed, and low on-state resistance<sup>8-12)</sup>. However, sometimes a single MOSFET cannot withstand the high current, so multiple MOSFETs need to be assembled in parallel to increase current handling capability and improve reliability and system efficiency<sup>8,9,13-24)</sup>. A current imbalance phenomenon may occur in the parallel assembly MOSFET due to the difference in the characteristics of devices, inconsistencies in the parasitic loop parameters and the aging degree of the components. The current imbalance produces differentiation in transient current stress, power loss, and junction temperature among the MOSFETs, which affects a decline in device performance, increased thermal failure, and potentially leads to device failure<sup>1,11,14-16,25-29</sup>). Therefore, the evenly current share control for parallel assembly MOSFETs is required. In recent years, several MOSFET driver methods have been studied to solve this issue. One of these methods is known as Active Gate Driver (AGD). However, there are still some challenges that need to be addressed.

The AGD is a sophisticated control technique used to enhance the switching performance of semiconductors, including MOSFETs. The AGD involves external driver circuitry that precisely controls the voltage applied to the MOSFET gate terminal, enabling rapid and precise switching. It overcomes the limitations of conventional passive gate driving methods by providing higher voltage slew rates, reduced switching losses, and improved efficiency. The AGD operates by utilizing high-speed transistors and capacitors to efficiently drive the MOSFET gate capacitance, resulting in faster switching transitions

and minimized high-impedance states. The primary objective is to achieve precise and predictable switching characteristics, leading to improved power conversion efficiency and reduced switching losses. AGD's responsiveness to dynamic load changes makes it suitable for high-frequency applications, maintaining reliable performance while enabling higher switching frequencies. In summary, AGD plays a crucial role in enhancing MOSFET performance, offering significant benefits in various applications, such as power electronic systems, motor drives, inverters, and switching power supplies<sup>6,7,11)</sup>.

Furthermore, AGD can be applied to solve the current imbalance in parallel MOSFET configurations. The AGD with the derating method idea is lowering the MOSFET rating performance to protect against potential overcurrent, even though it wastes the MOSFET potential<sup>13</sup>). The AGD method for gate control manipulation is a good current balancing technique with very small power loss, but it cannot guarantee consistent MOSFET performance in high-current applications 14,19,20). Reference 15) describes an AGD method that involves MOSFET oscillation and overshooting reduction. However, this method increases losses in MOSFET switching. The Master and Slave method presented in 16,18) is an effective method to control current imbalances. However, the interrupt signal, which requires the use of a traditional operational amplifier circuit-based approach, may also have a higher susceptibility to electrical noise. This can degrade the performance of the control circuit and have a negative impact on the driver's reliability. Analog current-sharing methods use analog control with sensors and feedback control to adjust the gate voltage of each MOSFET to balance the current. This method makes the system more complex and more sensitive to other disturbances, especially noise, which can result in fluctuations in the control signal and compromise the accuracy of the current balance processing<sup>17,24,32-34)</sup>. The AGD method dynamically regulates the MOSFET gate voltage to synchronize with the peak of drain current (Id) in each MOSFET on a closed-loop circuit. However, this approach leads to a significant gate time delay and requires a complex digital process<sup>21-24,35)</sup>.

This study describes a new MOSFET Active Gate Driver (AGD) method with the aim of achieving the same Id current with different PWM duty cycles or Ton on each MOSFET. The difference in each MOSFET current is used to regulate the PWM duty cycle of every MOSFET. The PWM duty cycle regulates the turning ON (which is defined as a Ton) and the turning OFF (Toff) of the MOSFET switching, thus influencing the current flow (Id) through it 15). The MOSFET with the smallest current capability is configured as the Master, whereas the other MOSFETs are designated as Slaves. The interrupt time value for the duty cycle of each Slave MOSFET is influenced by the current difference between the Master and Slaves. As a result, the duty cycles of the Slave MOSFETs can vary and be adjusted to balance the current

flowing through each MOSFET.

## 2. Operation Principles and Methods

MOSFETs commonly use Pulse-Width Modulation (PWM) to determine Ton and Toff voltage supplies to control the average current delivered to a load. The PWM duty cycle represents the duration of the MOSFET that is in the active state during the switching process. It is directly proportional to the MOSFET current flow. When the duration of MOSFET operation in an active mode increases, the drain current of the MOSFET also increases. Consequently, an increase in the duty cycle results in a corresponding increase in the drain current, while a decrease in the duty cycle leads to a decrease in the drain current 21,32,36-40). Reference 34) explains that the correlation between the PWM duty cycle and Id (drain current) can be calculated by considering the internal characteristics of each MOSFET, as shown in Eq. 1. In the context of this research, the gate voltage (Vgs) was maintained at 12 Vdc, where Vth represents the voltage threshold of the MOSFET.

$$Id = \frac{((Vgs - Vth)xdtyxTtotal x Gms)}{(Rtotal x Ciss)}$$

(1)

Ciss is the total capacitance of the MOSFET as seen from the input, obtained by summing the capacitance of the gate-source (Cgs) and the capacitance of the gate-drain (Cgd)<sup>29-32)</sup>. Gms signifies the transconductance parameter inherent to the MOSFET<sup>22)</sup>. The duty cycle of the PWM signal (dty) is a measure of the proportion of time the signal remains in the high state relative to its entire period. Meanwhile, the total switching time (Ttotal) depends on the microcontroller or PWM frequency used. In this study, a frequency of 8kHz was utilized, resulting in a total switching time of 125 µS. The total resistance (Rtotal) in the formulated equation includes not only the resistance of the load but also any other resistive elements within the circuit. Consistent with Eq. 1, the outcome of " dtyxTtotal " actually signifies the Ton (Turn-On Time) of the MOSFET switching process. Consequently, Id can be computed during switching events based on the Ton of the MOSFET.

$$Id = \frac{((Vgs - Vth)x Ton x Gms)}{(Rtotal x Ciss)}$$

(2)

However, Eq. 2 used to calculate Id during switching events is typically more complex, as it depends on other factors such as load conditions and gate driver characteristics<sup>29)</sup>. Furthermore, in this study, the manipulation and variation of Ton are crucial for achieving current balancing among individuals of each MOSFET. This dynamic control of Ton allows for precise current regulation and optimization, ensuring that each MOSFET carries an equal share of the load current.

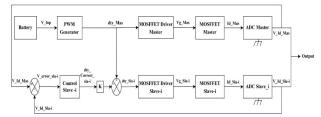

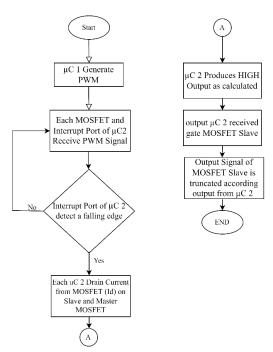

Fig. 1: Control Diagram of Current Balancing Process.

Fig. 1 shows a control diagram of MOSFETs current regulation. The current through the MOSFETs drain of Slave-i (i=1,2,...,n) is regulated until it reaches the same current as the Master. The comparison between two output voltages from ADC Master and Slave-i is used to program the feedback of MOSFET driver Slave-i. The program is compiled in a certain microcontroller to enable control PWM duty correction. The PWM duty cycle (dty) of each Slave-i MOSFET will reduced if the current sensor reading indicates a higher current flow through the MOSFET of Slave-i than the Master MOSFET.

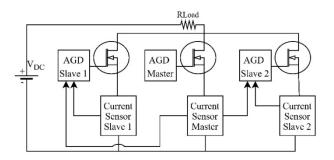

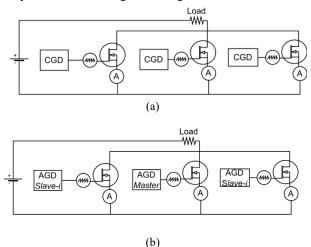

**Fig. 2:** Circuit Configuration of MOSFETs Parallel Connection.

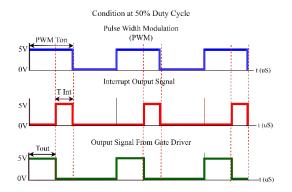

Fig. 3: Interrupt Scheme for Reducing PWM Duty Cycle.

The key idea of the proposed driving system is shown in Fig. 2. At first, a typical test circuit with three parallel MOSFETs is set up, where the drain current (Id) of three devices is measured through three current sensors. In the initial phase the AGD Master generates PWM signal input for the MOSFETs according to input reference 40). Furthermore, the AGD Slave-i undertakes to drain current (Id) balancing duties for the MOSFETs Slave by adjusting the PWM Ton for each MOSFET. Specifically, the AGD

Slave-i acquires current information from the current sensors of both the Master and Slave-i, recognizes the current error and executes the current balancing algorithm. Then, the PWM duty cycle (dty) Or specifically the switching on time (Ton) of each MOSFET is adjusted using an interrupt signal (T Int) from the AGD Slave-i in a closed-loop manner. The closed-loop control is realized by the current sensors. An example of an interrupt signal that cuts the PWM waveform is shown in Fig. 3.

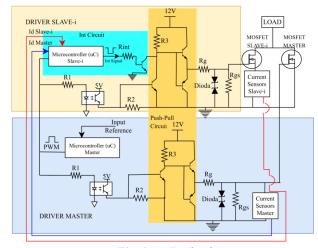

Fig. 4: AGD Circuit.

The proposed AGD consists of AGD Master and Slavei as shown in Fig. 4. Each AGD has an optocoupler for the purpose of isolating control signals and segregating lowpower devices from high-power devices<sup>17)</sup>. This allows safe control of high-power devices without adversely affecting the operation of the microcontroller (uC) Master. The push-pull transistor circuit is a power amplifier to amplify the voltage from 5V to 12V 20). R1 is a voltage limiter from the microcontroller ( $\mu$ C) to the optocoupler. Generally, the value range of R1 is 10 to 100  $\Omega$ . R2, R3 and Rint are the voltage limiter of the transistor, typically in 1k  $\Omega^{17}$ ). Rg is the current limiter for the MOSFET gate and the speed regulator of MOSFET charge-discharge capacitance. A Zener diode is used to avoid gate surge voltage and electrostatic discharge on the circuit. Meanwhile, the resistor gate to the source (Rgs) is a resistor to reduce the voltage of the MOSFET gate to the source. The value is 1k to 10k  $\Omega^{17}$ .

A circuit configuration of MOSFETs with AGD on a parallel connection is depicted in Fig. 4. The configuration circuit consists of three microcontrollers ( $\mu$ C). One microcontroller ( $\mu$ C) 1 functions as a PWM generator for the AGD Master, while the other microcontroller ( $\mu$ C) 2 serves as the Slave MOSFET. The microcontrollers ( $\mu$ C) 2 interrupt and calculate the time delay based on input from Master (Id master) and Slave (Id slave-i) current sensors. The reference for current balancing is according to the Master-Slave concept<sup>18</sup>). The MOSFET with the smallest current value is defined as Master and the others are Slaves.

Fig. 5: Flowchart of Current Balancing Process.

In the current balancing process of Fig. 5, the PWM signal from the microcontroller ( $\mu$ C) 1 is received by each MOSFET and the microcontroller ( $\mu$ C) 2 as an interrupt trigger. Microcontroller ( $\mu$ C) 2 reads the drain current (Id) from the Master MOSFET and Slave when a falling edge trigger is detected from the PWM signal. The difference value between the Slave and Master MOSFETs, along with the duty cycle value of the Master, serves as the primary criteria for computing the microcontroller ( $\mu$ C) 2 output signal, which determines the interrupt time. This signal plays a crucial role in achieving precise Ton or Duty Cycle adjustments for each Slave-i. The interrupt time value is calculated based on programming calculations, taking into account the total switching time on the MOSFET (µS) and the ADC input of the potentiometer (used as a reference for the duty cycle of the PWM signal) in a 10-bit state, as per Eq. 3.

Interrupt time =

$$\frac{k2a}{1023} \times \frac{ADC\ port}{1023} \times Ttotal$$

(3)

The k2a is the difference between the ADC port values of the current sensors of Master MOSFET and Slave MOSFET. The ADC value is in a 10-bit so the k2a and ADC port in Eq. 3 are divided by 1023, while the total switching time is 125  $\mu S$ .

The microcontroller output ( $\mu$ C) 2 received by each Slave MOSFET will affect the trimming of the gate driver output signal for each MOSFET. A special condition occurs when the duty cycle is 0% and 100%, which is the falling edge trigger cannot be found. As a result, the execution process is not carried out in an interrupt condition. For the 0% condition, due to the absence of a current difference, there is no execution process for this condition. Meanwhile, when the condition is 100%, the falling edge trigger cannot be obtained, resulting in the

execution process not being carried out in an interrupt condition.

The analysis of the experiment data is carried out by comparing the MOSFET performance when tested without AGD and with AGD. The experiment records the current (Id) flow of each MOSFET for a certain duration. The test was carried out on three MOSFETs in parallel assembly with a dummy load of three bulbs, which is equivalent to a resistive load of 288W and an inductive load of 120W.

#### 3. Results and Discussion

Experiments results are presented with MOSFET arranged in parallel connection using both without AGD or conventional gate driver (CGD) and with AGD. The test was carried out on three MOSFETs with a dummy load connected by separate planar copper busbars. The dummy load is three 12V bulbs equivalent to a resistive load of 288W and an inductive load of 120W. The parallel assembly MOSFETs and gate driver are connected on different boards to avoid heat conduction produced by the MOSFET dissipation. The PWM and AGD waveform was recorded using the Instrustar ISDS205A 2-channel digital oscilloscope. Furthermore, the MOSFET drain-source current (Id) was recorded using a datalogger Labjack T7 with a sampling time of 20  $\mu S$  for 1 S. The experimental setup can be seen in Fig. 6 and Fig. 7.

**Fig. 6:** Circuit of Experimental setup on The Study (a) Without AGD (CGD), and (b) With AGD.

Fig. 7: Photograph of Experimental setup on The Study.

### 3.1 Testing without AGD on Resistive Load

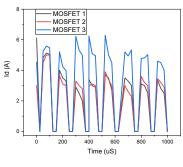

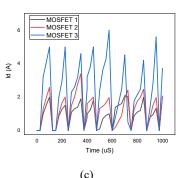

**Fig. 8:** Test Results Without AGD, (a). 25%, (b). 50%, (c). 75%.

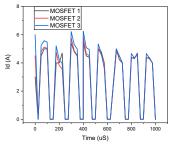

Fig. 8. illustrates the imbalance in Id current that occurs without AGD or when using a conventional gate driver (CGD) in three different duty cycle conditions. In situations where the duty cycle or total current increases, a significant impact is observed in the deviation of MOSFET current values despite the consistent PWM signals. This observed current imbalance can be attributed to device characteristic mismatches, non-symmetrical circuit layouts, and cooling conditions in the parallel MOSFET connection 19,29,30).

Under a 15% duty cycle, each MOSFET exhibits relatively similar Id current values. However, as the duty cycle increases to 50%, an imbalance occurs between MOSFETs 1 and 2, while MOSFET 3 takes most of the load current, resulting in the most significant deviation, as evident in Fig. 8(b). Fig. 8(c) demonstrates that MOSFET 3 exhibits the most pronounced deviation, reaching 9 A at a 75% duty cycle, while MOSFET 1 has the lowest Id

current value. It is essential to note that in these situations, the peak current of MOSFET 3 approaches 16 A due to this imbalance, thereby increasing the risk of module failure. The disparity in MOSFET current distribution can have critical implications for the reliability and performance of power electronic systems, particularly when used in applications with resistive loads. The non-uniform current distribution in the parallel configuration can lead to uneven heating, potential hotspots, and reduced overall efficiency<sup>1,23</sup>. Based on the above experimental result, this AGD study selected MOSFET 1 with the lowest current value as the Master MOSFET and the others as Slave MOSFETs.

### 3.2 Testing with AGD on Resistive Load

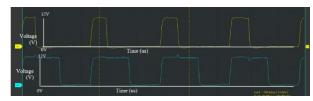

**Fig. 9:** Output Waveform AGD MOSFET 1 (Blue Color) and AGD MOSFET 3 (Yellow Color).

The test using AGD with the same power module and test conditions without AGD were obtained. In the system, one MOSFET is defined as Master and two as Slaves. The output waveform of AGD MOSFET 1 (Master) and MOSFET 3 (Slave) under a 50% PWM duty cycle on an oscilloscope is in Fig. 9. The result shows the proposed AGD circuit can cut off the PWM signal and reduce the turn-on switching time (Ton) from 76,5  $\mu S$  to 32,5  $\mu S$ .

(b)

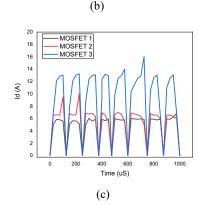

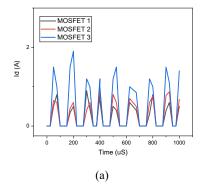

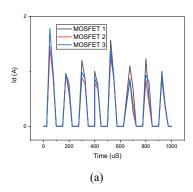

**Fig. 10:** Test Results With AGD, (a). 25%, (b). 50%, (c).

Based on the testing conducted with AGD as shown in Fig. 10, the current between each MOSFET is balanced in all duty cycle conditions. As seen in Fig. 10(a), the Id value of MOSFET 3 can be lowered to align with the other MOSFETs. Meanwhile, in Fig. 10(b), the Id values of each MOSFET experience spikes or ringing, but adjustments to the Ton values of the Slave MOSFETs can synchronize the Id values. This is particularly noticeable in conditions with the largest current difference when testing without AGD (duty cycle of 75%). In that state, the current value between MOSFETs can be balanced and stable at 6 A. The changes in turn-on switching time (Ton) affect the value of the current flowing (Id) of the MOSFET according to ref<sup>15,41)</sup> and Eq. 3. The proposed AGD can reduce Id deviation by 80% compared to without AGD at each duty cycle condition and the current value between MOSFETs can be balanced.

According to the result, the proposed method can overcome the problems in several previous studies. The application of a simple digital process can reduce delay time in the balancing process  $^{21\text{-}23)}$ . Directly applying simple components with a microcontroller ( $\mu C$ ) can ensure the durability of the system, reduce the power consumption of the system, increase cost-efficiency, and be robust against electrical noise  $^{23\text{-}28,31\text{-}35)}$ . To further demonstrate the advantages of the proposed AGD method, experiments with inductive loads have been carried out.

#### 3.3 Testing on Inductive Load

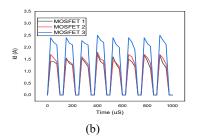

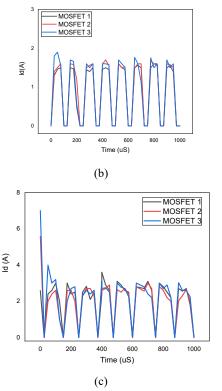

**Fig. 11:** Test Results Without AGD on inductive load, (a). 25%, (b). 50%, (c). 75%.

In Fig. 11, the performance of MOSFETs without AGD is illustrated under inductive load conditions with varying duty cycles. The total load current being switched is 10 A, and the duty cycle is increased from 25% to 75% (with a 25% resolution) to highlight the Id imbalance conditions. There is a deviation in MOSFET 3 compared to the other MOSFETs, ranging from 1-3 A under all duty cycle conditions. Additionally, MOSFET 1 exhibits the lowest Id value when compared to the other MOSFETs, particularly at the 75% duty cycle condition.

Moreover, peak current occurrences are observed in each MOSFET, influenced by the inductance characteristics of the load. Inductive loads, such as electric motors, can display abrupt current spikes that occur during power-on or power-off events due to the gradual formation or collapse of the magnetic field within the inductor. These temporary peak current spikes have the potential to impact the overall system performance and should be taken into consideration during the design and operation of power electronic systems<sup>32,35,41</sup>).

**Fig. 12:** Test Results With AGD on inductive load, (a). 25%, (b). 50%, (c). 75%.

According to the test with the AGD shown in Fig. 12, the implementation of active gate drivers for MOSFETs in a parallel configuration has successfully balanced the current differences, even in the presence of fluctuations in the inductive load. The proposed AGD function to precisely and responsively control the Ton of each Slave MOSFET, allowing for rapid adjustments to changes in load demand. As a result, AGD can provide more accurate current regulation for each MOSFET, reducing current imbalances, and preventing excessive current peaks. This helps improve overall system efficiency and ensures MOSFETs operate optimally.

Based on the experimental findings with resistive and inductive loads, the proposed AGD effectively reduces Id deviation by 80% compared to without AGD and addresses the current unbalance in specific load and duty cycle conditions. However, fluctuations are observed during switching transitions. Hence, further development and additional modifications to the AGD are required. With improved current distribution and the ability to handle fluctuations, the system becomes more efficient, durable, and stable in operation. Nonetheless, the utilization of the proposed AGD provides significant advantages in enhancing the performance and reliability of power electronic systems with resistive and inductive loads.

Based on the experimental results, the implementation of AGD has shown the potential to significantly increase the load capacity of paralleled MOSFETs, ranging from 2 to 3 times compared to configurations without AGD.

However, it is essential to consider the specific specifications and characteristics of the MOSFETs used in the circuit, as the extent of capacity improvement may vary based on their performance capabilities. Hence, careful matching of MOSFETs and the integration of AGD are crucial in maximizing the load capacity enhancement in parallel MOSFET arrangements.

The success of the current balancing method in the parallel assembled MOSFET is indicated by its capability to improve performance and overcome the damage risk to each MOSFET <sup>19)</sup>. The impact of the current difference between Master and Slave MOSFETs on overall reliability for more than three parallel assemblies will be studied in future work.

#### 4. Conclusion

This paper proposed a new method of AGD to control the current of MOSFETs in parallel. The AGD driver consists of three separate gate drivers to set the Ton switching time of each MOSFET. With the proposed design, the time value of the Ton or duty cycle between MOSFET is properly adjusted. The Id difference between the Master and Slave MOSFET, which previously reached 2 to 3 can be balanced. Experimental results with a total resistive load of 288W and inductive load have proven that the AGD method can overcome the current imbalance in the MOSFET assembled in parallel. Furthermore, it improves performance, ensures equal current sharing, and overcomes the risk of damage to each MOSFET. Additionally, The advantage of this method is that the control system can be customized to suit the specific needs of a particular application, allowing for optimization of performance to control current unbalance under different operating conditions. Last but not least, a module consisting of several MOSFETs connected in parallel is expected to be more robust under dynamic loads.

#### Acknowledgments

This work was supported by National Research and Innovation Agency (BRIN) under the electric vehicle technology research grant. Sunarto Kaleg is the main contributor to this paper. Damaris Adi Waskitho contributed to writing the article, conducting experiment, data preparation, and data analysis. All authors read and approved the final paper. The authors do not have any conflict of interest to declare.

#### References

Beye, M.L., Wickramasinghe, T., Mogniotte, J.F., Phung, L.V., Idir, N., Maher, H., & Allard, B., "Active Gate Driver and Management of the Switching Speed of GaN Transistors during Turn-On and Turn-Off," *Electronics*, 10 (2) 106 (2021). doi: 10.3390/electronics10020106.

- S. Acharya, X. She, F. Tao, T. Frangieh, M. H. Todorovic and R. Datta, "Active gate driver for SiC MOSFET based PV inverter with enhanced operating range," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 3230-3237 (2018). doi: 10.1109/APEC.2018.8341565.

- 3) O. Kwon, J. M. Kwon and B. H. Kwon, "Highly efficient single-phasethree-level three-leg converter using SiC MOSFETs for AC–AC applications," *IEEE Trans. Ind. Electron*, **65** (9) 7015–7024, (2018). doi: 10.1109/TIE.2018.2793231.

- 4) P. Barman, P. Baruah and S. Sharma, "An Optoisolator Based Gate Driver Design for Reliable Operation in High Power Motor Control Applications," *International Conference on Advances in Electrical, Computing, Communication and Sustainable Technologies (ICAECT)*, 1-6 (2021), doi: 10.1109/ICAECT49130.2021.9392583.

- 5) H. Wang and D. Jiang, "Design of high temperature gate driver for SiC MOSFET for EV motor drives," *IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific)* 1-6 (2017). doi: 10.1109/ITEC-AP.2017.8080762.

- S. Parashar and S. Bhattacharya, "A Novel Gate Driver for Active Voltage Balancing in 1.7kV Series Connected SiC MOSFETs," IEEE Applied Power Electronics Conference and Exposition (APEC), 2773-2779 (2019). doi: 10.1109/APEC.2019.8722176.

- S. Ivanov and Y. Ivanova, "Research of the Impacy of an Active Driver circuit with di / dt Feedback on DC Motor Speed," *IX National Conference with International Participation (ELECTRONICA)*, 1-4 (2018). doi: 10.1109/ELECTRONICA.2018.8439363.

- 8) Hussein A. Jaffar, Ali A. Ismaeel, Ahlam Luaibi Shuraiji, "Review of Hybrid Photovoltaic- Air Updraft Solar Application: Present and Proposed state Models," *Evergreen*, 9(4) 1181-1202 (2022). doi:10.5109/6625729

- 9) Mu'to Naimah, Farashinta Dellarosa Nanda Pratama, Farashinta Dellarosa Nanda Pratama, "Photocatalytic Hydrogen Production Using Fe-Graphene/TiO2 Photocatalysts in the Presence of Polyalcohols as Sacrificial Agents," *Evergreen*, 9(4) 1244-1251 (2022). doi:10.5109/6625736

- 10) I. Roihan, K. Tjandaputra A., E.A. Setiawan, and R.A. Koestoer, "Installing and testing the grashof portable incubator powered using the solar box 'be-care' for remote areas without electricity," *Evergreen*, 7(4) 621–628 (2020). doi:10.5109/4150516.

- 11) M. Ezaki, and K. Kusakabe, "Highly crystallized tungsten trioxide loaded titania composites prepared by using ionic liquids and their photocatalytic behaviors," *Evergreen*, **1**(2) 18–24 (2019). doi: 10.5109/1495159.

- 12) N.I.I. Zamri, S.L.N. Zulmajdi, E. Kusrini, K. Ayuningtyas, H.M. Yasin, and A. Usman, "Rhodamine B Photocatalytic Degradation using CuO Particles under UV Light Irradiation for Applications in Industrial and Medical Fields," *Evergreen*, 7(2) 280–284 (2020). doi:10.5109/4055233.

- 13) M. Elimelech, a Zhang, Y., Song, Q., Tang, X. et al. "Gate Driver For Parallel Connection Sic MOSFETs With Over Current Protection And Dynamic Current Balancing Scheme," *Journal of Power Electronics*, 20 319-328 (2020). doi: 10.1007/s43236-019-00026-1.

- 14) D. N. Dalal et al., "Impact of Power Module Parasitic Capacitances on Medium Voltage SiC MOSFETs Switching Transients," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, 8 (1) 298-310 (2020). doi: 10.1109/JESTPE.2019.2939644.

- 15) Obara, H. "Active Gate Control In Half-Bridge Inverters Using Programmable Gate Driver Ics To Improve Both Surge Voltage And Converter Efciency," *IEEE Transactions on Industry* Applications, 54 (5) 4603-4611 (2018). doi:10.1109/TIA.2018.2835812.

- 16) Luedecke, C., Krichel, F., Laumen, M., & Doncker, R. W. "Balancing the Switching Losses of Paralleled SiC MOSFETs Using an Intelligent Gate Driver," *IEEE Energy Conversion Congress and Exposition* (ECCE), 5400-5406 (2021). doi: 10.1109/ECCE47101.2021.9595091.

- 17) Dymond, H. "A 6.7-GHz active gate driver for GaNFETs to combat overshoot, ringing, and EMI," IEEE Trans. Power Electron, 33 (1) 581-594 (2017). doi: 10.1109/TPEL.2017.2669879.

- 18) Junhui Ao, Z. W. "The Cost-Efficient Gating Drivers with Master Slave Current Sharing Control for Parallel SiC MOSFET," *IEEE Transportation Electrification Conference and Expo*, 1-5 (2018) doi: 10.1109/ITEC-AP.2018.8433284.

- 19) Alejandro Paredes, H. G. "A New Active Gate Driver for Improving the Switching Performance of SiC MOSFET," IEEE Applied Power Electronics Conference and Exposition (APEC), 3172-3177 (2017). doi: 10.1109/APEC.2017.7931208.

- 20) Y. Mukunoki, et al. "Electro-Thermal Co-Simulation of two Parallel-Connected SiC-MOSFETs Under Thermally- Imbalanced Conditions," *IEEE Applied Power Electronics Conference and Exposition* (APEC), 2855–2860 (2018). doi: 10.1109/APEC.2018.8341422.

- 21) Wang, P., et al. "An integrated gate driver with active delay control method for series connected SiC MOSFETs," *IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL)*, 1–6 (2018). doi: 10.1109/COMPEL.2018.8459904.

- 22) Y. Sukhatme, J. Titus, P. Nayak and K. Hatua, "Digitally controlled active gate driver for SiC

- MOSFET based induction motor drive switching at 100 kHz," in *IEEE Transportation Electrification Conference (ITEC)*, 1-5 (2017). doi: 10.1109/ITEC-India.2017.8356953.

- 23) Yang, Y., et al.: "An active gate driver for improving switching performance of SiC MOSFET," in *International Symposium on Next Generation Electronics (ISNE)*, 1–4 (2018). doi: 10.1109/ISNE.2018.8394704.

- 24) Krishna, M.V., Hatua, K.: "Closed loop analog active gate driver for fast switching and active damping of SiC MOSFET," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 3017–3021 (2018). doi: 10.1109/APEC.2018.8341530.

- 25) Q. -X. Guan et al., "An Extremely High Efficient Three-Level Active Neutral-Point-Clamped Converter Comprising SiC and Si Hybrid Power Stages," *IEEE Transactions on Power Electronics*, **33** (10) 8341-8352 (2018). doi: 10.1109/TPEL.2017.2784821.

- 26) S. Ko, Y. Jeong, R. Rorrer and J. -D. Park, "High Efficiency Asymmetric Dual Active Clamp Forward Converter with Phase-Shift Control for Small Conduction Loss," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 1866-1871 (2020). doi: 10.1109/APEC39645.2020.9124611.

- 27) Beye, M. L., J. F. Mogniotte, Luong Viêt Phung, Nadir Idir, Hassan Maher and Bruno Allard. "Analysis and Assessment of temperature effect on an Open Loop Active Gate Voltage Control of GaN Transistor during Turn-ON and Turn-OFF." *IEEE 13th International Conference on Power Electronics and Drive Systems (PEDS)*, 1-5 (2019). doi: 10.1109/PEDS44367.2019.8998769.

- 28) Jianing Guo, "Analysis of Current Imbalance in Parallel Silicon Carbide Power MOSFETs," *Academic Journal of Science and Technology,* **3** (3) 247-254 (2022). doi: 10.54097/ajst.v3i3.2992.

- 29) C. Zhao, L. Wang, F. Zhang and F. Yang, "A Method to Balance Dynamic Current of Paralleled SiC MOSFETs With Kelvin Connection Based on Response Surface Model and Nonlinear Optimization," *IEEE Transactions on Power Electronics*, 36 (2) 2068-2079 (2021). doi: 10.1109/TPEL.2020.3009008.

- 30) N. Zhu, M. Chen, R. Yan, A. Mantooth and D. Xu, "Die Current Balancing of a Press-Pack SiC MOSFET," *IEEE Energy Conversion Congress and Exposition (ECCE)* 5824-5830 (2018). doi: 10.1109/ECCE.2018.8557940.

- 31) A. Lavarda, L. Petruzzi, N. Radež, and B. Deutschmann, "On the Robustness of CMOS-Chopped Operational Amplifiers to Conducted Electromagnetic Interferences," IEEE Transactions on Electro-magnetic Compatibility, 60 (2) 478–486, (2018). doi: 10.1109/TEMC.2017.2729781.

- 32) R. Ramabhadran, M. H. Todorovic, C. Li, E. Asa and K. -K. Huh, "An Analog Active Gate Drive Circuit Architecture for Wide Band Gap Devices," *IEEE Energy Conversion Congress and Exposition (ECCE)*, 380-386 (2019). doi: 10.1109/ECCE.2019.8912218.

- 33) Vamshi K. M., K. Hatua, "Low-cost analogue active gate driver for SiC MOSFET to enable operation in higher parasitic environment," *IET Power Electronics*, 13 (3) 463-474 (2020). doi: 10.1049/iet-pel.2019.0589.

- 34) Y. Yang, Y. Wen and Y. Gao, "A Novel Active Gate Driver for Improving Switching Performance of High-Power SiC MOSFET Modules," *IEEE Transactions on Power Electronics*, **34** (8) 7775-7787 (2019). doi: 10.1109/TPEL.2018.2878779.

- 35) Acharya, S., et al.: "Active gate driver for SiC-MOSFET based pv inverter with enhanced operating range," *IEEE Transaction on Industry Application, Publishing*, 55 (2) 1677-1689 (2019). doi: 10.1109/TIA.2018.2878764.

- 36) C. Xu, X. Zhong, H. Jiang, G. Qiu, L. Tang and L. Ran, "Impact of Duty Cycle and Junction Temperature on Dynamic Threshold Drift of SiC MOSFET," 4th International Conference on Energy, Electrical and Power Engineering (CEEPE), 347-350 (2021). doi: 10.1109/CEEPE51765.2021.9475706.

- 37) Y. Peng and H. Wang, "Duty Cycle based Condition Monitoring of MOSFETs in Digitally-Controlled DC-DC Converters," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 364-369 (2020). doi: 10.1109/APEC39645.2020.9124403.

- 38) K. Puschkarsky, H. Reisinger, T. Aichinger, W. Gustin and T. Grasser, "Understanding BTI in SiC MOSFETs and Its Impact on Circuit Operation," *IEEE Transactions on Device and Materials Reliability*, 18 (2) 144-153 (2018). doi: 10.1109/TDMR.2018.2813063.

- 39) Y. Funaki and K. Wada, "Gate Drive Circuit Configuration for Current Balancing of SiC MOSFETs Connected in Parallel," IEEE International Future Energy Electronics Conference (IFEEC), 1-5 (2021). doi: 10.1109/IFEEC53238.2021.9661805.

- 40) K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin and H. Reisinger, "Understanding and modeling transient threshold voltage instabilities in SiC MOSFETs," *IEEE International Reliability Physics Symposium (IRPS)*, 3 (5) 1-10 (2018). doi: 10.1109/IRPS.2018.8353560.

- 41) L. Du, Y. Wei, X. Du, A. Stratta, Z. Saadatizadeh and H. A. Mantooth, "Digital Active Gate Driving System for Paralleled SiC MOSFETs with Closed-loop Current Balancing Control," *IEEE Energy Conversion Congress and Exposition (ECCE)*, 1-6 (2022). doi: 10.1109/ECCE50734.2022.9947707.