#### 九州大学学術情報リポジトリ Kyushu University Institutional Repository

### An Energy Characterization Framework for Software-Based Embedded Systems

Lee, Donghoon Faculty of ISEE, Kyushu Univ.

Ishihara, Tohru System LSI Research Center, Kyushu Univ.

Muroyama, Masanori System LSI Research Center, Kyushu Univ.

Yasuura, Hiroto System LSI Research Center, Kyushu Univ.

他

https://hdl.handle.net/2324/6794497

出版情報: ESTIMedia2006. 1, pp.59-64, 2006-10-26. ESTIMedia

バージョン: 権利関係:

# An Energy Characterization Framework for Software-Based Embedded Systems

Donghoon Lee<sup>1</sup>,

Tohru Ishihara<sup>2</sup>, Masanori Muroyama<sup>2</sup>, Hiroto Yasuura<sup>2</sup>,

Farzan Fallah<sup>3</sup>

- <sup>1</sup> Faculty of ISEE, Kyushu Univ.

- <sup>2</sup> System LSI Research Center, Kyushu Univ.

- <sup>3</sup> Fujitsu Labs. of America

#### Outline

Introduction

- Energy characterization framework

- Training bench generation

- Experimental results

- Summary

#### Back Ground (1/2)

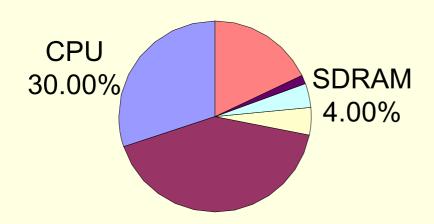

## Power consumption at a processor on embedded system has a big portion

Power Distribution in a PDA class sample device

Cliff Brake, Accelent Systems, Inc. (May, 2003)

www.princeton.edu/~wolf/

#### Back Ground (2/2)

## Power consumption at a processor depends on the software being executed

SW designer should think power dissipation by SW that he is developing

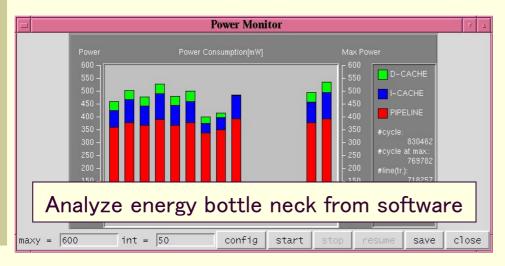

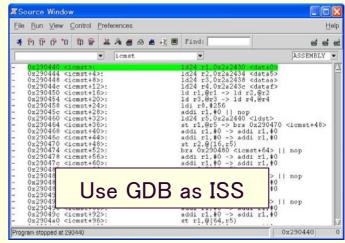

#### Energy Analysis Tool

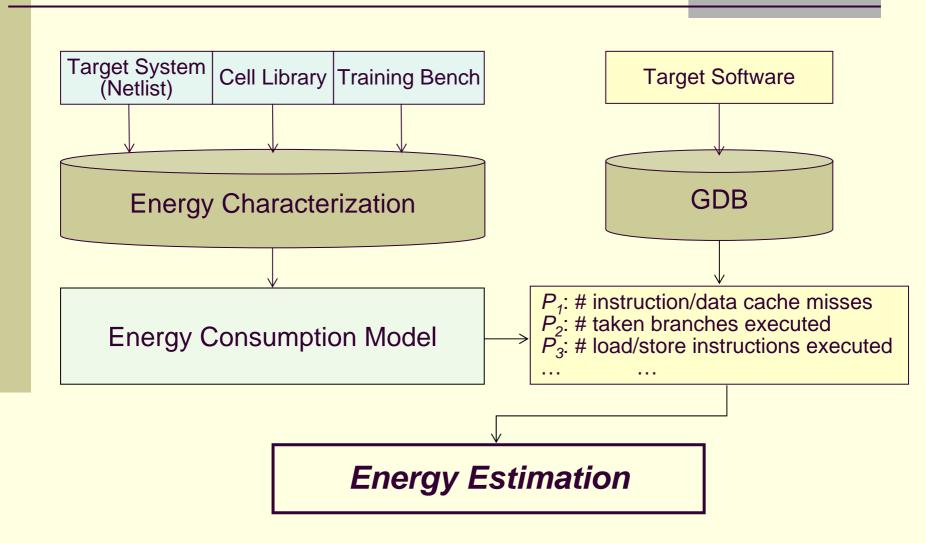

# We propose a characterization technique to find a good energy model for a processor

Fast, accurate, and processor-independent Instruction level energy estimation

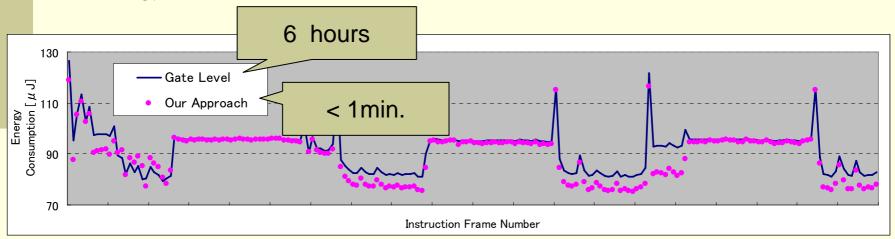

#### Experimental Result

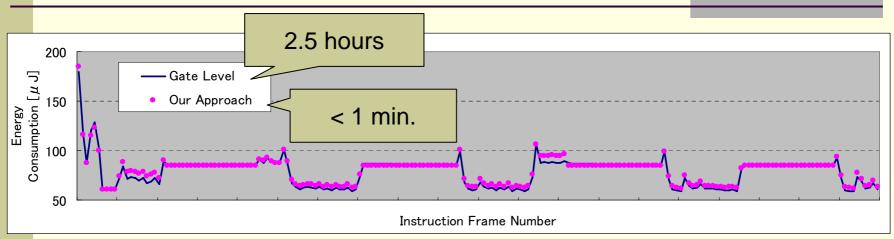

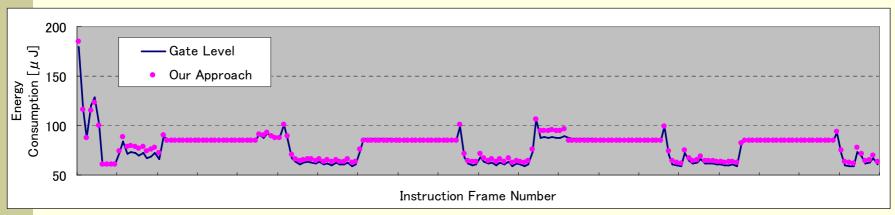

Energy estimation for JPEG encoder executed on a M32R-II processor

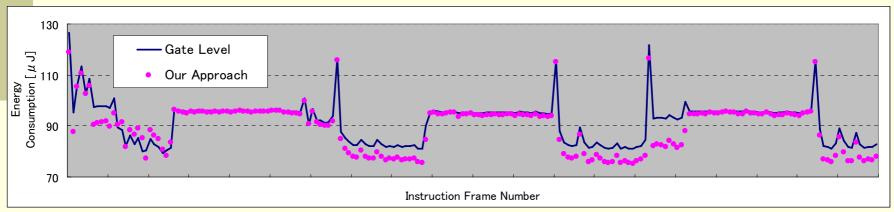

Energy estimation for JPEG encoder executed on a SH3-DSP processor

#### Related Work (1/2) High-level energy estimation

- Instruction-level modeling

- Energy estimation by instruction-set simulator

- Instruction level energy modeling by measuring the average power consumption of each instruction while executed in a loop

V. Tiwari, S. Malik, and A. Wolfe, "Power analysis of embedded software: a first step towards software power minimization," IEEE Tr. On VLSI, vol. 2, no. 4, pp. 437-445, Dec. 1994.

- Structural modeling of the underlying hardware architecture

- Make power models by estimating capacitance on the circuit

- Keep track of which units are accessed per cycle by cyclelevel performance simulation

D. Brooks, V. Tiwari, and M. Matonosi, "Wattch: A Framework for Architectural-Level Power Analysis and Optimization," in Proc. Of ISCA, pp. 84-94, June. 2000.

#### Our Approach

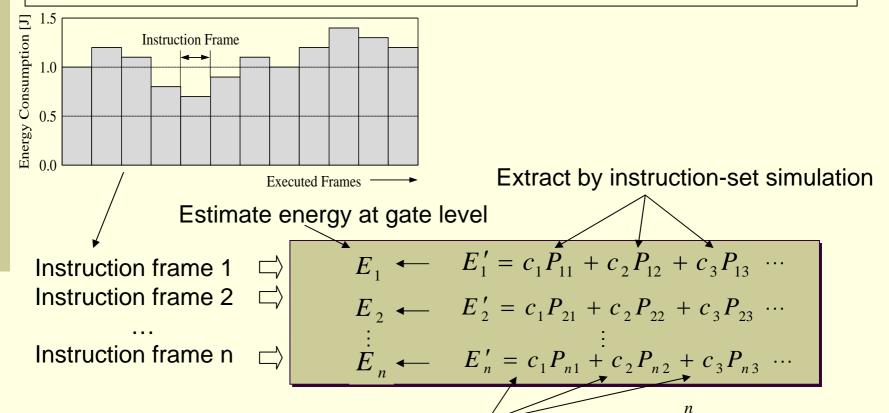

#### Related Work (2/2) Characterization-based energy estimation

- Characterization-based macro-modeling

- Regression analysis to model software energy

- Model the energy consumption using linear expression

$$E = \sum_{j=1}^{p} C P_{j}$$

· P<sub>j</sub> : parameters of the model

· c<sub>i</sub>: corresponding coefficients

p: number of parameters

$$\mathbf{P} = \begin{pmatrix} P_{1,1} & P_{1,2} & \dots & P_{1,p} \\ P_{2,1} & P_{2,2} & \dots & P_{2,p} \\ \dots & \dots & \dots & \dots \\ P_{n,1} & P_{n,2} & \dots & P_{n,p} \end{pmatrix} \qquad \mathbf{E} = \begin{pmatrix} E_1 \\ E_2 \\ \dots \\ E_n \end{pmatrix} \qquad \mathbf{C} = \begin{pmatrix} c_1 \\ c_2 \\ \dots \\ E_n \end{pmatrix} = \begin{bmatrix} \mathbf{P}^T \mathbf{P} \end{bmatrix}^{-1} \mathbf{P}^T \mathbf{E}$$

$$\mathbf{E} = \begin{pmatrix} E_1 \\ E_2 \\ \dots \\ E_n \end{pmatrix}$$

$$C = \begin{pmatrix} c_1 \\ c_2 \\ \dots \\ c_n \end{pmatrix} = \left[ \mathbf{P}^T \mathbf{P} \right]^{-1} \mathbf{P}^T \mathbf{E}$$

Evaluate set of parameters

Obtain the energy consumption by low-level estimator

Obtain coefficient using regression analysis

T. K. Tan, A. Raghunathan, G. Lakshminarayana, and N. K. Jha, "High-level software energy macro-modeling," in Proc. Design Automation Conf., 2001, pp. 605--610.

#### Overview of Energy Characterization

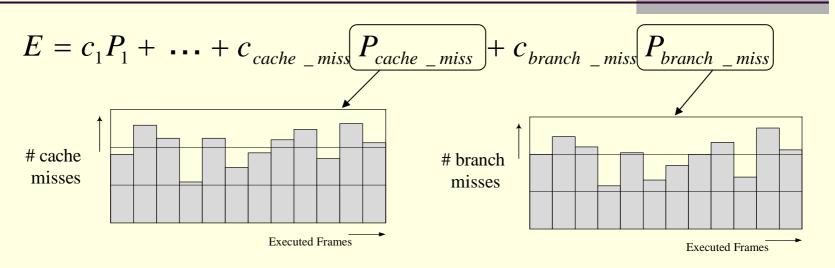

- Energy consumption model based on linear expression

- Evaluate energy from each divided instruction frames

Solve the set of  $c_i$  which minimizes  $\sum |E_i' - E_i|$

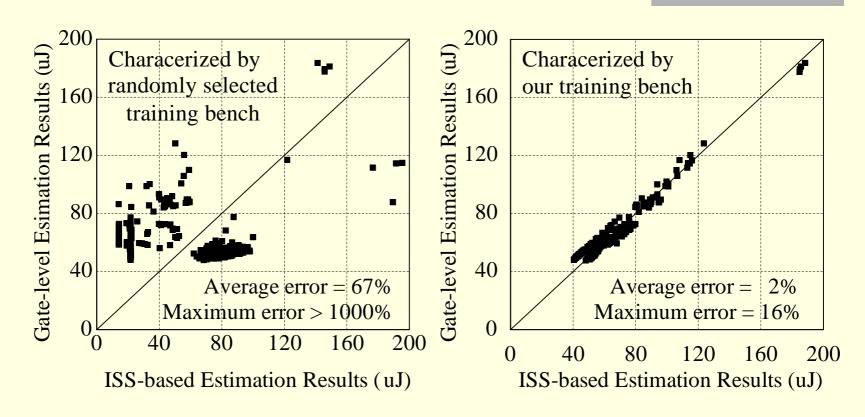

#### Error Sources of this characterization

Parameter set selection

Non-linear effects

Training bench

**.**..

#### Motivational Example

Training bench dominates model accuracy !!

What is expected for a 'good' training bench?

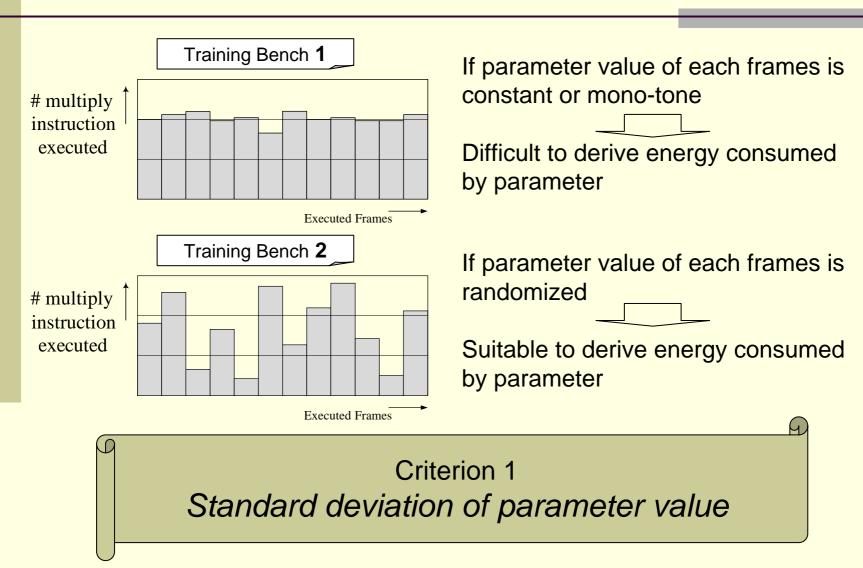

#### Criteria on Training Bench (1/2)

### Criteria on Training Bench (2/2)

If correlation is strong between two parameters

Difficult to derive energy consumption by each parameters

Criterion 2

Correlation between parameters

#### Training Bench Generation

#### Template of Training Bench

- Execute power hungry instructions repeatedly

- Produce many cache misses

- Produce many RAW hazards

- Produce many pipeline stalls

**Instruction Trace**

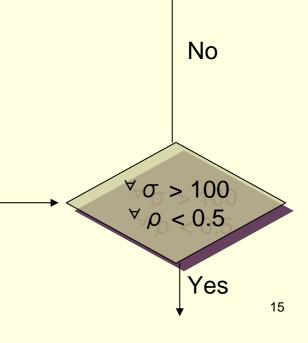

- Standard deviations of parameter values  $\sigma$

- Correlation factors of two parameters  $\rho$

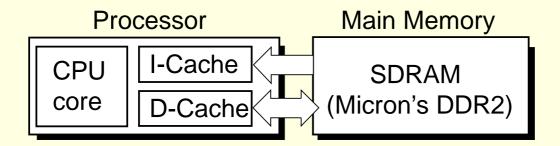

#### Experiment

Target system

- Processors

- M32R-II, SH3-DSP

- $\blacksquare$  0.18  $\mu$  m CMOS library

#### Experimental Result - Energy estimation error

|            | M32R-II       |                  | SH3-DSP       |                  |

|------------|---------------|------------------|---------------|------------------|

|            | Average Error | Maximum<br>Error | Average Error | Maximum<br>Error |

| JPEG       | 2.70 %        | 10.32 %          | 3.17 %        | 11.89 %          |

| JPEG_O     | 6.09 %        | 16.46 %          | 6.33 %        | 10.02 %          |

| MPEG2      | 1.54 %        | 3.97 %           | 1.32 %        | 3.41 %           |

| MPEG2_O    | 1.78 %        | 5.15 %           | 1.31 %        | 5.63 %           |

| compress   | 5.00 %        | 6.41 %           | 5.73 %        | 10.84 %          |

| compress_O | 4.35 %        | 7.18 %           | 1.73 %        | 15.15 %          |

| FFT        | 1.55 %        | 6.87 %           | 1.27 %        | 3.26 %           |

| FFT_O      | 1.45 %        | 5.59 %           | 1.15 %        | 4.75 %           |

| DCT        | 1.42 %        | 8.58 %           | 1.12 %        | 2.20 %           |

| DCT_O      | 1.47 %        | 8.07 %           | 1.51 %        | 3.04 %           |

| Total      | 2.74 %        | 16.46 %          | 2.47 %        | 15.15 %          |

Compared to the gate level estimation \*\_O : compiled with a "-O3" optimize option

#### Experimental Result

Energy estimation for JPEG encoder executed on a M32R-II processor

Energy estimation for JPEG encoder executed on a SH3-DSP processor

#### Summary

- Proposed energy characterization framework for processor-based embedded system

- Error is on an average 3% and worst case 16%

- Future work

- Compare result to board level measurement

- Extend current work to multi-core processor systems

- Extend to systems running on RTOS

### Thank You!