#### 九州大学学術情報リポジトリ Kyushu University Institutional Repository

## SysteMorph: AnSoC Framework for Adaptive Dynamic Optimization Systems

Noori, Hamid Department of Informatics, Kyushu University

Eshima, Kazuhito Department of Informatics, Kyushu University

Fujii, Yousuke

Department of Informatics, Kyushu University

Yoshida, Makoto Fukuoka Industry, Science & Technology Foundation

他

https://hdl.handle.net/2324/6231

出版情報: SLRC 論文データベース, 2005-06

バージョン: 権利関係:

## SysteMorph: An SoC Framework for Adaptive Dynamic Optimization Systems

Hamid Noori †, Kazuhito Eshima†, Yousuke Fujii†, Makoto Yoshida††, Takeshi Soga††, Norifumi Yoshimatsu††, Takanori Hayashida† & Kazuaki Murakami†

†Department of Informatics, Kyushu University ††Fukuoka Industry, Science & Technology Foundation E-mail: †arch-systemorph@c.csce.kyushu-u.ac.jp, ††ngarch@fleets.jp

#### **Abstract**

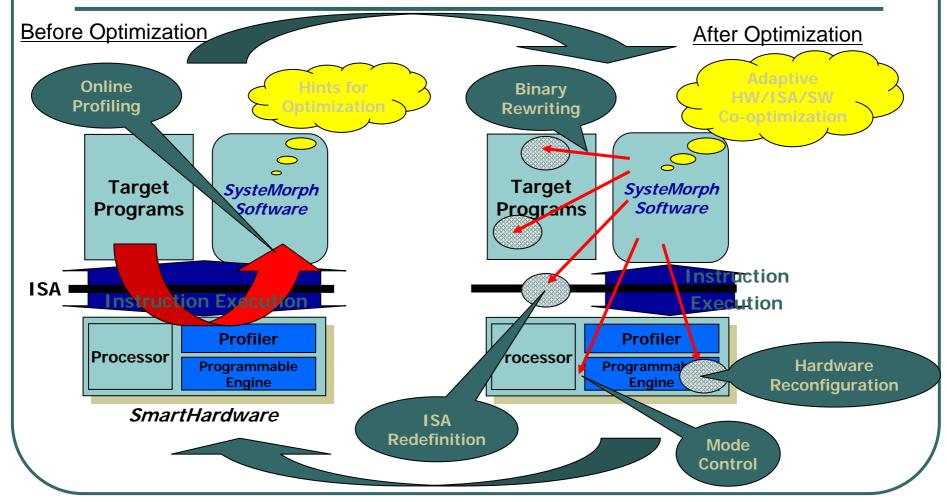

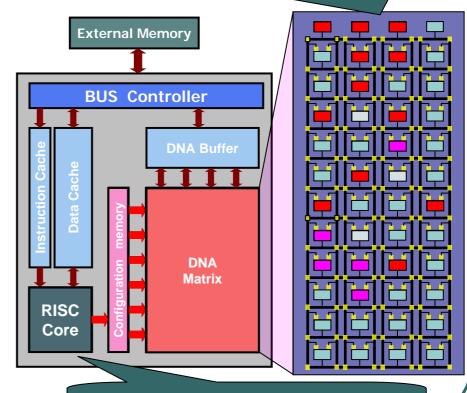

This research investigates a possible architecture to adaptive dynamic optimization systems. In this architecture, the running application is monitored and high frequently executed parts of the code are detected. Then, these parts of code are optimized, according to the architecture of embedded hardware accelerator. To be able to use the hardware accelerator, the new binary code is rewritten. IPFlex DAP/DNA-HP was the target of our prototyping to validate the concept. The proposed architecture for SoC implementation utilizes dynamic software pipelining technique for optimization and a simplified 8-way VLIW as the accelerator. Some preliminary performance evaluations show speedup.

## Concept of SysteMorph

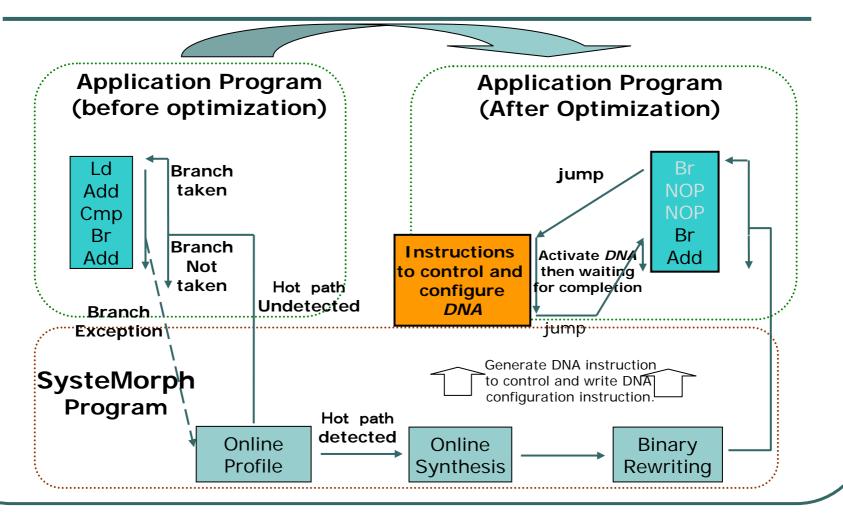

# SysteMorph Synthesis Flow on DAP/DNA-HP

Hot path information

Renaming

Optimization

Generate

Control/data flow graph

Timing matching

Mapping

Place and Route

Generate instructions to configure DNA

Generate instructions to control DNA

Flow for synthesis

Flow for instruction generation

DNA (Dynamic reconfigurable Logic)

DAP (32bit RISC Processor)

#### Execution Flow on DAP/DNA-HP

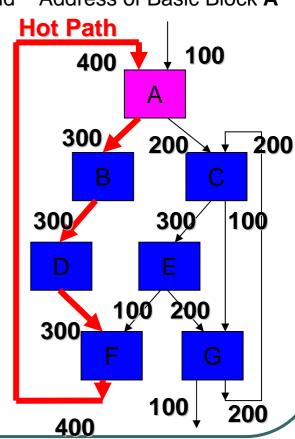

### Branch History Method

#### Branch History Table

| <b>A</b> top | : Head | Address | of Basic | Block A |

|--------------|--------|---------|----------|---------|

| Abottom      | :End   | Address | of Basic | Block A |

| Branch<br>Address | Branch Target<br>Address | Number of Branch |

|-------------------|--------------------------|------------------|

| Abottom           | Btop                     | 300              |

| Abottom           | Ctop                     | 200              |

| •••               | • • •                    |                  |

Number of Backward Branch > Threshold

#### Find Hot Path

A path which has more frequently taken is chosen as a Hot Path.

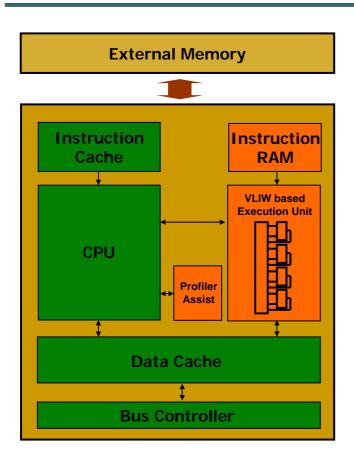

### SysteMorph with VLIW accelerator

#### CPU

Simple RISC processor

#### VLIW based accelerator

- Instruction RAM

- Compute intensive execution unit

#### H/W profiler assist

Store Branch history information

- Branch Target Address

- Branch Instruction Address

- Number of Taken/Not Taken

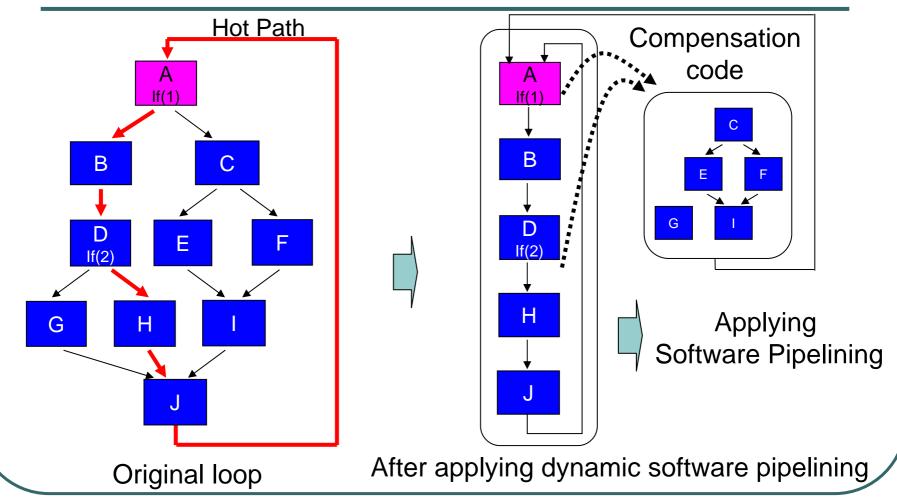

# Dynamic Trace Based Software Pipelining

#### Hot Paths

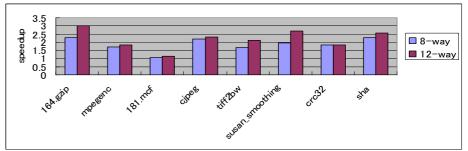

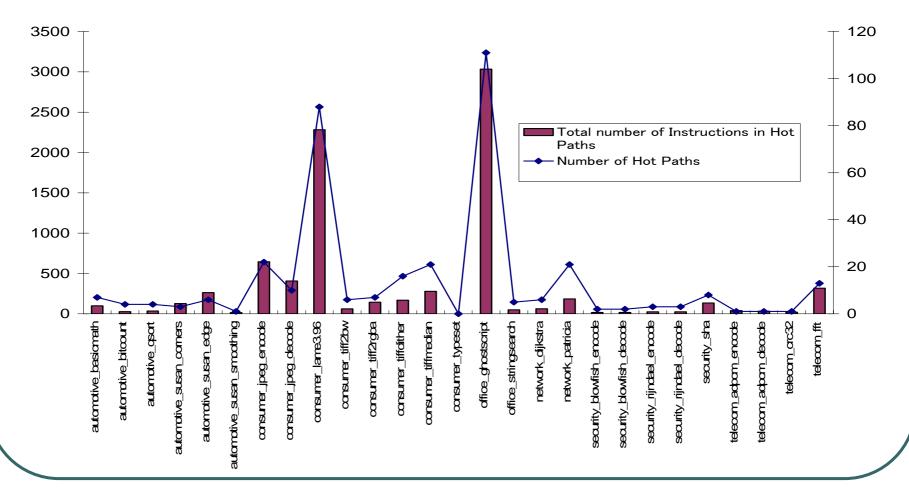

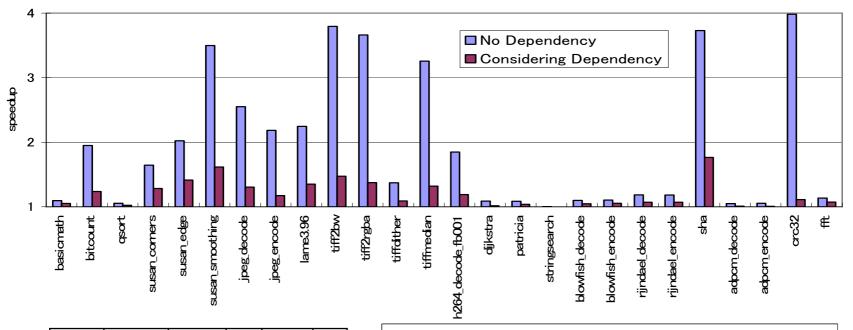

## Preliminary Performance Evaluation

|        | N (way) | Int | FP | Ld/St | Br |

|--------|---------|-----|----|-------|----|

| Exp. 1 | 4       | 3   |    | 1     |    |

| Exp. 2 | 8       | 3   | 1  | 3     | 1  |

| Exp. 2 | 12      | 5   | 1  | 5     | 1  |