# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# Fabrication of Oxide Passivated and Antireflective Thin Film Coated Emitter Layer in Two Steps for the Application in Photovoltaic

# Akter, Nahid

Computer Science and Telecommunication Engineering, Noakhali Science and Technology University

## Hossion, Abul

Physics, Bangabandhu Sheikh Mujibur Rahman Maritime University

### Amin, Nowshad

Renewable Energy and Solar Photovoltaics, Institute of Sustainable Energy, The National Energy University

https://doi.org/10.5109/4842524

出版情報: Evergreen. 9 (3), pp. 654-661, 2022-09. 九州大学グリーンテクノロジー研究教育センター

バージョン:

権利関係: Creative Commons Attribution-NonCommercial 4.0 International

# Fabrication of Oxide Passivated and Antireflective Thin Film Coated Emitter Layer in Two Steps for the Application in Photovoltaic

Nahid Akter<sup>1</sup>, Abul Hossion<sup>2,\*</sup> and Nowshad Amin<sup>3</sup>

<sup>1</sup>Computer Science and Telecommunication Engineering, Noakhali Science and Technology University, Noakhali 3814, Bangladesh

<sup>2</sup>Physics, Bangabandhu Sheikh Mujibur Rahman Maritime University, Dhaka 1216, Bangladesh.

<sup>3</sup>Renewable Energy and Solar Photovoltaics, Institute of Sustainable Energy, The National Energy University

(@Universiti Tenaga Nasional), 43000 Kajang, Selangor, Malaysia.

\*Author to whom correspondence should be addressed: E-mail: abulhossion.phy@bsmrmu.edu.bd

(Received May 12, 2022; Revised June 30, 2022; accepted July 1, 2022).

Abstract: The gap between laboratory scale and commercial silicon solar cells is wider, as many processes are not being practiced in commercialization. In this work, we have investigated the silicon solar cell fabrication process followed by industries and proposed a simplified process. The fabrication process for the emitter layer, 100 nm thin film anti-reflection coating and wet oxide passivation in a single chamber diffusion furnace on 200 micron p-type mono crystalline silicon wafer was followed. The diffusion process was carried out in an atmospheric furnace using phosphorus oxychloride as dopant source, oxygen for anti-reflection coating and wet oxide surface passivation. Topographical, optical and electrical characterization were conducted to understand the properties of the above layers for application in solar cell fabrication. The reflectivity and average sheet resistivity data of the diffused wafer is in the range those published in literature. Following the procedure, number of process steps, instrument and cost of commercial solar cell fabrication can be optimized.

Keywords: oxide passivation, thin film, crystalline silicon, antireflection coating, emitter layer.

#### 1. Introduction

Mono-crystalline silicon wafers are an interesting area for the research in the development of low cost commercial photovoltaic (PV) devices. Large industry scale PV cell fabrication is different from small laboratory scale cell fabrication. In practice many standard laboratories developed processes are not being transformed to large scale commercialization due to lack of commercial viability for turnkey-type establishment<sup>1)</sup>. Hence, development of a simplified process for industry scale silicon solar cell fabrication has become essential as the proof of concept especially in the case of developing countries as Bangladesh<sup>2)</sup>.

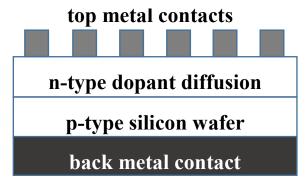

The generalized structure of the industrial silicon wafer based solar cells is shown in figure-1. The basics steps involve in the fabrication of wafer based commercial silicon solar cell are, texturing of p-type silicon wafer, diffusion of n-type dopant and formation of metal contacts. Keeping these three basic steps any inclusion of process that enhances the performance of the solar cell will not contribute to the production cost

significantly. The objective of the study is to develop a simplified process to enhance the electrical performance of the solar cell.

Fig 1. The schematic of the generalized structure of the industrial silicon wafer based solar cells.

At present, after the dopant diffusion in a furnace, the surface passivation and anti-reflection coating (ARC) is

executed using several techniques such as plasma enhanced chemical vapour deposition (PECVD), atomic layer deposition (ALD)<sup>3)</sup>, atmospheric pressure chemical vapor deposition (APCVD) which are separate instrument<sup>4)</sup>. This requires transfer of under processing solar cells from one instrument to another, which introduces risk of contamination, additional cost and wafer handling procedure. The developed simplified process explained in the other literature incorporates phosphorus diffusion<sup>5)</sup>, ARC<sup>6)</sup> and surface passivation<sup>7)</sup> in a single step using the spin on dopant (SOD) process<sup>8)</sup>. In commercial silicon solar cell fabrication process<sup>9)</sup>, diffusion furnaces are widely used for the formation of the n-type emitter layer<sup>10</sup>. Low cost anti-reflection layer can be formed using chemical solution<sup>11)</sup>, spray spin coated system<sup>12)</sup> and sol-gel process<sup>13)</sup>. Multi layered ARC performance for Silicon solar cell was modeled by Silvaco software<sup>14)</sup>. An efficiency of 9.84% for a crystalline silicon solar cell without any ARC was observed and efficiencies of 14% and 14.25% are obtained using TiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> ARC<sup>15</sup>), respectively. The surface passivation is another aspect of improving the performance and degradation of solar cell. The surface passivation increases the open circuit voltage by reducing the surface recombination velocity<sup>16</sup>). Various methods<sup>17)</sup> of surface passivation for the crystalline silicon solar cell is optimized using oxygen and nitrogen atmosphere at temperature range in 850°C -1000°C<sup>18</sup>).

The other kind of low cost thin film solar cell is dye-sensitized solar cell (DSSC)<sup>19),20)</sup>. It uses titanium dioxide (TiO<sub>2</sub>) thin film as the photo anode<sup>21),22)</sup>. The variation in the thickness of the TiO<sub>2</sub> thin film on glass shows an increase in optical band gap<sup>23),24)</sup>. The tuning of optical band gap allows a larger spectrum of electromagnetic wave to be received by the DSSC solar cell which increases the performance of the thin film by enhancing the optical properties <sup>25)</sup>.

In the industry, the simplification of solar cell fabrication process is imperative to the economic output of the product. Other than the growth of thin film on the silicon wafer, there are few techniques that are used to enhance the performance of silicon solar cell without affecting the process. The light trapping technique is widely used to enhance the performance of the silicon solar cell. This technique uses texturing process<sup>26</sup> such as copper nano particle etching to produce light trapping pyramids<sup>27</sup>. The variation in the doping profile in silicon wafer enhances the electrical properties of silicon solar cell<sup>28</sup>,<sup>29</sup>. The contact resistance optimization is another technique that enhances the electrical performances of the silicon solar cell<sup>30</sup>,<sup>31</sup>.

The application of multiple layers of thin film for the performance enhancement of silicon solar cell can be estimated using software<sup>32)</sup>. The multiple layers consist of silicon dioxide and silicon nitride shows an increase in the light absorption which enhances the efficiency of the solar cell. This inclusion of another layer does not affect

the industrial fabrication process rather act as a simplified step<sup>33</sup>).

A theoretical study using PC1D simulation predicted that the efficiency of the solar cell made by following the simplified process can be 20.35% with optimizing effective parameters<sup>34)</sup>. An SOD experimental process showed that a simplified process can be used to fabricate 15% efficient solar cells on c-Si wafers<sup>6)</sup>.

In this study, phosphorous diffusion process was carried on a p-type mono crystalline silicon wafer using a thermal diffusion furnace. This process is used to form the emitter layer followed by wet oxide passivation, silicon dioxide (SiO<sub>2</sub>) ARC formation and annealing under nitrogen flow. All of these steps are performed using a thermal diffusion furnace in one process run. The topographical, optical and electrical characteristic of the processed wafer is evaluated using scanning electron microscope, reflectometer and four-probe setup respectively. The well passivated silicon dioxide (SiO<sub>2</sub>) thin film is widely used by the various industries to produce photovoltaic cells<sup>35</sup>), optoelectronics devices, electronic sensors and transistors<sup>36</sup>).

# 2. Experimental

The experimental process followed in this research includes phosphorus diffusion, anti-reflection coating (ARC) and a surface passivation in two steps in a single chamber. In the thermal diffusion process, phosphorus oxychloride (POCl<sub>3</sub>) served as the dopant source and the final incorporation of the oxygen gas, produced silicon dioxide (SiO<sub>2</sub>) anti-reflection coating as well as surface passivation layer. The annealing of SiO<sub>2</sub> in the presence of N<sub>2</sub> was observed at 600°C using PECVD<sup>37)</sup> which is comparable to the process shown in this study in Table-1. The N<sub>2</sub> purging also provides a contamination and moisture-free inert environment in the diffusion chamber for the entire process.

P type mono crystalline Cz-Si (thickness= $180\pm20\mu m$ , resistivity = 1-3  $\Omega$ -cm, crystal orientation (100), dimension  $125\times125~mm^2$ ) wafers were cleaned by standard Radio Corporation of America (RCA) cleaning process<sup>38</sup>). The saw damaged was removed using high concentration of sodium hydroxide (NaOH) (NaOH:  $H_2O=1:10$ ) at 70°C temperature for 10 minutes for isotropic etching. The wafers were dipped into hydrofluoric (HF) acid solution (HF:  $H_2O=1:50$ ) for 10 seconds followed by rinsing in de-ionized water (DIW) for 1 minute and then dried with nitrogen blow.

The texturing process was performed using potassium hydroxide (KOH) solution (KOH:IPA:DIW=1:5:125) at 70°C temperature for 10 minutes. After that the wafers were dipped into HF solution for 10 seconds, DIW for 1 minute and then dried with nitrogen blow. The recipe is used to produce pyramid shape surface morphology on silicon wafer<sup>39</sup>).

The diffusion process was carried out by using atmospheric pressure chemical vapor deposition

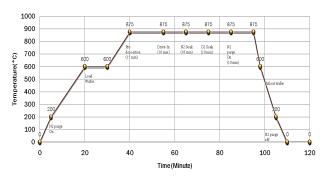

(APCVD) technique in a horizontal tube thermal furnace from Sandvik Thermal Process Inc. CA, USA. The instrument covers an extensive range of temperatures for solar cell processing. It has three tubes, each 48 inches long with three thermal flat zones and compatible for 150 mm diameter substrate. The details of the process steps for the phosphorous diffusion, ARC and wet oxide passivation are given in the Table 1. The temperature profile is shown in Figure 2.

Table 1. The details of process steps for the phosphorous diffusion, anti-reflection coating (ARC) and oxide passivation in thermal diffusion furnace.

| Temp<br>eratur<br>e in<br>°C | Durat<br>ion<br>in<br>minut<br>es | N <sub>2</sub><br>flow<br>rate<br>in<br>liter/<br>min | POCl <sub>3</sub><br>flow<br>rate<br>in<br>liter/<br>min | O <sub>2</sub><br>flow<br>rate<br>in<br>liter/<br>min | Name of<br>Steps                                       |

|------------------------------|-----------------------------------|-------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|

| 200                          | 20                                | 10                                                    | off                                                      | off                                                   | N <sub>2</sub> purge                                   |

| 600                          | 20                                | 10                                                    | off                                                      | off                                                   | Textured<br>wafer<br>loaded                            |

| 875                          | 15                                | off                                                   | 30                                                       | 30                                                    | Phosphoru                                              |

| 875                          | 10                                | 30                                                    | off                                                      | off                                                   | s diffusion                                            |

| 875                          | 10                                | off                                                   | off                                                      | 30                                                    | Surface<br>passivatio<br>n and SiO <sub>2</sub><br>ARC |

| 875                          | 20                                | 30                                                    | off                                                      | off                                                   | N <sub>2</sub> purge annealing                         |

| 600                          | 05                                | 10                                                    | off                                                      | off                                                   | Cooling                                                |

| 200                          | 10                                | 10                                                    | off                                                      | off                                                   | Wafer collection                                       |

**Fig 2.** Temperature profile for the phosphorous diffusion, anti-reflection coating (ARC) and oxide passivation in thermal diffusion furnace.

#### 3. Results and Discussion

The silicon wafers with the layers were characterized for the evaluation of morphological, optical and

electrical properties. The morphological aspects of raw, textured and phosphorus doped silicon wafers were investigated using scanning electron microscope. The reflectance in the visible and infrared range was measured for saw dust removed silicon wafer and phosphorus doped with SiO<sub>2</sub> anti-reflection coated silicon wafer. The thickness of the ARC layer was estimated using reflectometer. The sheet resistivity was calculated from the electrical measurement using collinear four point probe setup.

#### 3.1 Surface morphology analysis

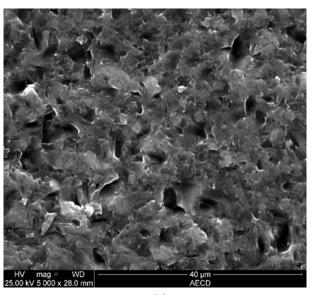

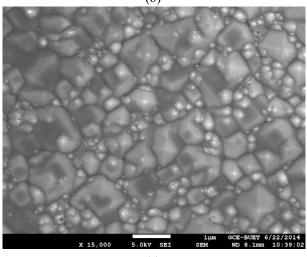

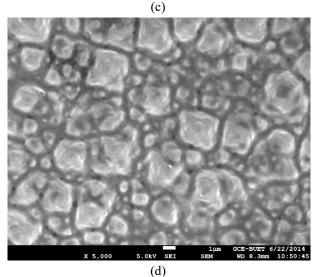

The scanning electron microscope (SEM) model JSM 7600F, from JEOL, Japan was used to observe the grains on raw, cleaned, textured and phosphorus doped silicon wafer which is shown in figure 3. The SEM image of commercial p-type silicon wafer as purchased from Renesola Yixing Co. Ltd. China, shown in figure 3(a), shows saw dust on top of the silicon wafer. After the RCA cleaning the dust is removed and sharp edge silicon grains are seen in figure 3(b). The chemical texturing causes significant changes in the wafer surface shown in figure 3(c). Figure 3(d) shows the wafer topography after the phosphorus diffusion process in the diffusion furnace at 875°C. The phosphorus diffusion along with the ARC layer covers the top of the pyramids, hence the bright spots which were seen in figure 3(c) become broad. Using Veeco Dektak-150 surface profiler for the chemically textured silicon wafer, for 10 minutes etching, the average pyramid height was measured 2.937 µm which is in the range (2-3 µm) suitable for light trapping in photovoltaic devices<sup>40)</sup>. Larger pyramid size of 10-15  $\mu$ m<sup>41)</sup> was observed for etching time of 30-50 minutes<sup>42)</sup>.

(a)

Fig 3. Surface topography images of p-type 200 micron silicon wafer taken by SEM (a) raw silicon wafer (b) saw dust removed silicon wafer (c) chemically textured silicon wafer (d) phosphorus doped, surface passivated and silicon dioxide (SiO<sub>2</sub>) ARC layer on p-type silicon wafer.

## 3.2 Optical reflectance analysis

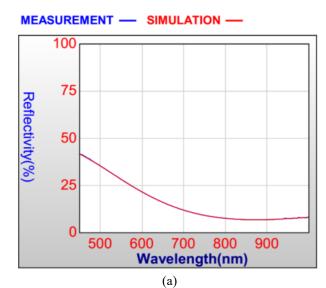

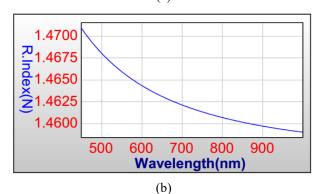

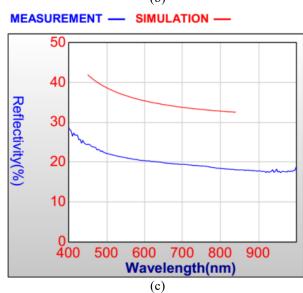

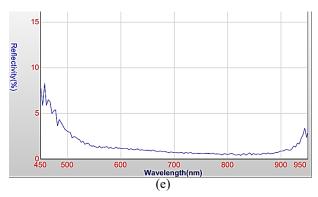

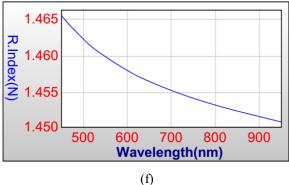

The optical reflectance study was conducted in the visible to near infrared range (400 nm - 1000 nm) using spectroscopic reflectometer from Radiation Technology Inc. Taiwan<sup>43)</sup>. The reflectivity data of visible light from saw dust removed, phosphorus doped and anti-reflection coated silicon wafer was estimated for 400 nm - 1000 nm wavelength shown in Figure 4(a,c,e) and in Table-2.

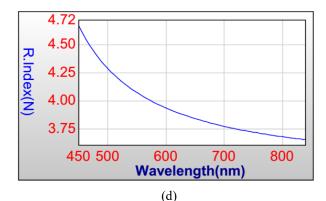

Fig 4. Optical Reflectivity in wavelength range 400 nm – 1000 nm, of (a) SiO<sub>2</sub> on SiCr substrate reference sample for reflectometer calibration (c) saw dust removed RCA cleaned silicon wafer (e) SiO<sub>2</sub> ARC layer on phosphorus doped textured silicon wafer, (b,d,f) corresponding refractive index-wavelength plot

The reflectivity-wavelength graphs in Figure-4(e) shows the reduced optical reflectivity for the phosphorus doped silicon wafer. The percentage of reflectivity is less than 1% in the near infrared region. Table-2 shows the spectroscopic reflectometer data of reference sample, RCA cleaned silicon wafer and phosphorous diffusion, anti-reflection coating (ARC) silicon wafer. The refractive index and thickness of the silicon dioxide (SiO<sub>2</sub>) ARC layer was 1.455 and 101 nm respectively<sup>44</sup>). The reflectivity of the phosphorus doped silicon wafer is in the range similar to other published literatures<sup>45),460</sup>.

Table 2. The spectroscopic reflectometer data of reference sample, RCA cleaned silicon wafer and phosphorous diffusion, anti-reflection coating (ARC) silicon wafer.

| Sample   | Name of   | Mate             | Thick | Refra | Extinctio  |  |

|----------|-----------|------------------|-------|-------|------------|--|

| Name     | layers    | rial             | ness  | ctive | n          |  |

|          |           |                  | in nm | Index | co-efficie |  |

|          |           |                  |       |       | nt         |  |

|          | Ambient   | Void             | -     | 1.000 | 0.000      |  |

| Referenc | Layer-1   | $SiO_2$          | 147   | 1.466 | 0.000      |  |

| e        | Substrate | SiCr             |       | 4.086 | 0.040 at   |  |

|          |           |                  |       |       | 550nm      |  |

| RCA      | Ambient   | Void             | -     | 1.000 | 0.000      |  |

| cleaned  | Substrate | Si100            | -     | 3.871 | 0.016 at   |  |

| Si Wafer |           |                  |       |       | 633nm      |  |

| Phosphor | Ambient   | Void             | -     | 1.000 |            |  |

| ous      | Layer-1   | SiO <sub>2</sub> | 101   | 1.455 |            |  |

| diffused | Substrate | Si100            |       | 3.759 | 0.010 at   |  |

| and ARC  |           |                  |       |       | 710nm      |  |

| wafer    |           |                  |       |       |            |  |

#### 3.3 Electrical properties analysis

The sheet resistance of phosphorus diffused silicon wafer was determined using four point probe setup. The setup consists of a i) manual tungsten probe station from Cascade Microtech, Germany, ii) Agilent 34401A voltmeter form Agilent Technology, Germany and iii) Keithley 6221 AC/DC source from Keithley Instruments, Inc. USA was used to record I-V data manually. The diffused wafers were dipped into hydrofluoric (HF) acid solution (HF49%: H<sub>2</sub>O=1:5) for 1 minute followed by rinsing in de-ionized water (DIW) and dried with nitrogen blow to remove the ARC layer, before the sheet resistivity data was taken. The sheet resistance of raw and phosphorus doped wafer was 115  $\Omega$ /square and 60  $\Omega$ /square, respectively<sup>47)</sup>, which is also in well agreement with the other literatures published earlier for high efficiency silicon solar cells<sup>10</sup>. The solar cell fabricated in the same facility, was 9.63% efficient<sup>48)</sup> following the similar diffusion process with a variation in the texturing, duration of diffusion, gas flow rate and process steps.

#### 4. Conclusion

In this research work, a simplified route was explored to incorporate phosphorus diffusion,  ${\rm SiO_2}$  antireflection coating and oxide passivated p-type silicon wafer in a diffusion furnace. As a result, apart from achieving less than 1% surface reflection from the silicon surface, the diffused wafer shows the sheet resistance of 60  $\Omega$ /square, which are in the most suited parametric ranges for crystalline silicon solar cell fabrication. The diffusion furnace can be further optimized for the silicon nitrite antireflection coating using nitrogen, the thickness of the antireflection coating and the annealing of the surface for better passivation in the presence of nitrogen or oxygen. Innovative fabrication process flow for commercial solar

cell is an ongoing field of research. This focuses on reducing the number of processing steps as well as less use of chemicals or ingredients. The process steps are directly related to the time, cost and human work hour where the use of chemicals directly impact the environment. In addition, the simplified process was carried out with the optimum amount of chemicals to reduce the effect on environment.

#### Acknowledgements

The authors are grateful to Professor Dr Zahid Hasan Mahmood for his continuous guidance and discussion during the experimental procedure. The authors are thankful to Mr. Mahbubul Hoque, Director, Institute of Electronics, Atomic Energy Research Establishment, Savar, Dhaka, Bangladesh, for allowing to use the Solar Cell Fabrication facility.

#### Nomenclature

ARC anti-reflection coating

PECVD plasma enhanced chemical vapour deposition

ALD atomic layer deposition

APCVD atmospheric pressure chemical vapor

deposition

HF Hydrofluoric SiO<sub>2</sub> silicon dioxide IPA Isopropyl alcohol

RCA Radio Corporation of America

DIW De-ionized water

AC/DC Alternating current/ Direct current

#### Greek symbols

$\Omega$  Ohm

$\mathcal{C}$  Degree Celsius  $\mu$  micrometer

#### References

- N. Nurwidiana, B.M. Sopha, and A. Widyaparaga, "Modelling photovoltaic system adoption for households: a systematic literature review," Evergreen, 8 (1) 69–81 (2021). doi:10.5109/4372262.

- 2) K. Marzia, M.F. Hasan, T. Miyazaki, B.B. Saha, and S. Koyama, "Key factors of solar energy progress in bangladesh until 2017," Evergreen, 5 (2) 78–85 (2018). doi:10.5109/1936220.

- D. Hocine, M.S. Belkaid, M. Pasquinelli, L. Escoubas, J.J. Simon, G.A. Rivière, and A. Moussi, "Improved efficiency of multicrystalline silicon solar cells by tio2 antireflection coatings derived by apcvd process," Materials Science in Semiconductor Processing, 16 (1) 113–117 (2013). doi:10.1016/j.mssp.2012.06.004.

- J. Schmidt, R. Peibst, and R. Brendel, "Surface passivation of crystalline silicon solar cells: present and future," Solar Energy Materials and Solar Cells, 187 39–54 (2018). doi:10.1016/j.solmat.2018.06.047.

- 5) V.V. Iyengar, B.K. Nayak, and M.C. Gupta, "Silicon pv devices based on a single step for doping, anti-reflection and surface passivation," Solar Energy Materials and Solar Cells, 94 (12) 2205–2211 (2010). doi:10.1016/j.solmat.2010.07.013.

- 6) Y. Tang, G. Wang, Z. Hu, X. Qin, G. Du, and W. Shi, "Preparation of n+ emitter on p-type silicon wafer using the spin-on doping method," Materials Science in Semiconductor Processing, 15 (4) 359–363 (2012). doi:10.1016/j.mssp.2011.11.003.

- N. Akter, and S. Roy, "Emitter layer formation by spin on doping on mono-crystalline silicon wafer," Microelectronics and Solid State Electronics, 7 (1) 14–18 (2019).

- 8) A. Kuddus, J. Hossain, and A.B.M. Ismail, "The effect of aging on the performance of open-air spin coated zno-cuo bulk heterojunction thin film solar cells," Journal of Optoelectronics and Advanced Materials, 23 (May-June 2021) 237–244 (2021).

- 9) H. Li, K. Kim, B. Hallam, B. Hoex, S. Wenham, and M. Abbott, "POCl3 diffusion for industrial si solar cell emitter formation," Front. Energy, 11 (1) 42–51 (2017). doi:10.1007/s11708-016-0433-7.

- 10) H. Ghembaza, A. Zerga, R. Saïm, and M. Pasquinelli, "Optimization of phosphorus emitter formation from pocl3 diffusion for p-type silicon solar cells processing," Silicon, 10 (2) 377–386 (2018). doi:10.1007/s12633-016-9458-0.

- 11) H.-C. Liu, and G.-J. Wang, "Superior antireflection coating for a silicon cell with a micronanohybrid structure," International Journal of Photoenergy, 2014 807812 (2014). doi:10.1155/2014/807812.

- 12) A. Uzum, M. Kuriyama, H. Kanda, Y. Kimura, K. Tanimoto, H. Fukui, T. Izumi, T. Harada, and S. Ito, "Sprayed and spin-coated multilayer antireflection coating films for nonvacuum processed crystalline silicon solar cells," International Journal of Photoenergy, 2017 3436271 (2017). doi:10.1155/2017/3436271.

- 13) A. Azani, D.S. Che Halin, M.M.A.B. Abdullah, K. Abdul Razak, M. Razak, M. Ramli, M.A.A. Mohd Salleh, and V. Chobpattana, "The effect of go/tio\_2 thin film during photodegradation of methylene blue dye," Evergreen, 8 556–564 (2021). doi:10.5109/4491643.

- 14) A. Lennie, H. Abdullah, S. Shaari, and K. Sopian, "Fabrication of single layer sio2 and si3n4 as antireflection coating on silicon solar cell using silvaco software," American Journal of Applied Sciences, 6 (12) 2043–2049 (2009). doi:10.3844/ajassp.2009.2043.2049.

- 15) B. Swatowska, T. Stapinski, K. Drabczyk, and P.

- Panek, "The role of antireflective coatings in silicon solar cells the influence on their electrical parameters," Optica Applicata, Vol. 41 (nr 2) 487–492 (2011).

- 16) M. Ju, N. Balaji, C. Park, H.T.T. Nguyen, J. Cui, D. Oh, M. Jeon, J. Kang, G. Shim, and J. Yi, "The effect of small pyramid texturing on the enhanced passivation and efficiency of single c-si solar cells," RSC Adv., 6 (55) 49831–49838 (2016). doi:10.1039/C6RA05321A.

- 17) M.Z. Rahman, and S.I. Khan, "Advances in surface passivation of c-si solar cells," Mater Renew Sustain Energy, 1 (1) 1 (2012). doi:10.1007/s40243-012-0001-y.

- 18) A. ur Rehman, M.Z. Iqbal, M.F. Bhopal, M.F. Khan, F. Hussain, J. Iqbal, M. Khan, and S.H. Lee, "Development and prospects of surface passivation schemes for high-efficiency c-si solar cells," Solar Energy, 166 90–97 (2018). doi:10.1016/j.solener.2018.03.025.

- 19) M.K. Hossain, M.F. Pervez, S. Tayyaba, M.J. Uddin, A.A. Mortuza, M.N.H. Mia, M.S. Manir, M.R. Karim, and M.A. Khan, "Efficiency enhancement of natural dye sensitized solar cell by optimizing electrode fabrication parameters," Materials Science-Poland, 35 (4) 816–823 (2017). doi:10.1515/msp-2017-0086.

- 20) M.K. Hossain, M.F. Pervez, M.N.H. Mia, S. Tayyaba, M.J. Uddin, R. Ahamed, R.A. Khan, M. Hoq, M.A. Khan, and F. Ahmed, "Annealing temperature effect on structural, morphological and optical parameters of mesoporous tio film photoanode for dye-sensitized solar cell application," Materials Science-Poland, 35 (4) 868–877 (2017). doi:10.1515/msp-2017-0082.

- 21) M.K. Hossain, M.T. Rahman, M.K. Basher, M.J. Afzal, and M.S. Bashar, "Impact of ionizing radiation doses on nanocrystalline tio2 layer in dssc's photoanode film," Results in Physics, 11 1172–1181 (2018). doi:10.1016/j.rinp.2018.10.006.

- 22) M.K. Hossain, M.T. Rahman, M.K. Basher, M.S. Manir, and M.S. Bashar, "Influence of thickness variation of gamma-irradiated dssc photoanodic tio2 film on structural, morphological and optical properties," Optik, 178 449–460 (2019). doi:10.1016/j.ijleo.2018.09.170.

- 23) M.K. Hossain, M.F. Pervez, M.J. Uddin, S. Tayyaba, M.N.H. Mia, M.S. Bashar, M.K.H. Jewel, M. a. S. Haque, M.A. Hakim, and M.A. Khan, "Influence of natural dye adsorption on the structural, morphological and optical properties of tio based photoanode of dye-sensitized solar cell," Materials Science-Poland, 36 (1) 93–101 (2018). doi:10.1515/msp-2017-0090.

- 24) Md.K. Hossain, M.F. Pervez, M.N.H. Mia, A.A. Mortuza, M.S. Rahaman, M.R. Karim, J.M.M. Islam, F. Ahmed, and M.A. Khan, "Effect of dye extracting

- solvents and sensitization time on photovoltaic performance of natural dye sensitized solar cells," Results in Physics, 7 1516–1523 (2017). doi:10.1016/j.rinp.2017.04.011.

- 25) M.K. Hossain, A.A. Mortuza, S.K. Sen, M.K. Basher, M.W. Ashraf, S. Tayyaba, M.N.H. Mia, and M.J. Uddin, "A comparative study on the influence of pure anatase and degussa-p25 tio2 nanomaterials on the structural and optical properties of dye sensitized solar cell (dssc) photoanode," Optik, 171 507–516 (2018). doi:10.1016/j.ijleo.2018.05.032.

- 26) M.K. Basher, R. Mishan, S. Biswas, M. Khalid Hossain, M. a. R. Akand, and M.A. Matin, "Study and analysis the cu nanoparticle assisted texturization forming low reflective silicon surface for solar cell application," AIP Advances, 9 (7) 075118 (2019). doi:10.1063/1.5109003.

- 27) M.K. Basher, M.K. Hossain, M.J. Uddin, M.A.R. Akand, and K.M. Shorowordi, "Effect of pyramidal texturization on the optical surface reflectance of monocrystalline photovoltaic silicon wafers," Optik, 172 801–811 (2018). doi:10.1016/j.ijleo.2018.07.116.

- 28) M.K. Basher, M.J. Uddin, M.K. Hossain, M.A.R. Akand, S. Biswas, M.N.H. Mia, and K.M. Shorowordi, "Effect of doping profile on sheet resistance and contact resistance of monocrystalline silicon solar cells," Mater. Res. Express, 6 (8) 085510 (2019). doi:10.1088/2053-1591/ab1e8c.

- 29) S. Biswas, M.K. Basher, M.K. Hossain, M.A.R. Akand, M.T. Rahman, M.R. Ahmed, M.A. Matin, and S. Huque, "Study and analysis of the morphological, elemental and electrical properties of phosphorus doped monocrystalline silicon solar cell," Mater. Res. Express, 6 (5) 055515 (2019). doi:10.1088/2053-1591/ab070b.

- 30) R.A. Amin, M.F. Pervez, M.N.H. Mia, M.K. Hossain, S.M. Rana, N.A. Khan, M. a. S. Haque, H.K. Ghosh, and M. Hoq, "Influence of different metals back surface field on bsf silicon solar cell performance deposited by thermal evaporation method," Advances in Energy and Power, 5 (3) 27–31 (2017). doi:10.13189/aep.2017.050301.

- 31) M.K. Basher, M. Khalid Hossain, R. Afaz, S. Tayyaba, M.A.R. Akand, M.T. Rahman, and N.M. Eman, "Study and investigation of phosphorus doping time on emitter region for contact resistance optimization of monocrystalline silicon solar cell," Results in Physics, 10 205–211 (2018). doi:10.1016/j.rinp.2018.05.038.

- 32) A. Acevedo-Luna, R. Bernal-Correa, J. Montes-Monsalve, and A. Morales-Acevedo, "Design of thin film solar cells based on a unified simple analytical model," Journal of Applied Research and Technology, 15 (6) 599–608 (2017). doi:10.1016/j.jart.2017.08.002.

- 33) R.S. Dubey, K. Jhansirani, and S. Singh,

- "Investigation of solar cell performance using multilayer thin film structure (sio2/si3n4) and grating," Results in Physics, 7 77–81 (2017). doi:10.1016/j.rinp.2016.11.065.

- 34) G. Hashmi, A.R. Akand, M. Hoq, and H. Rahman, "Study of the enhancement of the efficiency of the monocrystalline silicon solar cell by optimizing effective parameters using pc1d simulation," Silicon, 10 (4) 1653–1660 (2018). doi:10.1007/s12633-017-9649-3.

- 35) J. Schmidt, R. Peibst, and R. Brendel, "Surface passivation of crystalline silicon solar cells: present and future," Solar Energy Materials and Solar Cells, 187 39–54 (2018). doi:10.1016/j.solmat.2018.06.047.

- 36) S.K. Kim, and R. Hattori, "Study of contact resistance on organic thin-film transistor with surface treatments," Evergreen, 2 (1) 1–5 (2015). doi:10.5109/1500421.

- 37) K.H. Tan, and M. Muhamad, "The bonding modes and optical characteristics of annealed silicon oxide thin films prepared by plasma enhanced cvd," Malaysian Journal of Science, 16 (2) 13–16 (2017).

- 38) K.A. Reinhardt, and W. Kern, eds., "Front Matter," in: Handbook of Silicon Wafer Cleaning Technology (Third Edition), William Andrew Publishing, 2018: p. iii. doi:10.1016/B978-0-323-51084-4.01001-7.

- 39) U. Gangopadhyay, S. Jana, S. Das, and P. Ghosh, "Novel and efficient texturing approach for large-scale industrial production line of large-area monocrystalline silicon solar cell," Mater Renew Sustain Energy, 2 (3) 1–9 (2013). doi:10.1007/s40243-013-0015-0.

- 40) G. Hashmi, M. Hasanuzzaman, M.K. Basher, M. Hoq, and Md.H. Rahman, "Texturization of as-cut p-type monocrystalline silicon wafer using different wet chemical solutions," Appl. Phys. A, 124 (6) 415 (2018). doi:10.1007/s00339-018-1818-8.

- 41) M. Moreno, D. Murias, J. Martínez, C. Reyes-Betanzo, A. Torres, R. Ambrosio, P. Rosales, P. Roca i Cabarrocas, and M. Escobar, "A comparative study of wet and dry texturing processes of c-si wafers for the fabrication of solar cells," Solar Energy, 101 182–191 (2014). doi:10.1016/j.solener.2014.01.004.

- 42) A.A. Fashina, K.K. Adama, M.G. Zebaze Kana, and W.O. Soboyejo, "Improving the performance of light trapping in crystalline silicon solar cell through effective surface texturing," Advanced Materials Research, 1132 144–159 (2016). doi:10.4028/www.scientific.net/AMR.1132.144.

- 43) M. Anzan-Uz-Zaman, M. Aliuzzaman, A. Hossion, M. Nasrul, Md.N. Mia, M. Alam, and H. Ghosh, "Calibration of Spectroscopic Reflectometer for Thin Film Characterization," 2012. doi:10.5281/zenodo.4017167.

- 44) B.L. Sopori, "Principle of a new reflectometer for

- measuring dielectric film thickness on substrates of arbitrary surface characteristics," Review of Scientific Instruments, 59 (5) 725–727 (1988). doi:10.1063/1.1139817.

- 45) M. Li, H. Shen, L. Zhuang, D. Chen, and X. Liang, "SiO2 antireflection coatings fabricated by electron-beam evaporation for black monocrystalline silicon solar cells," International Journal of Photoenergy, 2014 670438 (2014). doi:10.1155/2014/670438.

- 46) G. Hashmi, M.J. Rashid, Z.H. Mahmood, M. Hoq, and Md.H. Rahman, "Investigation of the impact of different arc layers using pc1d simulation: application to crystalline silicon solar cells," J Theor Appl Phys, 12 (4) 327–334 (2018). doi:10.1007/s40094-018-0313-0.

- 47) N. Akter, S. Afrin, A. Hossion, S. Afrin, A. Kabir, S. Akter, and Z. Mahmood, "Evaluation of majority charge carrier and impurity concentration using hot probe method for mono crystalline silicon (100) wafer," IJAMSE, 4 (4) 13–21 (2015). doi:10.14810/ijamse.2015.4402.

- 48) M.K. Basher, M.K. Hossain, and M.A.R. Akand, "Effect of surface texturization on minority carrier lifetime and photovoltaic performance of monocrystalline silicon solar cell," Optik, 176 93–101 (2019). doi:10.1016/j.ijleo.2018.09.042