九州大学学術情報リポジトリ Kyushu University Institutional Repository

# High-performance cryogenic computing using superconductor single flux quantum logic

石田, 浩貴

https://hdl.handle.net/2324/4475154

出版情報:九州大学,2020,博士(工学),課程博士 バージョン: 権利関係:

# High-Performance Cryogenic Computing Using Superconductor Single Flux Quantum Logic

Koki Ishida

# A DISSERTATION

Kyushu University

March, 2021

# High-Performance Cryogenic Computing Using Superconductor Single Flux Quantum Logic

### Koki Ishida

### Abstract

Processors, the essential part of computer systems, have dramatically improved their performance with transistors' shrinking technology since the first processors are developed in the early 1970s. However, around the 2000s, the problem of power consumption became apparent, and it became hard to improve the clock frequency, which significantly contributed to the improvement of performance. Although processors' performance improvement has been maintained by introducing multi-core designs, it will be challenging to improve chip performance only with conventional CMOS computing technology continuously after the end of transistors' scaling.

To solve these problems, this dissertation focuses on a cryogenic computing technology using superconductor single flux quantum (SFQ) logic that has both high speed and low power consumption. SFQ logic uses low-voltage impulseshaped signals for logic operations, which allows the ultra-fast  $(10^{-12}s)$  and lowenergy switching  $(10^{-19}J)$ . Due to these potentials, several researchers have so far contributed to SFQ-related research, and several physical implementations, including processors, have successfully demonstrated at the outstanding frequency, e.g., several tens of GHz. However, this is the performance at the logic gate level in the circuit, and when converted to the processor's performance based on software execution, it remains at the same level as conventional CMOS processors. The fundamental problem existing behind the SFQ processors is the lack of architectural optimizations to exploit the full potential of SFQ devices. Moreover, although several circuits' demonstrations have successfully shown the device-level potential, few studies focus on the architectural unit designs to show the SFQ computing potential. Therefore, the following questions must be clearly addressed to show the SFQ computing's potential: (1) what architecture is promising for this technology, (2) how is the feasibility and effectiveness of the architecture, (3) how to evaluate the effective performance and power efficiency of the target designs.

To solve the problem, this dissertation firstly explores the architectural design space of SFQ processors to determine the basic design guidelines for the realization of high-performance SFQ processors. Specifically, we assume a simple processor (i.e., in-order scalar processor) and analyze the effect of two architectural parameters (i.e., instruction pipeline stages and bit-width) on performance and power consumption. As a result, the bit-parallel processing and gate-level deep pipeline structure are suitable for achieving high performance in SFQ processors. Moreover, the result indicates that SFQ processors must conceal almost all pipeline stalls to achieve high performance in such an ultra-deep pipelining.

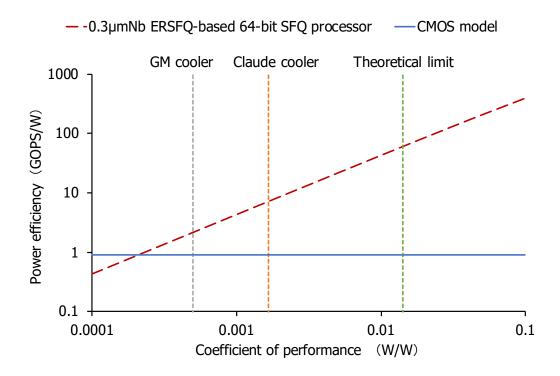

Second, this dissertation designs and implements a 4-bit SFQ processor chip as a prototype to clarify our proposed architectural design guidelines' effectiveness and feasibility. As a result, we confirm the correct operation at 32 GHz of clock frequency with 6.5 mW of power consumption. Moreover, this dissertation has extended into the 64-bit processor based on these results and evaluated its power efficiency with the cooling overhead for keeping SFQ circuits at 4 kelvin. The power efficiency, including the cooling cost, is estimated to at most 7.1 GOPS/W, and our processor outperforms the CMOS processor model 7.8 times.

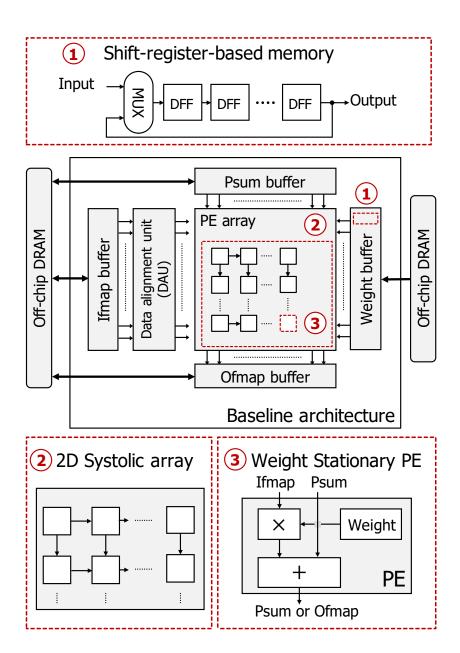

Third, this dissertation proposes and evaluates the SFQ accelerator design for neural network applications to show the real potential of SFQ computing. Specifically, this dissertation designs the basic architecture of the neural network accelerator based on the basic design guidelines for SFQ processors and develops an evaluation environment based on power performance modeling. Besides, we analyze the performance bottleneck and optimize the architecture. As a result of the evaluation, our design outperforms about 23 and 1.2 times higher performance and power efficiency with the cooling cost compared to a state-of-the-art CMOS accelerator, respectively.

# Contents

| 1        | Intr | oduction                                                           | 1        |

|----------|------|--------------------------------------------------------------------|----------|

|          | 1.1  | Challenges in the conventional CMOS computing                      | 1        |

|          | 1.2  | Cryogenic computing using superconductor single flux quantum logic |          |

|          |      | and its challenges                                                 | 2        |

|          | 1.3  | Thesis statement                                                   | 3        |

|          | 1.4  | Contributions                                                      | 3        |

|          | 1.5  | Dissertation Organization                                          | 4        |

| <b>2</b> | Bac  | ground                                                             | <b>5</b> |

|          | 2.1  | Trend and challenges of CMOS processors                            | 5        |

|          | 2.2  | Cryogenic computing                                                | 7        |

|          |      | 2.2.1 Low-temperature CMOS computing                               | 7        |

|          |      | 2.2.2 Superconducting computing                                    | 8        |

|          |      | 2.2.3 Quantum computing                                            | 9        |

|          | 2.3  | Superconductor single flux quantum logic                           | 9        |

|          |      |                                                                    | 10       |

|          |      |                                                                    | 11       |

|          |      | 2.3.3 Frequency determination                                      | 15       |

|          |      | 2.3.4 Power consumption                                            | 18       |

|          | 2.4  | Current status and research trend of SFQ technology                | 19       |

|          |      | 2.4.1 Fabrication process technology                               | 19       |

|          |      |                                                                    | 20       |

|          |      |                                                                    | 21       |

|          |      | 2.4.4 Memory technology                                            | 21       |

| 3        | Exp  | oring design space of a SFQ processor                              | 23       |

|          | 3.1  | Introduction                                                       | 23       |

|          | 3.2  |                                                                    | 24       |

|          |      | · · · · ·                                                          | 24       |

|          |      | •                                                                  | 25       |

|          |      |                                                                    | 26       |

|          | 3.3  |                                                                    | 29       |

|          |      |                                                                    | 29       |

|          |      |                                                                    | 31       |

|          | 3.4 |                                                                                                                                                        | 34         |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 3.5 | Conclusions                                                                                                                                            | 36         |

| 4        | Pro | totype design of SFQ processor 3                                                                                                                       | 87         |

|          | 4.1 |                                                                                                                                                        | 37         |

|          | 4.2 |                                                                                                                                                        | 38         |

|          | 1.2 |                                                                                                                                                        | 38         |

|          |     | 8 0                                                                                                                                                    | 39         |

|          |     |                                                                                                                                                        | 40         |

|          |     |                                                                                                                                                        | 10         |

|          | 4.3 | I O                                                                                                                                                    | 15         |

|          | 1.0 |                                                                                                                                                        | 15<br>15   |

|          |     |                                                                                                                                                        | 17         |

|          |     | 6 6                                                                                                                                                    | ±1<br>19   |

|          | 4.4 |                                                                                                                                                        | ± <i>5</i> |

|          | 7.7 |                                                                                                                                                        | 50         |

|          |     | 1                                                                                                                                                      | 51         |

|          |     | -                                                                                                                                                      | 52         |

|          |     | 1                                                                                                                                                      | 55         |

|          | 4.5 |                                                                                                                                                        | 58         |

|          | 4.0 |                                                                                                                                                        | 10         |

| <b>5</b> | Ext | remely fast SFQ neural processing unit architecture 5                                                                                                  | <b>5</b> 9 |

|          | 5.1 | Introduction                                                                                                                                           | 59         |

|          | 5.2 | Background & Motivation                                                                                                                                | 52         |

|          |     | 5.2.1 SFQ technology in the architect's perspective 6                                                                                                  | 52         |

|          |     | 5.2.2 Challenges for designing SFQ-based architectural unit 6                                                                                          | 54         |

|          |     | 5.2.3 Research goal: Provide SFQ design principles with NPU 6                                                                                          | 55         |

|          | 5.3 | Baseline SFQ-based NPU design                                                                                                                          | 35         |

|          |     | 5.3.1 On-chip network unit design                                                                                                                      | 37         |

|          |     | 5.3.2 PE design $\ldots \ldots \ldots$ | 58         |

|          |     | 5.3.3 Data alignment unit design                                                                                                                       | 71         |

|          | 5.4 | Simulation framework                                                                                                                                   | 73         |

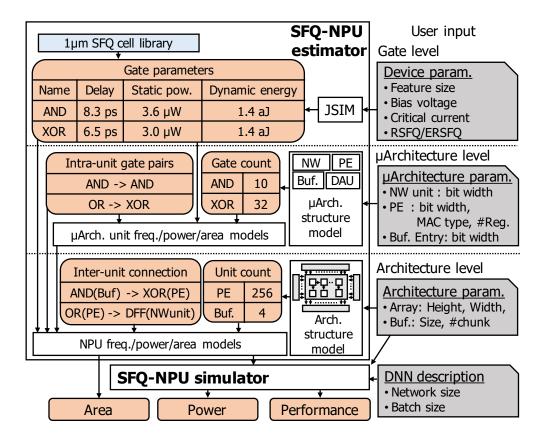

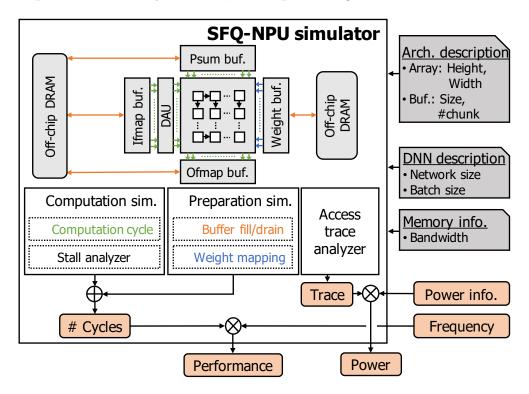

|          |     | 5.4.1 SFQ-NPU estimator                                                                                                                                | 73         |

|          |     | 5.4.2 SFQ-NPU simulator                                                                                                                                | 78         |

|          | 5.5 | Optimizing SFQ-based NPU design                                                                                                                        | 79         |

|          |     | 5.5.1 Design implications for the SFQ-optimal NPU architecture . 7                                                                                     | 79         |

|          |     | 5.5.2 SuperNPU: SFQ-optimal NPU architecture                                                                                                           | 33         |

|          | 5.6 |                                                                                                                                                        | 38         |

|          |     |                                                                                                                                                        | 38         |

|          |     | 0.                                                                                                                                                     | 90         |

|          |     |                                                                                                                                                        | 92         |

|          |     | -                                                                                                                                                      | )3         |

|          | 5.7 | U U U U U U U U U U U U U U U U U U U                                                                                                                  | 94         |

|          | 5.8 |                                                                                                                                                        | 95         |

|          |     |                                                                                                                                                        |            |

| 6 Conclusions                      | 97  |

|------------------------------------|-----|

| List of Publications by the Author | 103 |

| References                         | 104 |

# List of Figures

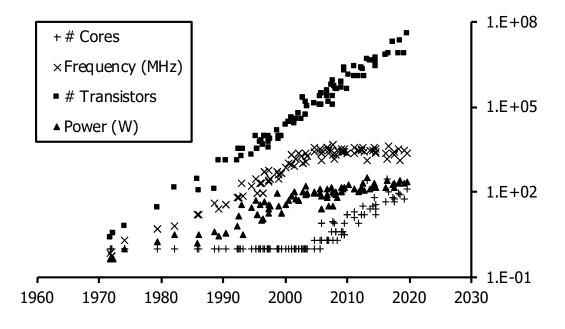

| 2.1  | 48-year CMOS processors' trend                                        | 6              |

|------|-----------------------------------------------------------------------|----------------|

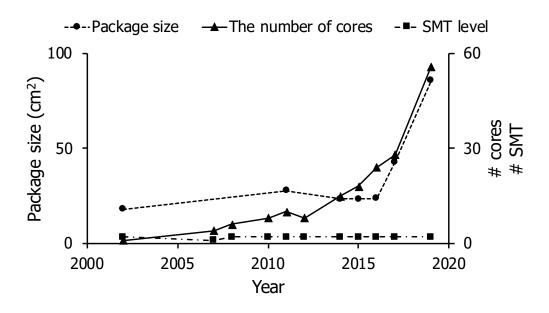

| 2.2  | Trends of Intel Xeon processors over generations                      | $\overline{7}$ |

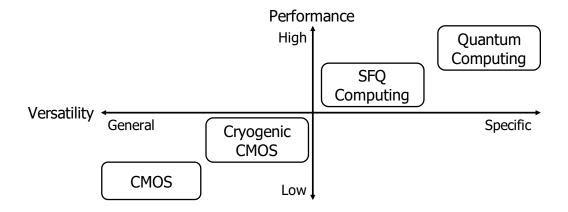

| 2.3  | Classification of computing technologies                              | 8              |

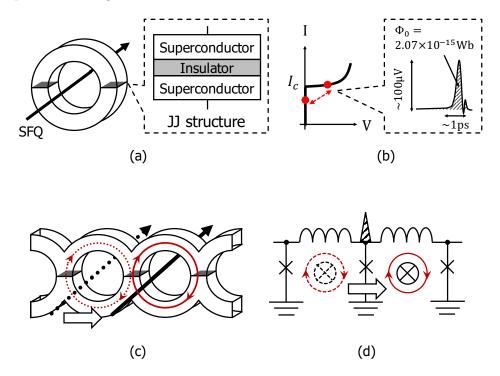

| 2.4  | (a) Superconductor ring with SFQ (b) Electrical characteristics of    |                |

|      | JJ (c) Serially connected SFQ rings and (d) its equivalent circuit    |                |

|      | diagram                                                               | 10             |

| 2.5  | (a) Circuit diagram of an SFQ-based DFF with (b) its operating        |                |

|      | example                                                               | 11             |

| 2.6  | (a) SFQ-based AND gate with (b) its circuit diagram                   | 12             |

| 2.7  | Operating examples of SFQ AND gate                                    | 13             |

| 2.8  | Operating example of the serially connected DFFs                      | 14             |

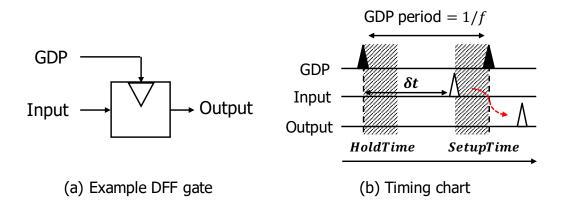

| 2.9  | Example timing chart of an SFQ DFF gate                               | 15             |

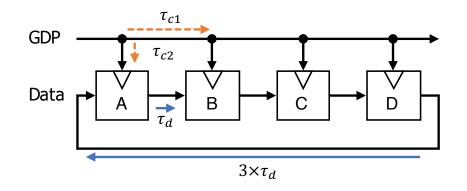

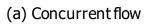

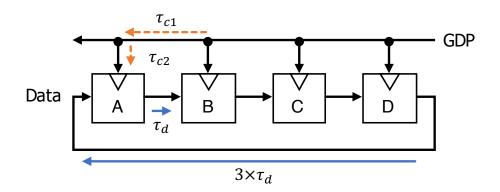

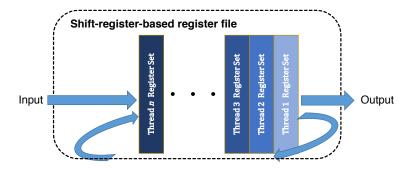

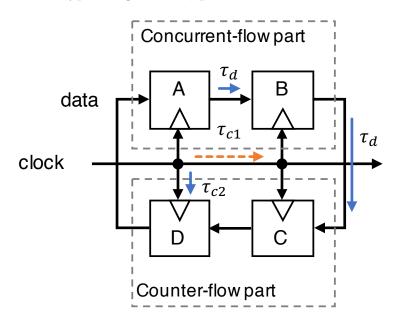

| 2.10 | Illustration of flow clocking schemes (a) Concurrent-flow clocking    |                |

|      | (b) Counter-flow clocking (c) Comparison of $\delta t$                | 17             |

| 2.11 | Circuit diagram of a biased JJ                                        | 18             |

| 0.1  |                                                                       | 00             |

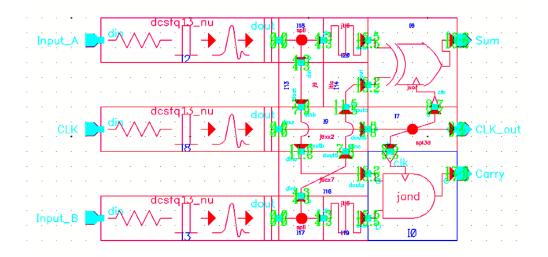

| 3.1  | Gate-level circuit diagram of the SFQ adder.                          | 28             |

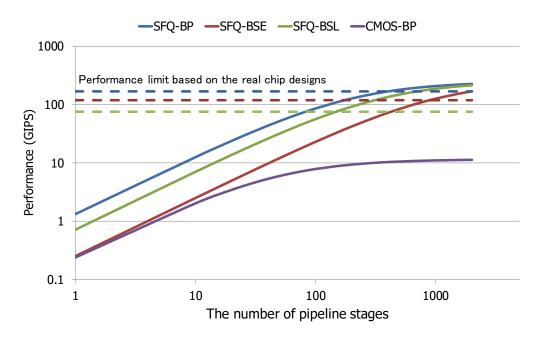

| 3.2  | Performance comparison with fixed pipelines                           | 30             |

| 3.3  | Performance comparison with variable pipeline stages                  | 31             |

| 3.4  | Performance comparison between SFQ-BP and CMOS-BP consid-             | 20             |

| 25   | ering the ratio of the average pipeline stall $\gamma$                | 32             |

| 3.5  | Performance comparison between SFQ-BP and CMOS-BP consid-             | 33             |

| 26   | ering the pipeline stall concealment rate $\theta$                    |                |

| 3.6  | Overview of the proposed design policy                                | 34             |

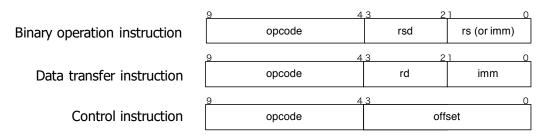

| 4.1  | Instruction format                                                    | 40             |

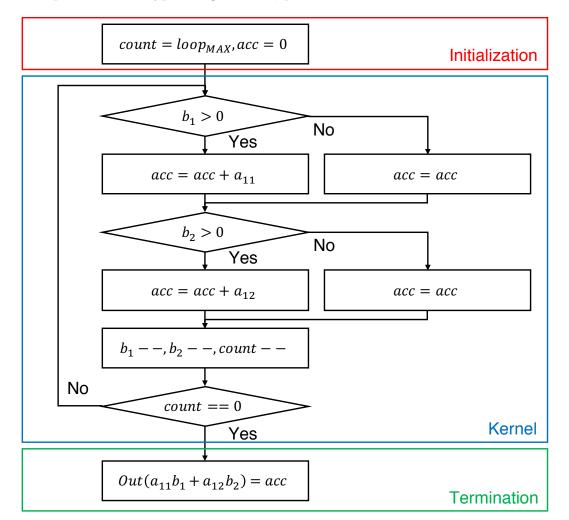

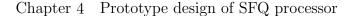

| 4.2  | Algorithm of the 2-by-2 matrix-vector product                         | 42             |

| 4.3  | Operating flow chart of the 2-by-2 matrix-vector product              | 44             |

| 4.4  | The layout of 1-bit half adder                                        | 45             |

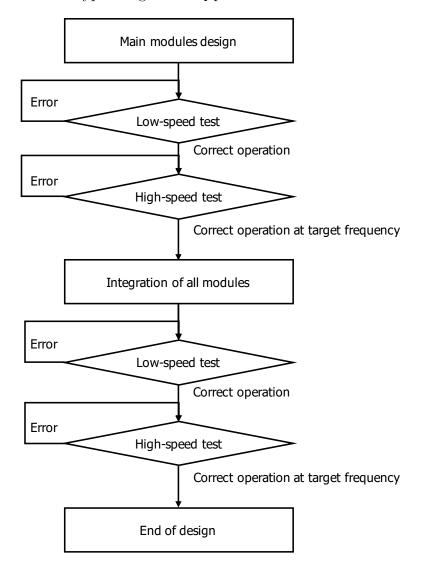

| 4.5  | Design flow of the prototype processor                                | 46             |

| 4.6  | Shift-register-based register file for fine-grained multithreading    | 47             |

| 4.7  | Brahen clocking: combination of concurrent- and counter-flow clocking | 48             |

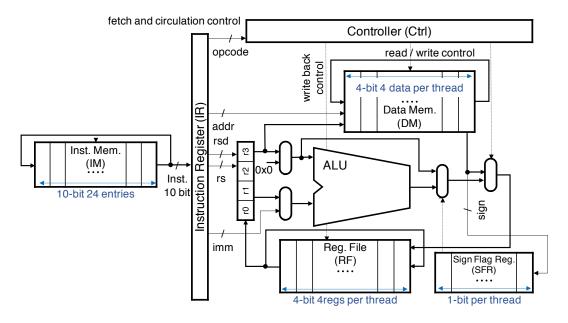

| 4.8  | Microarchitecture of prototype processor                              | 49             |

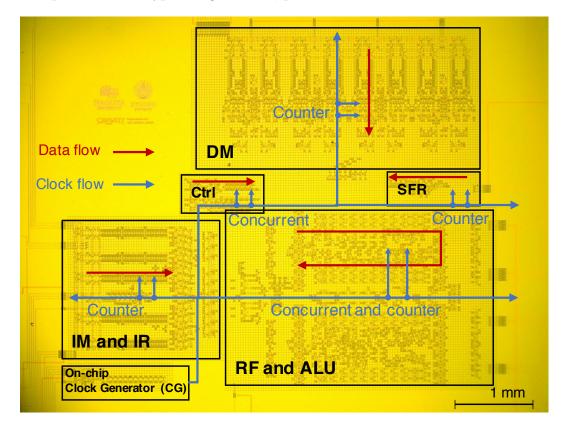

| 4.9  | Microphotograph of the 4-bit processor chip                           | 51             |

|      |                                                                       |                |

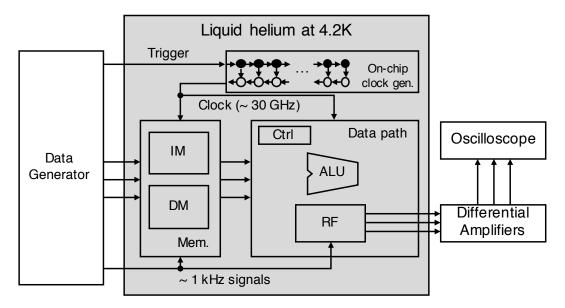

| 4.10         | Chip measurement setup                                                   | 52 |

|--------------|--------------------------------------------------------------------------|----|

| 4.11         | Illustration of on-chip high-speed testing                               | 53 |

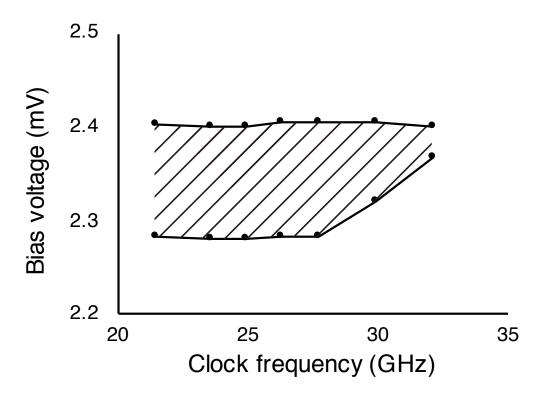

| 4.12         | Frequency dependence of operating margin in supply voltage               | 54 |

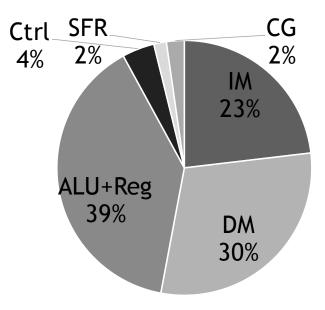

| 4.13         | Power consumption breakdown of the processor                             | 55 |

| 4.14         | Power efficiency comparison between 64-bit SFQ processor and CMOS        |    |

|              | processor model                                                          | 57 |

| 5.1          | Example of the SFQ technology's architectural characteristics (a)        |    |

| 0.1          | Gate-level-pipelined datapath (b) 1-bit N-entry shift register           | 62 |

| 5.2          | Overview of our baseline SFQ-based NPU design                            | 66 |

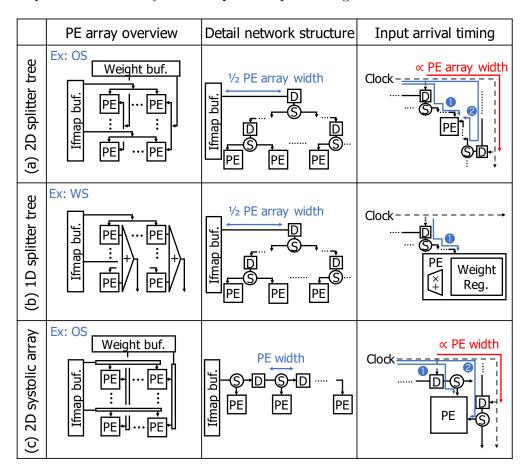

| $5.2 \\ 5.3$ | On-chip network structure for three alternative designs                  | 68 |

| $5.3 \\ 5.4$ | Network unit designs' (a) critical-path delay and (b) area comparison    | 69 |

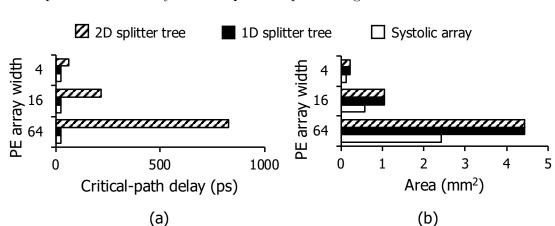

| $5.4 \\ 5.5$ | PE designs with two different dataflows                                  | 69 |

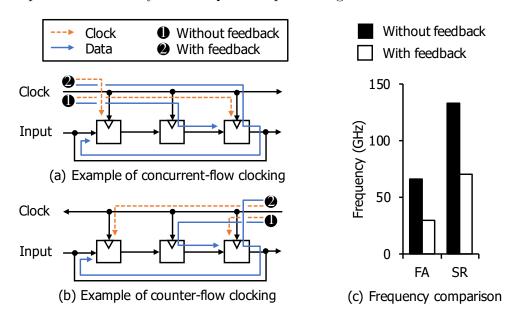

| 5.6          | Feedback loop's impact on the frequency of SFQ circuits                  | 70 |

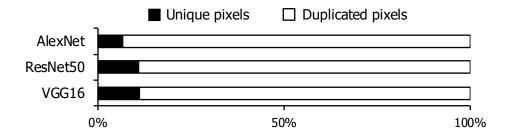

| 5.7          | Data ratio breakdown for unique and duplicated ifmap pixels              | 71 |

| 5.8          | Data alignment unit's structure with the working example                 | 71 |

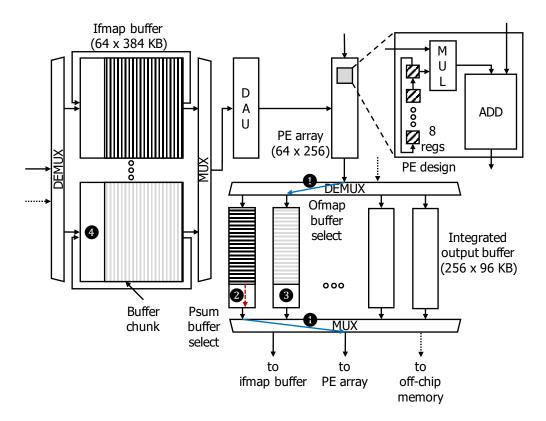

| 5.9          | SFQ-NPU overview                                                         | 73 |

| 5.10         | Frequency model illustration                                             | 75 |

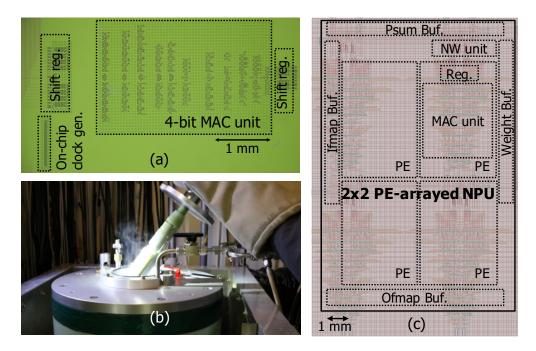

| 5.11         | Model validation setup (a) Chip microphotograph of 4-bit MAC             |    |

|              | unit (b) 4 K measurement setup (c) Layout of the $2 \times 2$ PE-arrayed |    |

|              | NPU                                                                      | 76 |

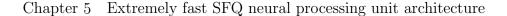

| 5.12         | Model validation result                                                  | 77 |

| 5.13         | SFQ-NPU simulator overview                                               | 78 |

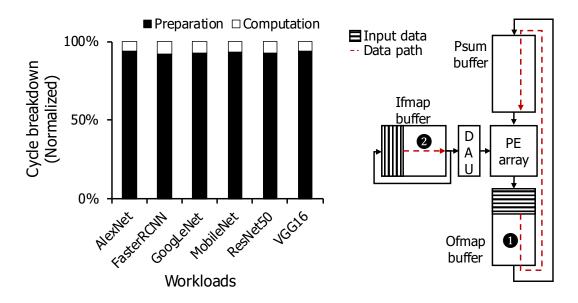

| 5.14         | Baseline's cycle breakdown normalized for each CNN workload              | 80 |

| 5.15         | Example data path of on-chip buffers                                     | 80 |

| 5.16         | Limited performance improvement in Baseline due to the low com-          |    |

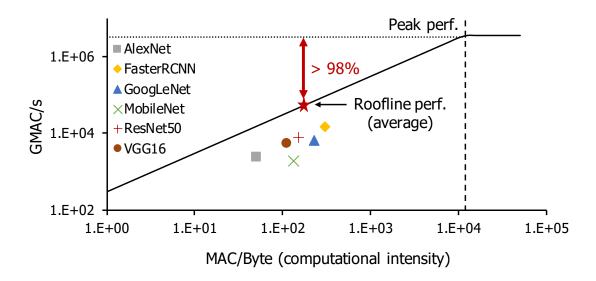

|              | putational intensity with a single batch                                 | 82 |

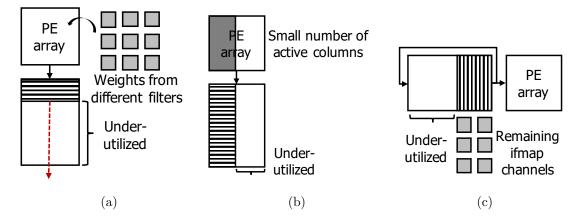

| 5.17         | On-chip buffer under-utilization in terms of (a) ofmap buffer's length,  |    |

|              | (b) ofmap buffer's width, and (c) ifmap buffer's length                  | 83 |

| 5.18         | SuperNPU overview                                                        | 84 |

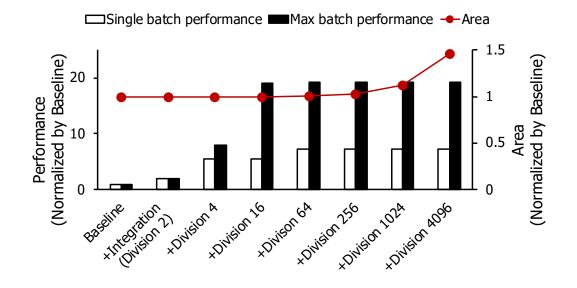

| 5.19         | Performance impact and area overhead of the buffer optimizations .       | 85 |

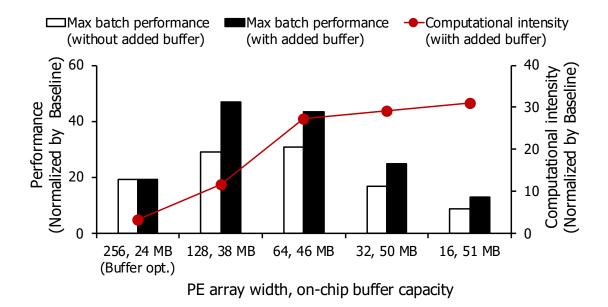

| 5.20         | Performance and computational intensity with resource balancing .        | 85 |

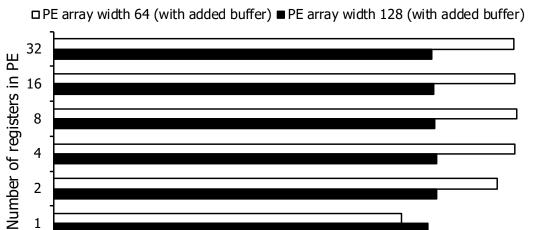

| 5.21         | Performance impact of number of registers in PE                          | 87 |

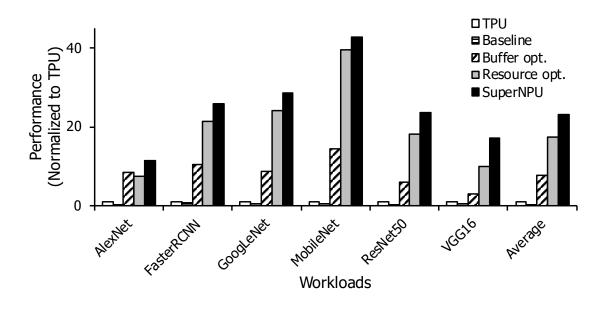

| 5.22         | Performance evaluation                                                   | 90 |

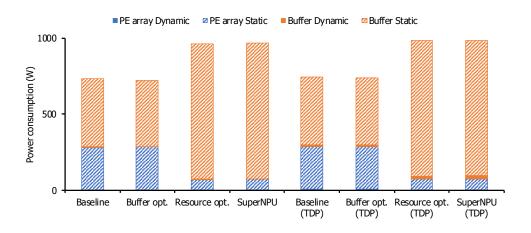

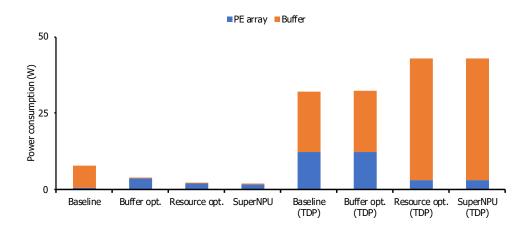

| 5.23         | Power consumption breakdown of RSFQ-based NPU                            | 92 |

| 5.24         | Power consumption breakdown of ERSFQ-based NPU                           | 92 |

|              |                                                                          |    |

# List of Tables

| 3.1 | Delay parameters                                  | 26 |

|-----|---------------------------------------------------|----|

| 4.1 | Instruction set                                   | 40 |

| 4.2 | Assembly code of the 2-by-2 matrix-vector product | 43 |

| 4.3 | The number of JJs of each 64-bit extended module  | 53 |

| 4.4 | Parameters                                        | 56 |

| 4.5 | CMOS processor model's parameters                 | 56 |

| 5.1 | Evaluation setup                                  | 89 |

| 5.2 | Workload setup (batch size)                       | 90 |

| 5.3 | Power-efficiency evaluation                       | 93 |

# Chapter 1

# Introduction

# 1.1 Challenges in the conventional CMOS computing

Processors are essential and fundamental components of various computer systems, e.g., computer servers, personal computers, and embedded systems. The processors' performance has continuously improved thanks to Moore's Law, the observation in which the number of transistors in a chip doubles every 18 months. Until the early 2000s, the processors have achieved their performance improvements by mainly increasing its frequency. However, in the early 2000s, the device scaling became ineffective in increasing the chip frequency because of the negligible power dissipation, i.e., power wall problem.

To get around the power wall problem, architects have introduced relatively slow multi- or many-core designs to improve chip performance continuously. Nevertheless, these circumventions can suffer from the parallelization overhead and the increasing on-chip power consumption. Moreover, while device and manufacturing technologies have continued progressing, it seems challenging to maintain the transistors shrinking because of physical or economic reasons, i.e., the end of Moore's Law is coming. After the end of Moore's Law, we are running out of an effective option to improve computer systems' performance while maintaining its power budget. Therefore, we believe that it is the right time to actively exploit emerging device technologies with significant potentials and make a serious effort to improve their feasibility by resolving their limitations.

# 1.2 Cryogenic computing using superconductor single flux quantum logic and its challenges

Cryogenic computing, which is to run a computer device at extremely low temperatures, is an attractive direction to make a breakthrough for achieving sustainable improvement of computer systems in the post-Moore's era. Among several candidates, superconductor single-flux-quantum (SFQ) logic [49, 58] and its energyefficient families [43, 84, 86, 89, 78] are highly promising solutions thanks to their ultra-fast speed and low-power consumption at 4 kelvin. SFQ logic uses low-voltage impulse-shaped signals for logic operations, which allows the ultra-fast ( $10^{-12}$ s) and low-energy switching ( $10^{-19}$ J). Because of these potentials, several researchers have so far contributed to SFQ-related research in various aspects, especially in the device and circuit area. There are physical implementations, including processors, that have successfully demonstrated at the outstanding frequency, e.g., several tens of GHz [87, 77, 64].

Although several circuits have successfully demonstrated at several tens of GHz circuit frequency, it is hard to say that these demonstrations have sufficiently shown SFQ computing's potential. For example, a state-of-the-art SFQ processor [64] operates at 50 GHz, the performance (i.e., throughput) is relatively low, e.g., 333 million instructions per second (MIPS). The fundamental problem existing behind the SFQ processors is the lack of architectural optimizations to exploit the full potential of SFQ devices. Due to its unique pulse-driven nature, SFQ logic requires completely different architecture designs from conventional CMOS technology. Therefore, the following questions must be clearly addressed to show the SFQ computing's potential: (1) what architecture is promising for this technology, (2) how is the feasibility and effectiveness of the architecture, (3) how to evaluate the effective performance and power efficiency of the target designs.

## **1.3** Thesis statement

To resolve these challenges, this dissertation first proposes the architectural design guidelines for SFQ logic. Next, this dissertation shows the feasibility and effectiveness of the architectural design guidelines with a prototype chip design. Finally, this dissertation designs the neural processing unit (NPU) as a case-study architecture design and evaluates its performance and power efficiency with the cooling cost of 4 kelvin.

## **1.4 Contributions**

This dissertation makes the following contributions:

- This dissertation explores the architectural design space of SFQ processors and quantitively shows that the bit-parallel processing and gate-level deep pipeline structure are suitable for achieving high performance. Moreover, the result indicates that to achieve high performance by such an ultra-deep pipelining, SFQ processors must conceal almost all pipeline stalls. Even with the small pipeline stalls are occurred, the performance improvement degrades 63 times to 5.7 times. To resolve the problem, this dissertation proposes fine-grained multithreading execution for hiding all pipeline stalls caused by data and control hazards, i.e., this scheme enables processor interlock-free streaming execution.

- To clarify our proposed architectural design guidelines' effectiveness and feasibility, this dissertation designs and implements a 4-bit SFQ processor as a prototype and confirm the correct operation by real chip measurement. As a result, the prototype chip has successfully operated at 32 GHz with 6.5 mW. Moreover, to clarify the cooling overhead for keeping SFQ circuits at 4 kelvin, this dissertation evaluates the power efficiency, including a cryocooler cost. Specifically, this dissertation has extended into the 64-bit processor based on these results and evaluated its power efficiency with two types of the real cryocoolers' cost. The best power efficiency (i.e., calculated by its peak performance) with the cooling cost is estimated to at most 7.1 GOPS/W,

and our processor outperforms the CMOS processor model 7.8 times. The result indicates that our SFQ processor based on proposed architectural design guidelines has the potential to achieve high performance and power efficiency even with the cooling cost.

• To show the real potential of SFQ computing, this dissertation proposes and evaluates the SFQ-based neural processing unit (NPU) architecture as a case study. Specifically, first, this dissertation implements and validates an SFQ-based NPU modeling framework. It is the first work to model and validate a model and simulator for SFQ-based architectures. Next, by using the tool, we identify critical challenges in architecting an SFQ-based NPU. Finally, we present *SuperNPU*, our example SFQ-based NPU architecture, which effectively addresses the challenges at the architectural level. Our evaluation shows that the proposed design outperforms a conventional state-of-the-art NPU by 23 times with comparable power efficiency, including extremely expensive cooling costs.

## **1.5** Dissertation Organization

This dissertation is organized into 6 chapters. Chapter 2 introduces the challenges of CMOS processors, prior work that tackles the problem with cryogenic computing, and clarifies our research field. Chapter 3 proposes the architectural design guidelines for SFQ processors with architectural design space exploration and quantitive evaluations. Chapter 4 prototypes the SFQ processor chip based on the proposed guidelines and evaluates its feasibility and effectiveness. Chapter 5 shows the real potential of SFQ computing by designing and evaluating SFQ-based NPU with a validated simulation framework. Chapter 6 concludes this dissertation.

# Chapter 2

# Background

## 2.1 Trend and challenges of CMOS processors

Processors had improved their performance since 1971, when the first processor, Intel 4004, was developed [8]. Fig. 2.1 shows the 48-year CMOS processors' trend [1]. Thanks to Dennard scaling [22] and Moore's Law [65], architects can place more logics and memories on the same sized chip and increase the frequency without increasing its power consumption. However, Dennard scaling broke down in the early 2000s because of the negligible power dissipation (i.e., leakage power), and the device scaling has been ineffective in increasing the chip frequency. As you can see in the Fig. 2.1, processors have been limited in their capacity for clock speed improvement since the early 2000s. With the limit of clock frequency improvement, it is hard to improve the single-thread performance significantly.

After the end of Dennard scaling, architects have introduced multi- or manycore designs to improve chip performance. Specifically, they replace the fast singlecore processor with slow multiple processor cores to improve the multi-thread performance while suppressing its power consumption. To execute a program in parallel, programmers must explicitly describe where to be executed in parallel in their source code. Ideally, the chip performance improves in proportion to the number of cores in a chip. However, programs that cannot be executed in parallel have no benefit from the multi-core designs, i.e., the single-thread performance is still important. Moreover, if the end of Moore's Law comes, we cannot expect

Figure 2.1: 48-year CMOS processors' trend

performance improvement by increasing the number of cores.

While device and manufacturing technologies have continued progressing, it does not seem easy to maintain the transistors shrinking because of physical or economic reasons. Fig. 2.2 shows the processor trends of Intel Xeon processors over generations [71]. The figure plots the number of threads running on a single core (i.e., SMT level), the number of cores integrated on a chip, and the package size of these processors. Increasing the SMT level is completely stopping because it requires much larger intra-core, memory-like architectural units (e.g., register files, load, and store queues, reorder buffer) to keep many architectural states, and it can decrease the number of cores in a chip. On the other hand, the number of cores is still increasing year after year. However, the package size is also increasing in proportion to the number of cores. There is a physical limit to relying on the increase of the package size, and even if the package can be larger, the total number of cores in the computer system will not change much. Thus, architects cannot put more cores on a chip without increasing the package size or reducing each core's size anymore. Therefore, we believe that it is the right time to actively exploit emerging device technologies with significant potentials and make a serious effort to improve their feasibility by resolving their limitations.

Figure 2.2: Trends of Intel Xeon processors over generations

# 2.2 Cryogenic computing

Cryogenic computing, which is to run a computer device at extremely low temperatures (e.g., 77, 4, or sub-millikelvin), is a promising approach for achieving sustainable improvement in the post-Moore's era. Such ultra-low temperatures allow introducing unique physical phenomena (e.g., superconductivity, quantum mechanics) for improving computer systems' performance. There are mainly three types of cryogenic computing: conventional CMOS computing at low temperature, superconducting computing, and quantum computing. These technologies are comparatively classified on two axes (i.e., performance and versatility) in Fig. 2.3.

## 2.2.1 Low-temperature CMOS computing

Cryogenic CMOS computing aims to improve both performance and power efficiency by reducing transistors' leakage current and wire resistance. If the leakage current decrease, we can apply a much higher clock frequency without increasing dynamic power consumption. Moreover, reducing wire resistance makes the wire latency lower, i.e., it becomes much easier to achieve high clock speed or lowlatency signal transfer. Recent studies focusing on cryogenic memory, cache, and

Figure 2.3: Classification of computing technologies

processor show the potential in both performance and power efficiency, including their cooling cost [47, 11, 53].

[47] reports the results of three promising case studies using cryogenic memories to significantly improve the server performance up to 2.5 times, decrease the server power to 6% on average, and reduce datacenter's power cost by 8.4%. [53] proposes cryogenic CMOS cache architecture that achieves 2 times faster cache access and 2 times larger capacity compared to conventional caches running at room temperature. [11] proposes two following types of cryogenic CMOS processor architectures. The high-performance design achieves 41% higher single-thread performance for the same power budget and 2 times higher multi-thread performance for the same die area. The low-power design reduces power consumption by 38% without sacrificing the single-thread performance.

## 2.2.2 Superconducting computing

Superconducting computing uses superconductors' unique properties (e.g., zeroresistance wires and quantization of magnetic flux) for high performance and power efficiency computation. Superconducting circuits use Josephson junctions as basic elements and require cooling to 4 kelvin. There are several superconducting logics such as single-flux-quantum (SFQ) logic family [49, 58], reciprocal quantum logic (RQL) [33], and adiabatic quantum-flux-parametron (AQFP) logic [51].

SFQ logic family is the most practical superconducting VLSI technology and

has ultrafast speed and low-power consumption natures. By focusing on these high potentials, many serious SFQ-related research efforts have been made in various aspects, and a lot of SFQ circuits and their successful operations have been demonstrated [23, 87, 77, 64, 56, 55, 24, 9, 80].

RQL and AQFP logics are relatively slow but more energy-efficient technology compared to SFQ logic. Both use alternating current for power supply instead of direct current, which is employed in SFQ logic. Therefore, they achieve more energy efficiency with sacrificing speed compared to SFQ logic. There are several circuit demonstrations and architecture consideration studies [12].

### 2.2.3 Quantum computing

Quantum computing is entirely different from conventional digital (or classical) computing and uses quantum bits, or qubits, to encode information as logical '0', '1', or both at the same time. This superposition of states enables quantum computers to manipulate enormous combinations of states at once. Therefore, quantum computing has the potential to solve problems that conventional computers could not solve in a realistic amount of time.

Real implementations that use a process called quantum annealing are available in the market as quantum computers [30, 38]. Although they can effectively be applied to specific purposes such as quantum annealing, there is a large gap regarding functionality between classical digital computing and the application-specific quantum acceleration. Therefore, there are several studies about more generalpurpose quantum computing using quantum logic gates, and several companies try to build the first practically useful quantum computer [20, 27, 66].

## 2.3 Superconductor single flux quantum logic

Superconductor SFQ logic [49, 58] and its energy-efficient families [43, 84, 86, 89, 78] are representative ultra-fast and low-power VLSI technologies using superconducting devices, namely Josephson junctions (JJs). This dissertation focuses on the SFQ logic technology because it is one of the most practical technology with emerging device potential for the next-generation computer. In this section, first,

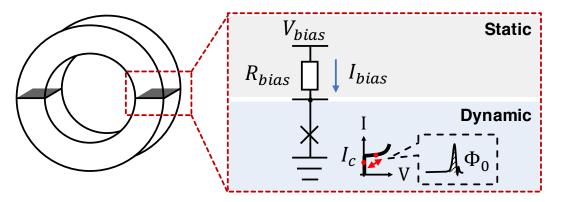

Figure 2.4: (a) Superconductor ring with SFQ (b) Electrical characteristics of JJ (c) Serially connected SFQ rings and (d) its equivalent circuit diagram

the working principle of SFQ circuits is introduced. Next, this dissertation explains the frequency determination and power calculation of SFQ circuits based on pulse-driven logic.

## 2.3.1 Basic elements of SFQ circuit

Fig. 2.4(a) shows a basic circuit element of SFQ technology, a superconductor ring. SFQ circuits utilize the existence of a single magnetic flux quantum (SFQ) in the superconductor ring as an information carrier, similar to the voltage level in conventional CMOS circuits. Specifically, the presence or absence of an SFQ in the ring represents a logical '1' or '0'. The superconductor ring can store and transfer the SFQ by using a superconducting device called Josephson junction (JJ). In this dissertation, we use the superconductor-insulator-superconductor (SIS) structured JJs, as shown in Fig. 2.4(a), that use niobium (Nb) as the superconductor and aluminum oxide (AlOx) as the insulator layer. The JJ included in the ring acts as a switching device like a transistor and JJs' electrical characteristic is shown

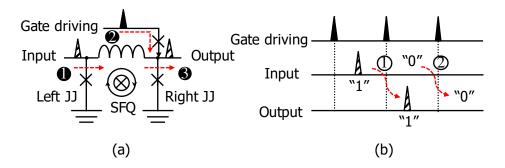

Figure 2.5: (a) Circuit diagram of an SFQ-based DFF with (b) its operating example

in Fig. 2.4(b). If the current flowing JJ exceeds its critical current  $I_c$ , the JJ will switch, and an impulse-shaped voltage pulse, called an SFQ pulse, will be generated. SFQ pulses have a quantized area  $\Phi_0$  due to magnetic flux quantization, a fundamental property of superconductors, as shown in Eq. (2.1).

$$\int V(t)dt = \Phi_0 \simeq 2.07 \times 10^{-15} \text{Wb} = 2.07 \text{mV} \cdot \text{pH}$$

(2.1)

As shown in Fig. 2.4(b), the typical width and height of the SFQ pulse are a few picoseconds and a few hundreds of microvolts, respectively. The SFQ pulse allows the ultra-fast  $(10^{-12}s)$  and low-energy switching  $(10^{-19}J)$ .

Fig. 2.4(c) shows the serially connected SFQ rings and Fig. 2.4(d) shows its equivalent circuit diagram. Inductance and cross marks represent the superconductor part of the ring and JJs, respectively. These serially connected SFQ rings are used to one of the SFQ wirings named Josephson transmission line (JTL). The signal is propagated by switching the ring in order from the left in JTL. Besides, SFQ signals can be split or merged using a few JJs, and easily stored in large inductance superconducting rings, i.e., the ring can play the role of delay flip flops (DFF). All SFQ gates or wire cells are composed of a combination of the SFQ rings, and the working principle of the SFQ gates are explained in Section 2.3.2.

## 2.3.2 Working principle of SFQ circuit

Unlike voltage level logic, synchronization of an input signal with the reference signal (from now on *gate driving pulse*) is essential at a storage ring in each SFQ logic gate to distinguish between that the input signal has not arrived yet and

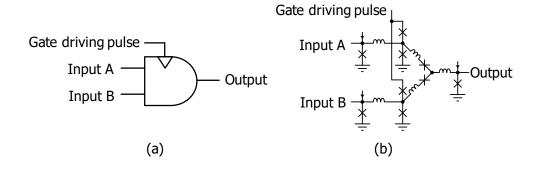

Figure 2.6: (a) SFQ-based AND gate with (b) its circuit diagram

that a logic value '0' has arrived. In other words, each storage ring intrinsically has latch or memory functionality, and all the SFQ logic gates are clocked gates except for wire cells such as pulse splitters and mergers.

First, an SFQ-based DFF is taken as our example due to its simplest structure consisting of only a single superconductor ring and a gate driving pulse line. When the input pulse comes to the ring, it makes the current flowing through the left JJ of the ring higher than its critical current,  $I_c$ . With the electrical characteristic shown in Fig. 2.4(b), the left JJ generates a voltage pulse and it is stored to the ring as an SFQ (Fig. 2.5(a) **0**). Next, by taking a gate driving pulse (Fig. 2.5(a) **0**), the right JJ is activated and the stored SFQ is transferred to the output as a voltage pulse (Fig. 2.5(a) **6**). In this manner, SFQ gates can define the logical value '1' as the existence of stored SFQ between the gate driving pulses (Fig. 2.5(b) **0**). On the other hand, if no input pulse comes during a gate driving pulse period, no voltage pulse is generated on the output, and it indicates the logical value '0' (Fig. 2.5(b) **2**).

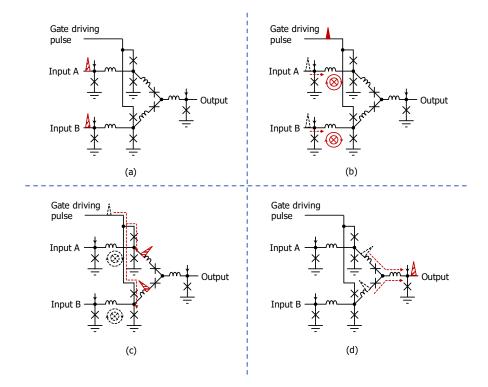

Next, we introduce how to build SFQ-based AND gate with its operating examples. Fig. 2.6 shows the SFQ-based AND gate and its circuit diagram. As mentioned in Section 2.3.1, SFQ logic gates are composed of a combination of the SFQ rings, and AND gate is mainly composed of three SFQ rings. Fig. 2.7 shows the operating examples of SFQ AND gate. When the input pulses come to the AND gate (Fig. 2.7(a)), these signals are stored as SFQ in the AND gate's SFQ rings (Fig. 2.7(b)). Next, by taking a gate driving pulse, the JJs of the SFQ rings storing inputs are activated, and the stored SFQ are transferred to the output

Figure 2.7: Operating examples of SFQ AND gate

as voltage pulses (Fig. 2.7(c)). The two data pulses switch the JJ at the output port, and the logical AND operation is performed. The JJ at the output port only switches when both two SFQ rings output data pulses.

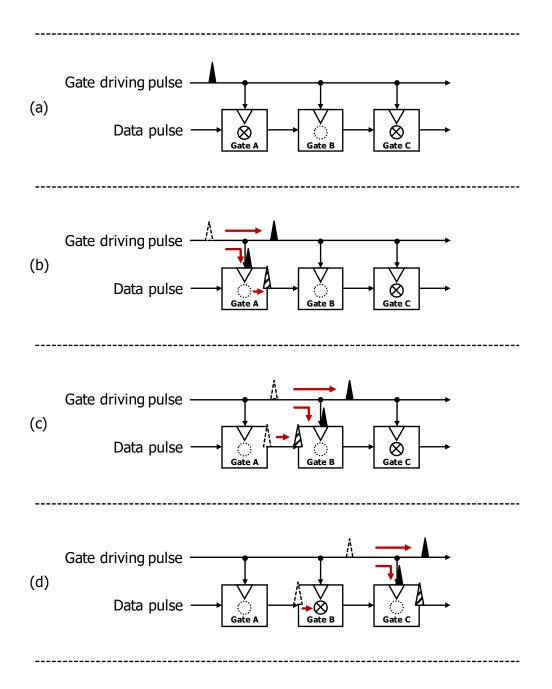

Besides, we explain how to operate SFQ logic gates with serially connected DFFs, as shown in Fig. 2.8. In this circuit, gate A and gate C have an SFQ inside their ring initially; on the other hand, gate B has no data (Fig. 2.8 (a)). First, a gate driving pulse arrives at gate A and an SFQ stored in gate A outputs as a data pulse (Fig. 2.8 (b)). Second, the gate driving pulse arrives at gate B (Fig. 2.8 (c)). However, there is no output from gate B because gate B does not have an SFQ in its ring. To guarantee the correct operation, gate B must get the gate driving pulse before the data pulse input. In the timing design of SFQ circuits, designers must adjust the arrival timing of the data pulse and gate driving pulse. For example, inserting the delay elements in the data path can satisfy such timing constraints. Finally, gate C gets the gate driving pulse and outputs the data pulse (Fig. 2.8 (d)). In this way, the SFQ circuits consisting of memory functional logic gates operate with gate driving signals.

Figure 2.8: Operating example of the serially connected DFFs

Figure 2.9: Example timing chart of an SFQ DFF gate

### 2.3.3 Frequency determination

Unlike conventional CMOS technology, SFQ circuits' frequency is determined by the timing difference between the data and gate driving pulse (GDP) arrival and timing constraints of origin and destination gates. In the CMOS technology, the clock frequency is bounded by the longest datapath delay because it only can put single digital information (i.e., voltage level) in a wire. On the other hand, SFQ logic can put several data into a single wire because its data is encoded as a voltage pulse. That pulse encoding enables SFQ circuits to flow many data pulses through a single wire simultaneously. Therefore, the critical factor in determining SFQ circuits' frequency is the difference between the arrival timing of data and gate driving pulse, not the wire length.

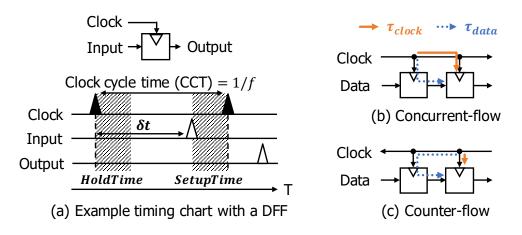

As mentioned in Section 2.3.1, SFQ logic gates have inherently memory or latching functionality. In other words, each SFQ logic gate has its own two types of timing constraints, *HoldTime* and *SetupTime*. Data from the origin gate should arrive at the destination gate after the HoldTime of the destination gate, and the next GDP should arrive after SetupTime elapsed from the data arrival. If the input pulse violates the HoldTime or SetupTime, the pulse will not be recognized as an input of logical '1'. Fig. 2.9 shows the example timing chart of an SFQ DFF gate. The circuit frequency is calculated by following Eq. (5.1).

$$f = 1/\text{GDP}$$

cycle time  $= 1/(SetupTime + Max(HoldTime, \delta t))$  (2.2)

$\delta t$  represents the timing difference between the data and GDP arrival and it de-

#### Chapter 2 Background

pends on the circuit structure.

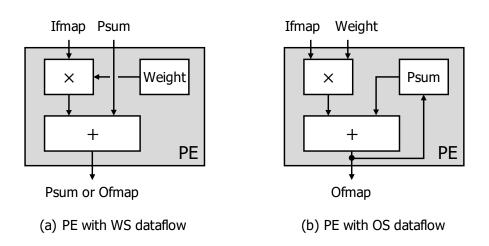

One of the most influential factors on the  $\delta t$  is how to provide GDP (from now on called the clocking scheme). SFQ circuits employ flow clocking schemes where the GDP signals also propagate inside the circuits, i.e., not all but part of SFQ logic gates are synchronized [49]. Thus, the clocking scheme is an essential factor to determine the GDP frequency of SFQ circuits. There are mainly two clocking schemes in SFQ logic designs; the concurrent-flow (Fig. 2.10(a)) and the counterflow clocking (Fig. 2.10(b)). In the concurrent-flow clocking, the GDP and data pulses propagate in the same direction. On the other hand, the GDP and data pulses propagate in the opposite direction in the counter-flow clocking.

To clarify the difference between the two clocking schemes, we calculate  $\delta t$  of each clocking scheme. As shown in Fig. 2.9,  $\delta t$  is calculated by Eq. (2.3)

$$\delta t = T_{data} - T_{GDP} \tag{2.3}$$

, where  $T_{data}$  and  $T_{GDP}$  are the arrival timing of data pulse and GDP, respectively. Both  $\delta t$  of concurrent-flow clocking and counter-flow clocking are summarized in Fig. 2.10(c). In the concurrent-flow clocking (Fig. 2.10(a)), the  $T_{data}$  of gate B is calculated to  $\tau_{c2} + \tau_d$ . On the other hand,  $T_{GDP}$  of gate B is represented in  $\tau_{c1} + \tau_{c2}$ . Thus, the  $\delta t$  of gate B is  $\tau_d - \tau_{c2}$ , and  $\delta t$  can be minimized by maching the data pulse and GDP propagation delay. In other words, the concurrent-flow clocking can achieve higher circuit frequency because it can hide the data propagation delay by flowing the GDP and the data pulse. However, such clocking cannot be utilized when the circuit includes the feedback loop, where the GDP and data pulses propagate in the opposite direction. Because gate A should wait for the output of gate D in Fig. 2.10(a),  $T_{data}$  of gate A is calculated to  $3\tau_{c1} + \tau_{c2} + 3\tau_d$ . On the other hand,  $T_{GDP}$  is represented in  $\tau_{c2}$ . As a result,  $\delta t$  of gate A is  $3\tau_{c1} + 3\tau_d$  and it increases in propotion to the depth of feedback loop. The circuit's frequency can be significantly reduced because the next GDP should wait for a very long data transfer through the feedback path.

On the other hand, this problem can be resolved with the counter-flow clocking, which can entirely hide the data feedback delay. Specifically,  $\delta t$  of gate A is represented in  $3\tau_d - 3\tau_c$  and the long data transfer through the feedback path can be hidden. However, the counter-flow circuit's frequency is much lower than that

| (b) | Counter flow |

|-----|--------------|

|-----|--------------|

|                 | $\Delta \tau$ w/o FB | $\Delta \tau$ w/ FB |

|-----------------|----------------------|---------------------|

| Concurrent flow | $\tau_d - \tau_c$    | $3\tau_d + 3\tau_c$ |

| Counter flow    | $\tau_d + \tau_c$    | $3\tau_d - 3\tau_c$ |

| (C) | Comparison of $\Delta \tau$ |

|-----|-----------------------------|

|-----|-----------------------------|

Figure 2.10: Illustration of flow clocking schemes (a) Concurrent-flow clocking (b) Counter-flow clocking (c) Comparison of  $\delta t$

Figure 2.11: Circuit diagram of a biased JJ

of the concurrent-flow circuit without feedback. This is because the GDP and data pulses propagate in the opposite direction in the feedforward path (i.e.,  $\delta t$  is  $\tau_d - \tau_{c1}$ ). Therefore, the existence of a feedback loop is the key factor to determine the clocking scheme.

#### 2.3.4 Power consumption

The power consumption of the SFQ circuit consists of the static power consumed by the bias current supply and the dynamic power consumed when the JJs are activated. Fig. 2.11 shows a circuit diagram of a JJ biased by direct current. The total power consumption of the SFQ circuit  $P_{total}$  is given by Eq. (2.4).

$$P_{total} = P_{static} + P_{dynamic} \tag{2.4}$$

where  $P_{static}$  and  $P_{dynamic}$  is the static and dynamic power consumption, respectively. As shown in Fig. 2.11, the bias current is continuously supplied to the JJ in the SFQ circuit, and it consumes the power regardless of JJ's switching. The static power  $P_{static}$  is calculated by Eq. (2.5).

$$P_{static} = V_{bias} I_{bias} \times N_{JJ} \tag{2.5}$$

where  $V_{bias}$  and  $I_{bias}$  is the bias voltage and bias current, respectively.  $N_{JJ}$  is the number of JJs included in the target circuit.

The dynamic power consumption in SFQ circuits is caused only during JJ's switching event; otherwise, the JJs are in the zero-voltage state (Fig. 2.4(b)), and

#### Chapter 2 Background

no energy is consumed. When the JJ switches, the current flowing JJ exceeds its critical current  $I_c$  and generates SFQ pulse, that area corresponds to  $\Phi_0$ . Thus, the dynamic energy for one JJ's switching event is calculated by Eq. (2.6).

$$E_{dynamic} = I_c \Phi_0 \tag{2.6}$$

Besides, the dynamic power is given by Eq. (2.7).

$$P_{dynamic} = E_{dynamic} \times N_{activeJJ/s} \tag{2.7}$$

where  $N_{activeJJ/s}$  is the number of activated JJs per second in the target circuit.

# 2.4 Current status and research trend of SFQ technology

Due to the SFQ logic's high potentials, many serious SFQ-related research efforts have been made in various aspects to promote the technology. This dissertation introduces the current research in fabrication process technology, energy-efficient SFQ logic technology, circuit demonstrations, and SFQ memory technology in the following subsections.

#### 2.4.1 Fabrication process technology

In conventional CMOS technology, "technology node" or "feature size" represent the minimum line width or the smallest machining dimension of CMOS transistors. On the other hand, SFQ logic technology's feature size represents the side length of Josephson junctions. The National Institute of Advanced Industrial Science and Technology (AIST) in Japan provides the AIST 1.0  $\mu$ m Niobium (Nb) process technology for chip fabrication [57]. There are several fabricated chips for SFQ circuit demonstration by using this fabrication process technology. For instance, the state of the art bit-serial 8-bit processor, CORE e2, which successfully operates at 50 GHz, consists of 10,604 JJs [64]. In the 8-bit multiplier design, 20,251 JJs are integrated on a 6.03 mm × 5,22 mm chip area [55]. With this technology, the chip can integrate a few tens of thousands of JJs. It is possible to design prototypes of element circuits such as adders, multipliers, and processors to demonstrate the concept of architecture.

However, it is hard to design fully functional or practical units due to the low JJs' integration density. The AIST fabrication technology is relatively large compared to CMOS technology because the AIST uses an i-line stepper with a wavelength of 365 nm introduced to the market in the mid-1990s. The state-ofthe-art steppers using KrF or ArF excimer lasers would allow the fabrication of ultrafine Josephson junctions and patterns. To the best of our knowledge, there is no study that mentions the physical limit of JJ scaling. On the other hand, there is the scaling rule that the frequency increases in proportion to the reduction rate of JJ until 200<sup>-300</sup> nm [40], and T flip-flop (TFF) has successfully demonstrated at up to 770 GHz with the technology [15]. Moreover, there are several schemes to reduce the SFQ cell size without the JJ scaling, such as the introduction of a shuntresistor-free junctions [41], vertically-stacked junctions [13], multi-layer process technology with high-inductance layers [82], and new materials, such as niobium nitride. It is expected that process manufacturing technology will advance, and the device performance will improve in the future.

## 2.4.2 Energy-efficient SFQ logic technology

To ensure a more advantage in energy efficiency towards CMOS technology even with the cooling cost for 4 kelvin, researchers have so far contributed to developing energy-efficient circuit technologies. SFQ circuits were biased using direct current sources supplied by the external voltage sources with on-chip bias resistors. The total power of SFQ circuits is dominated by Joule heating in bias resistors (i.e., static power) rather than the JJ switching (i.e., dynamic power). Therefore, several studies are focusing on reducing SFQ circuit static power.

Inductance-load biasing [86], called LR biasing, replaces a bias resistor into a large inductor with a small resistor to reduce the static power. On the other hand, energy-efficient rapid SFQ (ERSFQ) logic technology [43, 84, 86, 89, 78] has successfully eliminated the static power. The only difference from standard SFQ gates is replacing bias resistors with the limiting JJs and series inductances. No major redesign of the SFQ logic gates is required in both technologies.

#### 2.4.3 Circuit demonstrations

FLUX-1, the first single-chip SFQ processor, has been designed and fabricated in 2001s [23]. FLUX-1 chip represents an 8-bit bit-parallel processor prototype with a target GDP frequency of 17-20 GHz. This chip contains 65,759 JJs on a 10.6 mm  $\times$  13.2 mm die with flip-chip packaging. Unfortunately, the operation verification of the chip has failed.

Core 1  $\alpha$ , the first successfully operated SFQ processor, has been designed and fabricated in 2004s [79]. This processor has employed 8-bit bit-serial processing for successful demonstration and operated at 15 GHz with a power consumption of 1.6 mW. This chip consists of 4,999 JJs. Other bit-serial processors have been designed and successfully demonstrated its correct operation [77, 87, 64]. State of the art bit-serial processor, CORE e2, operates at 50 GHz [64]. This processor includes 10,604 JJs and consumes 2.52 mW.

As described above, the bit-serial operation leads to a lot of successful circuit demonstrations. This is because bit-serial processing reduces hardware and longdistance wiring, and the timing adjustment of SFQ pulses becomes easy. However, such bit- by-bit fine-grained operations make the execution time much longer, resulting in poor performance. Therefore, it is a straightforward next step to consider the architecture exploiting the full potential of SFQ devices.

### 2.4.4 Memory technology

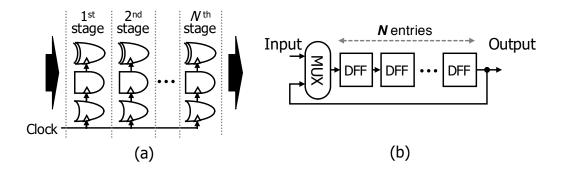

**On-chip memory technology**: For the SFQ logic's on-chip memory, the shift-register-based memory is much more practical than the random access memory (RAM). Even though we can implement RAM with SFQ technology, it severely suffers from low driving capability and scalability. Such limitations mainly result from the difficulty of driving the word lines and bit lines with the small pulses [49, 88]. On the other hand, a shift-register-based memory does not have those problems because it just consists of the serially connected DFFs and the feedback loop. However, it is difficult for the shift-register-based memory to support the random memory access due to the complex control logic and the variable access latency [37]. Therefore, the SFQ technology favors applications with sequential memory access when its on-chip memory implementation is considered.

**Off-chip memory technology**: It has been a long-standing challenge to implement a large-scale and high-speed off-chip memory operating at the 4K environment. There has been a few research about JJ-based memories [73, 45, 76], and one of them is Vortex Transition Memory (VTM) [73]. The VTM is the largest Josephson memory whose 4-kbit prototype has been demonstrated. Despite the demonstration, it has been difficult to practically use the VTM mainly due to the scaling and speed problems with the AC-biasing and the large superconductorring-based memory cells. Even though several off-chip memory technologies (e.g., hybrid Josephson-CMOS memory [45, 76], Josephson magnetic memory [21]) are currently being developed, these technologies also have not been put to practical use yet. For these reasons, it is currently practical to use CMOS memory technology, which is slower than the 4-kelvin JJ-based memory but large and reliable. Therefore, SFQ technology favors computation-oriented applications with a minimal number of off-chip memory access.

# Chapter 3

# Exploring design space of a SFQ processor

## 3.1 Introduction

As mentioned in Chapter 2, researchers have so far greatly been contributed to developing SFQ devices and logic design technologies; their physical designs and the successful operations of SFQ microprocessors have been demonstrated [87, 77, 64]. A state-of-the-art SFQ processor [64] have successfully operated at 50 GHz of GDP frequency. However, its effective performance, i.e., throughput, is significantly low compared to its circuit frequency, e.g., 333 million instructions per second (MIPS).

The fundamental problem existing behind the SFQ processors is the lack of architectural optimizations to exploit the full potential of SFQ devices. Specifically, these processors employ bit-serial processing to reduce hardware and long-distance wiring, and the timing adjustment of SFQ pulses becomes easy. However, such bit- by-bit fine-grained operations make the execution time much longer, resulting in poor performance. Moreover, the pipeline structure of these SFQ processors is from a course-grained pipeline such as the traditional 5-stage pipeline that consists of fetch, decode, execution, memory access, and writeback stages, despite the difference of device characteristics. It is essential to revisit SFQ processor architecture that fully exploits its device potential towards realizing extremely high-performance SFQ processors.

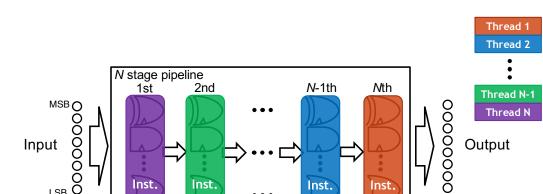

To solve the problem, we clarify the conventional SFQ processors' problems and quantitively shows the design guidelines for high-performance SFQ processors by conducting architectural design space exploration. As a result, we show the bit-parallel processing with gate-level pipelining is suitable for high-performance SFQ processors. Moreover, we propose fine-grained multithreading execution as the pipeline stall concealment technologies not to degrade its performance.

# 3.2 Architectural design space of SFQ processors

#### **3.2.1** Architecture paramaters

In this section, this dissertation introduces two key architecture parameters for determining SFQ processors' performance.

- **Pipeline depth**: Pipeline depth represents the number of pipeline stages. Whichever CMOS and SFQ circuits, it is essential in determining a processor's performance. First, a general five-stage pipeline structure is set as a standard. Those with a deeper pipeline are called super pipeline structures, improving the clock frequency by reducing one pipeline stage's delay. Ultimately, the most fine-grained pipeline structure, that a deeper pipeline to the gate level is also conceivable. Although the clock frequency can be improved by increasing the pipeline depth, there are drawbacks such as 1) area overhead of the pipeline registers and 2) increased power consumption due to the increased clock frequency. However, the SFQ logic gate has no such drawbacks. Since all SFQ logic gates have a latch function, it is unnecessary to add pipeline registers to deepen the pipeline. Moreover, the SFQ gates can operate with less than 1 / 1,000 power consumption than the case of CMOS gates [54]. By utilizing these fundamental features, it is possible to solve the above two problems. Therefore, in SFQ design, it is expected that the performance will be greatly improved by increasing the pipeline depth.

- **Datapath bit width**: The datapath bit width is also one of the architecture parameters and represents the bit width handled by each unit, such as an

ALU or register file in one process. The data word length is the data that can be handled by the processor. *Slice* corresponds to the data whose data word length is divided. For example, each 8-bit data obtained by dividing 64 bits into eight is called a slice. In this case, the number of slices is 8. Based on the above, the design space is defined in the same way as the pipeline depth. There are mainly three types of processing schemes, bit-serial, bit-slice, and bit-parallel processing. In the bit-serial and slice processing schemes, divided data are pipelines in the units (e.g., ALU or register file) at a bit or slice level. On the other hand, data can be overlapped at the word level in bit-parallel processing.

### 3.2.2 Performance model

In this section, to consider processor architecture suitable for SFQ circuits, we use a performance model to clarify each architecture parameter's effect on the SFQ processor performance. In this architectural design space exploration, the time per instruction (TPI) is used [31]. TPI is calculated by Eq. (3.1).

$$TPI = \frac{T}{N_I} = \left(\frac{t_o}{\alpha} + \gamma \frac{N_H}{N_I} t_p\right) + \frac{t_p}{\alpha p} + \gamma \frac{N_H}{N_I} t_o p \tag{3.1}$$

Each parameter is shown as follows.

- T: Total execution time.

- $N_I$ : The number of total instructions.

- $N_H$ : The number of total pipeline hazards.

- $t_o$ : The delay for latching data at pipeline registers. It depends on the HoldTime and SetupTime.

- $t_p$ : The total gate delay of the longest path in the pipeline.

- p: The number of pipeline stages.

- α: The number of simultaneous issued instructions per cycle. If the α is 2,

2 instructions are issued at one clock cycle.

|                            | $t_o$ (ps) | $t_p \ (\mathrm{ps})$ |

|----------------------------|------------|-----------------------|

| $1.0\mu m SFQ-BP$          |            | 2517.76               |

| $1.0\mu\mathrm{m}$ SFQ-BSE | 13.32      | 13232.8               |

| $1.0\mu\mathrm{m}$ SFQ-BSL |            | 4565.4                |

| $0.3\mu m SFQ-BP$          |            | 755.328               |

| $0.3 \mu m$ SFQ-BSE        | 3.995      | 3969.84               |

| $0.3 \mu m$ SFQ-BSL        |            | 1369.62               |

| CMOS-BP                    | 86.76      | 4048.58               |

|                            |            |                       |

Table 3.1: Delay parameters

•  $\gamma$ : The ratio of the average pipeline stall time per the latency for instruction execution, i.e.,  $t_o p + t_p$ . The maximum value is 1, which corresponds to the situation where subsequent instructions cannot be started until the instruction existing in the first pipeline stage is committed. On the other hand, the minimum value is 0, which indicates the situation where none pipeline stalls occur. For simplicity, this model uses the average value as  $\gamma$ . Note that the pipeline stalls caused by various hazards vary depending on the microarchitecture and the hazard occurrence situation. In this model, it is expressed as an average value.

The first item of Eq. (3.1) in parentheses represents the execution time increase caused by stalls and  $t_o$ , which is independent of the number of pipeline stages. The second item shows the effect of pipeline depth and  $\alpha$  on the latency for processing one instruction. The third item indicates the pipeline stall overheads.

### 3.2.3 Delay parameters setup

In this experiment, SFQ processors are assumed as scalar processors (i.e.,  $\alpha = 1$ ), and we evaluate SFQ-based bit-serial (SFQ-BSE), bit-slice (SFQ-BSL), and bitparallel processors (SFQ-BP). We also prepare the CMOS-based bit-parallel processor (CMOS-BP) as a comparison. Here, CMOS-BP refers to the configuration of a commercial processor that adopts the out-of-order instruction issuance scheme. The delay parameters are summarized in Table 3.1. We use two delay parameters for the SFQ processor: the 1.0  $\mu$ m Nb process currently used in SFQ circuits' demonstrations [57], and the 0.3  $\mu$ m Nb process [40], where the scaling rule that holds for SFQ devices reaches its limit. We estimate the delay parameter of the 0.3  $\mu$ m Nb process based on the scaling rule; when the JJ scales to 1/a, the switching speed and delay are also 1/a [40].  $t_o$  is calculated by the sum of the arithmetic average of SetupTime and HoldTime of typical logic gates used in SFQ processors and the operating margin for countermeasures against manufacturing variations and jitter.  $t_p$  is determined based on the CORE 1 $\beta$  [77, 87], that is one of state of the art SFQ processors. Specifically,  $t_p$  is determined by multiplying the circuit delay of the SFQ adder that constitutes the EX stage, which is the critical path of CORE 1 $\beta$ , by 7, which is the number of pipeline stages of CORE 1 $\beta$ . The circuit delay of this SFQ adder can be obtained by multiplying the GDP period by the number of cycles required for processing by the SFQ adder, as shown in Eq. (3.2).

$$D_{SFQadder} = T_{GDP} \times (N_{stages} + N_{slices} - 1)$$

(3.2)

Where  $D_{SFQadder}$  is the circuit delay of this SFQ adder,  $T_{GDP}$  is the GDP cycle time for driving SFQ adder's gates,  $N_{stages}$  is the number of pipeline stages of SFQ adder, and  $N_{slices}$  is the number of slices. For example,  $N_{slices}$  is 1 in SFQ-BP; on the other hand,  $N_{slices}$  is the data bit width in SFQ-BSE because the data is processed bit by bit. We use the value of the SFQ cell library of the 1.0  $\mu$ m Nb process as the circuit delay parameters. In addition, all circuit delays are assumed to be obtained from 64-bit SFQ adders. Below, we explain how to obtain  $t_p$  for each of SFQ-BP, SFQ-BSE, and BSL.

In SFQ-BP, since there is no feedback loop in the SFQ adder, the GDP period  $T_{GDP}$  is  $t_o$ , which is the maximum value that can be supplied.

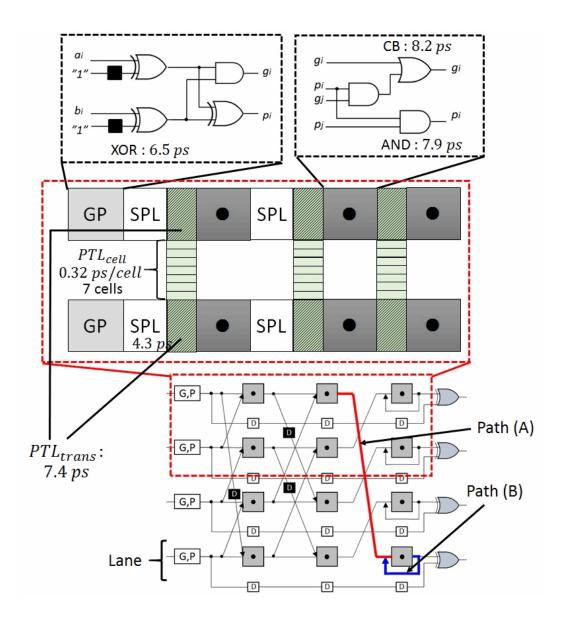

In SFQ-BSE and SFQ-BSL, there is a feedback loop path in the SFQ adder, and it is necessary to wait for the input data in this loop, i.e., SFQ-BSE and SFQ-BSL cannot apply the clock skewing and the  $T_{GDP}$  is determined by the critical path delay of the SFQ adder. Fig. 3.1 shows the gate-level circuit diagram of the SFQ adder. There are two candidates for the critical path, path (A) and path (B). In this adder, path (A) is longer than path (B), and the logic gate elements contained in path (A) are the AND gate, the confluence buffers (CB), and the

Figure 3.1: Gate-level circuit diagram of the SFQ adder.

superconducting passive transmission line (PTL), and splitters (SPL). The signal transmission time in PTL is determined by the delay required for transmission and reception to the transmission line ( $D_{PTLtrans}$ ) and the transmission line's length. The delay of path (A) is calculated by Eq. (3.3).

$$D_{pathA} = D_{AND} + D_{CB} + D_{PTLtrans} + D_{SPL} + (DPW - 1) \times D_{PTLcell} \times N_{PTLcell}$$

(3.3)

Where  $D_{pathA}$  is the delay of path (A),  $D_{AND}$ ,  $D_{CB}$ ,  $D_{SPL}$ , and  $D_{PTLcell}$  is the delay of AND gate, the confluence buffer, the splitter, and the PTL cell, respectively. DPW is the data path bit width and  $N_{PTLcell}$  is the number of PTL cells that exist between two bit lines as shown in Fig. 3.1. SFQ-BSL uses the 8-bit slice, which was the best-performing slice width for 64-bit data word lengths. The  $t_p$  of bit-serial and slice processing in Table 3.1 are not just 64 times or 8 times that of the bit-parallel scheme, respectively. This is because the slice- and bit-level overlap execution reduces the processing delay. In the CMOS processor, referring to the configuration of Intel's 45 nm process Core i7 920, 14 stages of pipeline and clock frequency of 2.66 GHz are used for each parameter calculation [3].  $t_o$  and  $t_p$  are calculated by the clock cycle time with the best ratio between the latch overhead and the delay of the pipeline stage (i.e., 1.8 to 6 [31]), as shown in Eq. (3.4), Eq. (3.5), respectively.

$$t_o = 1/2.66(\text{GHz}) \times 1.8/(1.8+6)$$

(3.4)

$$t_p = 1/2.66(\text{GHz}) \times p - t_o \times p \tag{3.5}$$

# 3.3 Design space exploration

This section evaluates each architecture parameter mentioned in Section 3.2.1 to determine the design guidelines for high-performance SFQ processors.

#### 3.3.1 Datapath bit width evaluation

First, to show the effect of the datapath bit width on the processor performance, we evaluate the performance with the fixed number of pipeline stages. In this

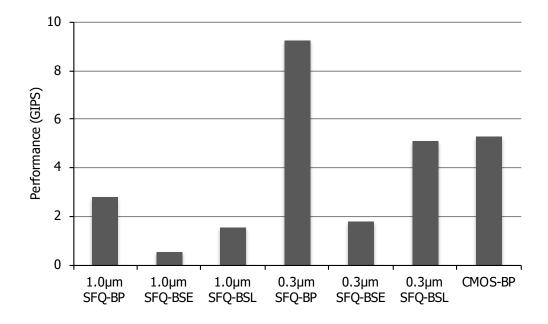

Figure 3.2: Performance comparison with fixed pipelines

evaluation, we set  $\gamma = 0$  of the TPI shown in Eq. (3.1) to compare each processor model's peak performance. We use the number of instructions executed per second (IPS) as the performance metric. IPS is calculated by Eq. (4.2).

$$IPS = 1/TPI \tag{3.6}$$

Fig. 3.2 shows the IPS comparison when the number of pipeline stages is fixed (SFQ and CMOS processors consist 7 and 14 stages, respectively). As the comparison results, the performance of SFQ-BP, SFQ-BSE, and SFQ-BSL with 1.0  $\mu$ m Nb process are 2.78 Giga IPS (GIPS), 0.52 GIPS, and 1.53 GIPS, respectively. In the 0.3  $\mu$ m Nb process, these clock frequencies are 9.27 GIPS, 1.76 GIPS, 5.11 GIPS, respectively. In the bit-serial and bit-slice processing schemes, logic gates in the pipeline stage are activated multiple times during the processing of one-word data, resulting in increasing  $t_p$ . The increase of  $t_p$  has a significant adverse effect on the IPS. The results clearly show that the bit-level parallelism of the bit-parallel processing scheme is more effective in improving the IPS than the latency reduction by the bit-level and slice-level overlapping execution.

In the 1.0  $\mu$ m Nb process SFQ processors, the IPS of SFQ-BP, SFQ-BSE, and SFQ-BSL are about the same as or lower than that of CMOS-BP. In the

Figure 3.3: Performance comparison with variable pipeline stages

$0.3 \ \mu m$  Nb process, the IPS of SFQ-BSE and SFQ-BSL are also about the same as or lower than that of CMOS-BP. On the other hand, SFQ-BSL and SFQ-BP achieve 5.11 GIPS and 9.27 GIPS, which are higher than CMOS-BP performance, respectively. This result also indicates that the bit-parallel processing scheme is the most suitable and sufficient for achieving high-performance SFQ processors.

#### 3.3.2 Pipeline depth evaluation

Next, we evaluate the peak performance ( $\gamma = 0$ ) with variable pipeline stages to show the effect of the pipeline depth. Fig. 3.3 shows the performance comparison between SFQ-BP, SFQ-BSE, SFQ-BSL with a 0.3  $\mu$ m Nb process, and CMOS-BP. The y-axis represents the performance, i.e., IPS, and the x-axis represents the number of pipeline stages. According to Fig. 3.3, the SFQ processors have more capacity to improve their performance than CMOS processors by increasing the number of pipeline stages. This is because the  $t_o$  of the SFQ circuit is much smaller than that of the CMOS circuit, as shown in Table 3.1. Therefore, SFQ processors can achieve higher clock frequency, i.e., higher performance. Moreover, in the CMOS processors, it is tough to improve the clock frequency by deepening

Figure 3.4: Performance comparison between SFQ-BP and CMOS-BP considering the ratio of the average pipeline stall  $\gamma$

the pipeline due to their power consumption, i.e., the power-wall problem. In contrast, in the SFQ circuits, the power consumption problem does not occur due to their low-power nature.

The broken lines in Fig. 3.3 are the limit of peak performance calculated with the limit of clock frequency based on the real chip design data of SFQ-BP, SFQ-BSE, SFQ-BSL, which are 166.67 GIPS, 76.66 GIPS, and 119.90 GIPS, respectively. When the number of SFQ-BP's pipeline stages increases, the performance of SFQ-BP reaches 166.67 GIPS at 377 pipeline stages, which is higher than that of SFQ-BSE and SFQ-BSL with the same number of pipeline stages. On the other hand, CMOS-BP with an increased number of pipeline stages cannot outperform around 11 GIPS. To obtain higher performance in SFQ processors, SFQ processors should adopt a bit-parallel processing scheme and a deep pipeline structure. However, the effect of pipeline stall increases in proportion to the number of pipeline stages, increasing TPI, as shown in Eq. (3.1).

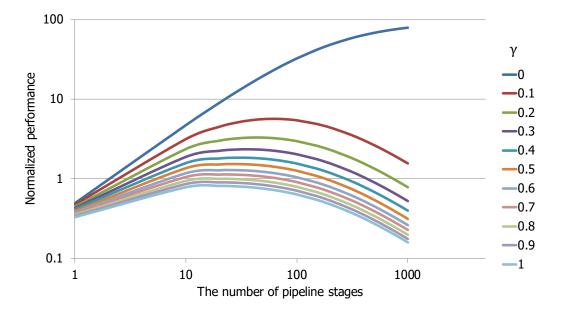

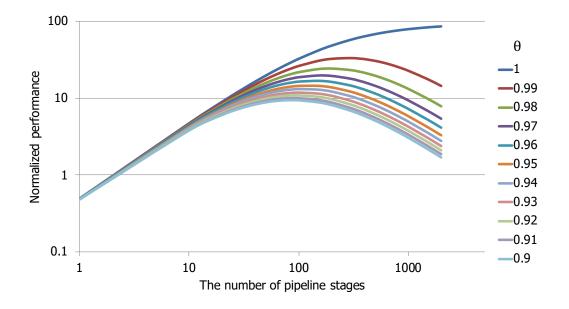

Next, let us consider the performance when pipeline stalls occur. Fig. 3.4 shows the performance comparison between SFQ-BP with 0.3  $\mu$ m Nb process and CMOS-BP in case of  $\frac{N_H}{N_I} = 0.5$  considering the ratio of the average pipeline stall,  $\gamma$ .

Figure 3.5: Performance comparison between SFQ-BP and CMOS-BP considering the pipeline stall concealment rate  $\theta$

The performance is obtained by normalizing the IPS with the peak performance of CMOS-BP. When  $\gamma = 0$ , that is, there is no pipeline stall, SFQ-BP achieves 62.66 times the performance of the CMOM-BP. However, the performance ratio between degrades up to 5.67 in 60 pipeline stages when the pipeline stalls are considered ( $\gamma = 0.1$ ). In other words, if the pipeline stalls cannot be sufficiently concealed, the performance will be low even with the deep pipeline structure. Thus, we introduce  $\theta$ , the pipeline stall concealment rate, to Eq. (3.1).  $\theta$  can take a value from 0 to 1, and  $\theta = 1$  indicates that all stalls are concealed. TPI with  $\theta$  is calculated as shown in Eq. (3.7).

$$TPI = \frac{T}{N_I} = \left(\frac{t_o}{\alpha} + (\gamma \times (1-\theta))\frac{N_H}{N_I}t_p\right) + \frac{t_p}{\alpha p} + (\gamma \times (1-\theta))\frac{N_H}{N_I}t_o p$$

(3.7)

Fig. 3.5 shows the performance comparison result in  $\frac{N_H}{N_I} = 0.5$  and  $\gamma = 0.5$ . The y-axis represents the normalized performance, and the x-axis represents the number of pipeline stages. Fig. 3.5 shows the result of increasing the value of  $\theta$  by 0.01 from 0.9 to 1, that is, increasing the pipeline stall concealment rate by 1% from 90% to 100%. In case that 99% of pipeline stalls are concealed, SFQ-BP

Inst.

Inst.

Chapter 3 Exploring design space of a SFQ processor

Inst.

/i\_

Inst.

Input

LSB

Cloc

with 300 pipeline stages outperforms 32.98 times than CMOS-BP. As a result, by hiding 99% of the pipeline stalls, SFQ processors' performance has a capacity for improvement in an extremely deep pipeline structure, such as 300 pipeline stages. Besides, advanced pipeline stall concealment technology is essential for high-performance SFQ processors.

Figure 3.6: Overview of the proposed design policy

## **3.4** Design guidelines for high-performance SFQ processors