#### 九州大学学術情報リポジトリ Kyushu University Institutional Repository

## System Level Optimization Techniques for Low Power VLSI Design

石原, 亨 九州大学システム情報情報工学

https://doi.org/10.11501/3166839

出版情報:九州大学, 1999, 博士(工学), 課程博士

バージョン: 権利関係:

System Level Optimization Techniques for Low Power VLSI Design

System Level Optimization Techniques for Low Power VLSI Design

Tohru Ishihara

Kyushu University

November 1999

### Abstract

Low power design has emerged as an attractive theme both practically and theoretically in modern VLSI (Very Large Scale Integration) system design. Recently many power optimization techniques at various levels of abstractions such as at the layout, circuit, architectural, and system levels are proposed. In todays system design, power optimizations at higher level of abstraction are required, because decisions at the higher level of abstraction strongly affect to the cost, performance, and power consumption of final products. This thesis presents system-level power optimization techniques. A brief summary of system-level low-power design approaches combined with my own works will be described. It reviews some techniques that have been proposed to overcome power issues and gives guidelines for prospective system-level low-power designs.

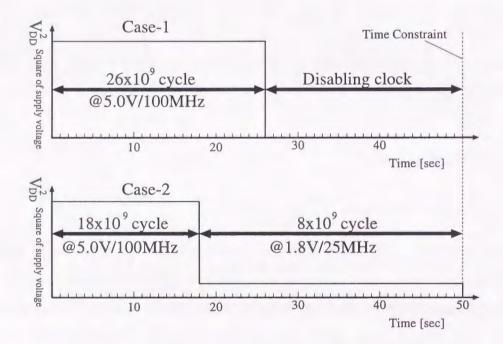

One of the most effective approaches for power reduction is voltage reduction, because the power consumption of CMOS circuits is quadratically proportional to the supply voltage. However, lowering the supply voltage leads to an increase of circuit delay. Therefore, system designers have to determine operating supply voltage, taking the power-delay trade-off into account. This thesis, first, introduces a new concept called voltage scheduling. This deals with a dynamically variable supply voltage. The voltage scheduling can formally be defined as follows: For a given task, determining a schedule of the processor's supply voltage so as to minimize the energy consumption for the task under a time constraint. An integer linear programming (ILP) model, theorems and an algorithm for the voltage scheduling problem are also presented in this thesis. Target systems include a variable voltage processor which can dynamically vary its supply voltage but can use only a single supply voltage at a time. For a given application program and the dynamically variable voltage processor, the algorithm finds a voltage schedule for each task so as to minimize the energy consumption satisfying a timing constraint.

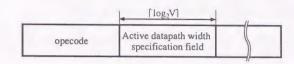

This thesis also presents *Power-Pro* architecture (Programmable Power Management Architecture), a novel processor architecture for power reduction. The *Power-Pro* architecture has two key functions: (i) The supply voltage and clock frequency of a microprocessor can be dynamically varied, and (ii) the active datapath width can be dynamically adjusted to the precision of each operation. This architecture aims to enable the software to dynamically control the active datapath width and the supply voltage. To make this possible, *Power-Pro* architecture employs complex instructions. With those instructions, programmers can dynamically vary the supply voltage, the clock frequency and the active datapath width. Experimental results show that power consumption for a variety of applications are dramatically reduced by the *Power-Pro* architecture.

Reducing the energy consumption throughout the whole system including hardware and software is one of the goals of this study. The hardware is often constructed by an embedded processor, an instruction memory and a data memory. The software and data which are executed and processed in the processor are usually stored in instruction memory and a data memory, respectively. Therefore, not only the processor but also the memories should be optimized for low power. A memory power optimization technique based on object code merging is also presented in this thesis. Basic idea is to merge sequences of frequently executed object codes into a set of single complex instructions. This complex instructions are restored by an instruction decompressor before decoding the object codes. The decompressor is implemented by ROM, and no modification to processor architecture is required for any application programs. Therefore, the technique is well suited for systems with embedded IP (Intellectual Property) cores whose internal architecture cannot be modified. In many programs, only a few object code sequences are frequently executed. Therefore, merging these frequently executed sequences into a set of single instructions leads to a significant energy reduction. Our experiments with actual read only memory (ROM) modules and some benchmark programs demonstrate significant energy reductions of up to more than 50% compared with processor-based systems without the object code merging.

The power reduction techniques which are proposed in this thesis can be applied together to a wide range of digital systems. Therefore, significant power reduction can be expected by these techniques, even if the power improvement by each of the techniques is modest. The variable datapath width control scheme can reduce the energy consumption of both the data memory and the processor's datapath by 35%. The energy consumption of the processor can

be reduced by 90% at best via the variable voltage control scheme. The energy consumption of the instruction memory can be halved by the object code merging technique. For example, if the control logic circuit of the processor, the processor's datapath, the instruction memory, and the data memory dissipate 25% of the total energy in a conventional system, we can reduce two third of the total energy dissipation in the same system by applying our proposed techniques.

ABSTRACT

## Contents

| A              | bstra | et                                                | i  |

|----------------|-------|---------------------------------------------------|----|

| C              | onter | nts                                               | v  |

| 1 Introduction |       |                                                   |    |

|                | 1.1   | Background                                        | 1  |

|                | 1.2   | Goal of This Research                             | 2  |

|                | 1.3   | Policy of This Research                           | 3  |

|                | 1.4   | Contributions of This Research                    | 4  |

|                | 1.5   | Organization of This Thesis                       | 6  |

| 2              | Low   | Power System Design                               | 7  |

|                | 2.1   | Power Dissipation Models                          | 7  |

|                | 2.2   | Optimization of Supply Voltage                    | 10 |

|                |       | 2.2.1 Power Reduction by Parallel Computation     | 11 |

|                |       | 2.2.2 Power Reduction by Adaptive Voltage Scaling | 12 |

|                | 2.3   | Reducing the Switching Activity                   | 13 |

|                |       | 2.3.1 Reducing Wasteful Switching Activity        | 13 |

|                |       | 2.3.2 Optimizing Signal Protocols and Encoding    | 13 |

|                |       | 2.3.3 Optimization by Algorithm Selection         | 14 |

|                | 2.4   | Reducing the Frequently Switched Capacitance      | 15 |

|                |       | 2.4.1 Memory Power Optimization                   | 15 |

|                |       | 2.4.2 Power Reduction for Cache Memory Systems    | 15 |

|                |       | 2.4.3 Optimization of Standard Cell Library       | 15 |

|                | 2.5   | Optimization of the Number of Execution Cycles    | 16 |

| vi |     |                                                         | ONTEN                                                                                                                                                                                                                                                                                                                                                      | TS |

|----|-----|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 2.6 | Summary                                                 |                                                                                                                                                                                                                                                                                                                                                            | 19 |

| 3  | Var | iable Voltage Scheduling                                |                                                                                                                                                                                                                                                                                                                                                            | 21 |

|    | 3.1 | Background                                              |                                                                                                                                                                                                                                                                                                                                                            | 21 |

|    |     | 3.1.1 Motivation                                        |                                                                                                                                                                                                                                                                                                                                                            | 21 |

|    |     | 3.1.2 Power Delay Trade-off                             |                                                                                                                                                                                                                                                                                                                                                            | 22 |

|    |     | 3.1.3 Motivational Example                              | 21          21          22          23          24         stic Model       30          35          35          36          37          39          42         rchitecture       45          45          47          49         rol       49         rol       49         rol       49         rol       49         rol       52         C scheme       52 |    |

|    | 3.2 | Basic Theorems on a Simple Model                        |                                                                                                                                                                                                                                                                                                                                                            | 24 |

|    | 3.3 | Generalized Theorems on a More Realistic Model          |                                                                                                                                                                                                                                                                                                                                                            | 30 |

|    | 3.4 | ILP Formulation                                         |                                                                                                                                                                                                                                                                                                                                                            | 35 |

|    |     | 3.4.1 Assumptions                                       |                                                                                                                                                                                                                                                                                                                                                            | 35 |

|    |     | 3.4.2 Notation                                          |                                                                                                                                                                                                                                                                                                                                                            | 35 |

|    |     | 3.4.3 Formulation                                       |                                                                                                                                                                                                                                                                                                                                                            | 36 |

|    | 3.5 | A Voltage Scheduling Algorithm                          |                                                                                                                                                                                                                                                                                                                                                            | 37 |

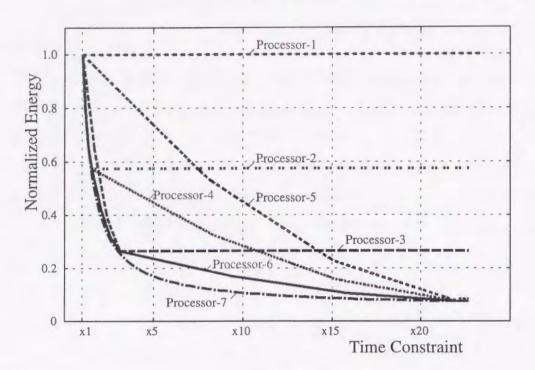

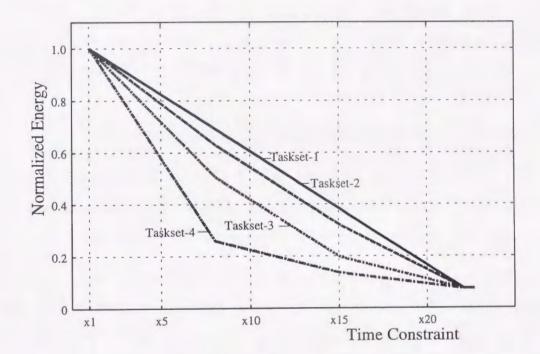

|    | 3.6 | Experimental Results                                    |                                                                                                                                                                                                                                                                                                                                                            | 39 |

|    | 3.7 | Summary                                                 |                                                                                                                                                                                                                                                                                                                                                            | 42 |

| 4  | Pro | grammable Power Management Architecture                 |                                                                                                                                                                                                                                                                                                                                                            | 45 |

|    | 4.1 | Background                                              |                                                                                                                                                                                                                                                                                                                                                            | 45 |

|    | 4.2 | Reduction of Wasteful Power Consumption                 |                                                                                                                                                                                                                                                                                                                                                            | 46 |

|    |     | 4.2.1 Power-Delay Optimization                          |                                                                                                                                                                                                                                                                                                                                                            | 47 |

|    |     | 4.2.2 Reduction of Wasteful Power in Datapath Circuits  |                                                                                                                                                                                                                                                                                                                                                            | 47 |

|    | 4.3 | The Power-Pro Architecture                              |                                                                                                                                                                                                                                                                                                                                                            | 49 |

|    |     | 4.3.1 PVC: Programmable $V_{DD}$ Control                |                                                                                                                                                                                                                                                                                                                                                            | 49 |

|    |     | 4.3.2 PADWC: Programmable Active Datapath Width Control |                                                                                                                                                                                                                                                                                                                                                            | 51 |

|    |     | 4.3.3 Architecture for <i>PADWC</i> scheme              |                                                                                                                                                                                                                                                                                                                                                            | 52 |

|    |     | 4.3.4 Special Instruction for <i>PADWC</i> scheme       |                                                                                                                                                                                                                                                                                                                                                            | 52 |

|    | 4.4 | Applications                                            |                                                                                                                                                                                                                                                                                                                                                            | 53 |

|    |     | 4.4.1 Applications for <i>PVC</i>                       |                                                                                                                                                                                                                                                                                                                                                            | 53 |

|    |     | 4.4.2 Applications for <i>PADWC</i>                     |                                                                                                                                                                                                                                                                                                                                                            | 55 |

|    | 4.5 | Experimental Results                                    |                                                                                                                                                                                                                                                                                                                                                            | 56 |

|    |     | 4.5.1 Experimental Results for PVC                      |                                                                                                                                                                                                                                                                                                                                                            | 56 |

| C  | ONT    | ENTS   |                                                       |   |   |   |   | vii |

|----|--------|--------|-------------------------------------------------------|---|---|---|---|-----|

|    |        | 4.5.2  | Experimental Results for PADWC                        |   |   | ٠ |   | 58  |

|    | 4.6    | Simul  | ation Results of Pilot Chip                           |   |   | • |   | 59  |

|    | 4.7    | Summ   | nary                                                  | ٠ | ٠ |   |   | 61  |

| 5  | Me     | mory l | Power Optimization with Code Merging                  |   |   |   |   | 63  |

|    | 5.1    | Backg  | ground                                                | ٠ |   |   |   | 63  |

|    | 5.2    | Motiv  | rations and Our Approach                              |   |   |   |   | 64  |

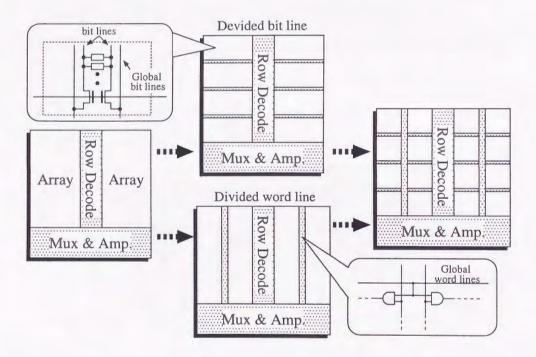

|    |        | 5.2.1  | Area-Power Correlation                                |   |   |   |   | 65  |

|    |        | 5.2.2  | Memory Reference Locality                             |   |   |   |   | 67  |

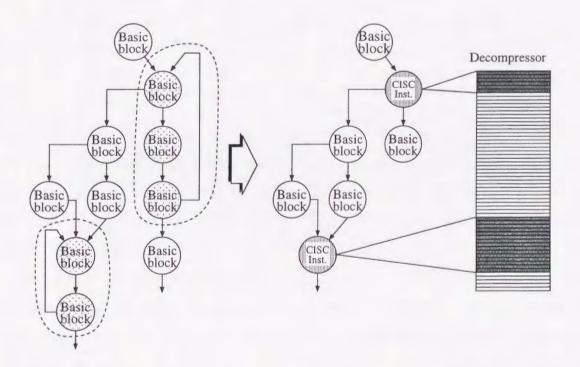

|    |        | 5.2.3  | Our Approach                                          |   | ٠ |   |   | 68  |

|    | 5.3    | Power  | Optimization with Object Code Merging                 |   |   |   |   | 70  |

|    |        | 5.3.1  | Optimization Flow                                     |   | ٠ |   |   | 70  |

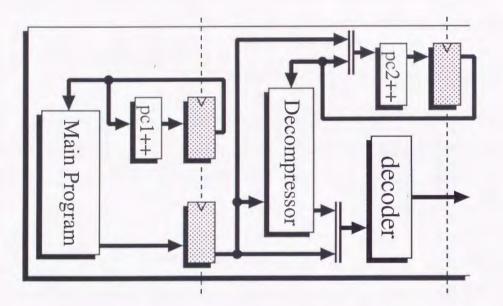

|    |        | 5.3.2  | Architecture                                          |   |   |   |   | 71  |

|    |        | 5.3.3  | ILP Formulation                                       |   |   |   |   | 73  |

|    |        | 5.3.4  | Algorithm                                             | ٠ |   |   |   | 74  |

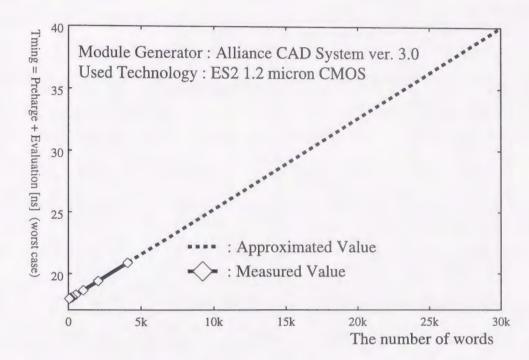

|    | 5.4    | Exper  | imental Results                                       | ٠ | ٠ |   |   | 76  |

|    |        | 5.4.1  | A Basic Block Packing Approach                        |   |   |   |   | 77  |

|    |        | 5.4.2  | A Sequence Merging Approach                           |   |   |   |   | 81  |

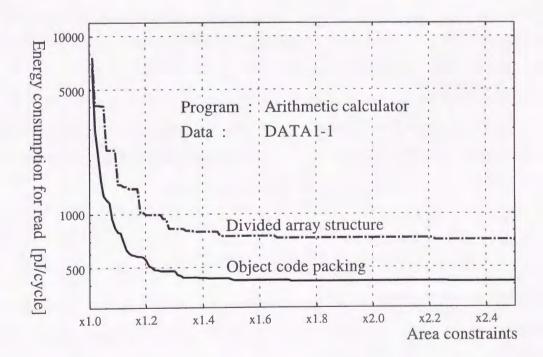

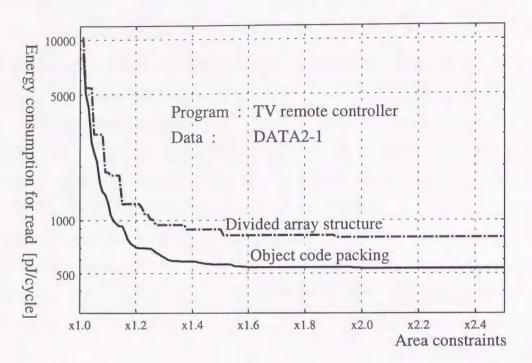

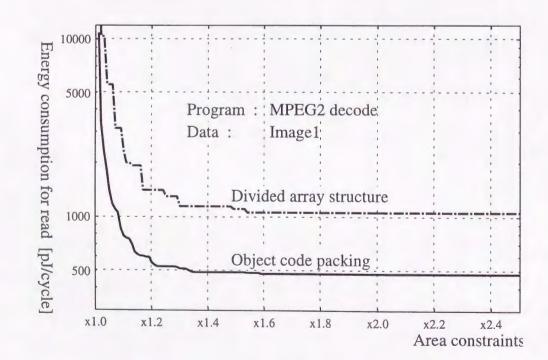

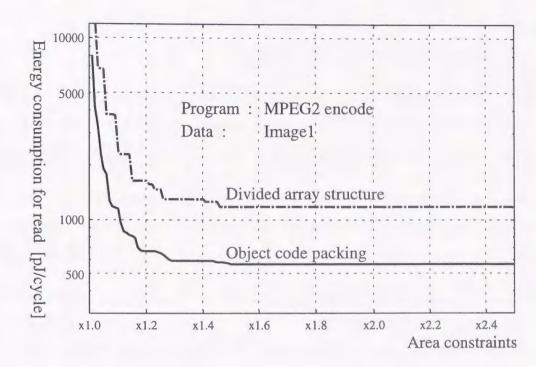

|    |        | 5.4.3  | A Basic Block Packing Approach under Area Constraints |   |   |   |   | 84  |

|    | 5.5    | Summ   | nary                                                  | ٠ |   |   |   | 87  |

| 6  | Con    | clusio | ns                                                    |   |   |   |   | 89  |

|    | 6.1    | Summ   | nary of Contributions                                 |   |   |   |   | 89  |

|    | 6.2    | Future | e Directions                                          | ٠ |   |   |   | 91  |

| A  | ckno   | wledgr | ment                                                  |   |   |   |   | 93  |

| Bi | ibliog | graphy |                                                       |   |   |   |   | 95  |

| Li | st of  | Public | cations by the Author                                 |   |   |   | 1 | 03  |

## Chapter 1

## Introduction

#### 1.1 Background

In past years, the most serious concerns for the VLSI designer were area, performance, cost, and reliability. Therefore, power considerations were mostly of only secondary issue. Recently, however, this paradigm is shifted, and power becomes more and more important issue. The primary driving factor of this paradigm shift must be explosive growth in the portable systems which demand high-speed computation and complex functionality with low power consumption.

In these applications power consumption is a critical design concern. The projected power consumption for a portable multimedia terminal when implemented components are not optimized for low-power operation is around the range of 10-50 W[58]. With advanced Nickel-Metal-Hydride battery technologies yielding around 65 watt-hours/kilogram, this terminal would require an unacceptable six kilograms of batteries for ten hours of operation between recharges[37].

There also exists a strong pressure for designers of high-end products to reduce their power consumption. Contemporary performance optimized microprocessors dissipate as much as 15-50W at 100-200MHz clock rates[58]. In the future, it can be expected that a 10 cm<sup>2</sup> microprocessor, clocked at 500MHz would consume about 300W. The cost associated with packaging and cooling such devices is huge. Consequently, there is a clear advantage to reducing the power consumed in high performance systems. Conversely, lowering the power is indispensable for consumer products whose sales are strongly affected by its price. There-

fore, for VLSI chips which are embedded in the consumer products, a rising heat of the chips becomes one of limiting factor to realize higher transistor density and computational speed. Though the motivations for reducing power consumption differ from application to application, power reduction is an essential theme in whole of today's electronics industry.

The most of low power system design process can be divided into the following two phases. (i) The power estimation, and (ii) the power optimization. In todays system design, power estimation and optimization at higher level of abstraction are required, because decision at the higher level of abstraction strongly affect to the cost, performance, and power consumption of final products. This thesis will present both power estimation and optimization techniques at the system level abstraction. A VLSI system design can be represented at several levels of abstraction such as at the layout, logic circuit, architectural, and system levels. The hardware design process is often performed by gradually detailing the abstract specification to lower level of abstraction. A behavioral level specifies the functionality of the design and may contain no structural information. A structural level represents the circuit as an interconnection of elements or building blocks. Synthesis tools can automatically convert or refine a design from a higher level of abstraction to a lower level of abstraction, or can convert a behavioral level description to a structural level description. At the system level, the design may be modeled as a set of abstract communicating processes or tasks, with no knowledge of whether the tasks are implemented in hardware or compiled into software running on an embedded processor. System level synthesis involves partitioning the tasks into hardware and software, choosing the processor architecture that will execute the software, determining the hardware/software communication mechanism, and so on. This thesis proposes power optimization techniques at the system level abstraction. These techniques perform the power optimization taking both hardware and software into account, and have much more impacts on the quality of the final products than lower level optimization techniques have.

#### 1.2 Goal of This Research

The goal of this research is to develop not only a low power system but also a high performance system with low power dissipation. Low power technologies support development higher density transistor and increased computational speeds in future VLSIs, because the heat produced by the VLSI chips is one of the limiting factors in developing larger scale and higher

speed computer systems. Low power is also essential to high performance battery powered systems. Another important issue for these applications is not only power consumption, but also energy consumption, that is a summation of power consumption. The goal of this research is to reduce both power consumption and energy consumption of VLSI systems.

To realize high performance computation with low power consumption, a power-delay optimization should be done. Basic idea of the power-delay optimization is to lower the supply voltage as much as possible satisfying a computation time constraint. The power-delay optimization technique can dramatically reduce power and energy consumption without essential performance degradation. This thesis presents theories for the power-delay optimization in the system design level. This thesis also proposes a technique to reduce redundant switching on datapath circuits. This technique can reduce energy consumption in the datapath circuits and a data memory with a trivial performance degradation.

Developing low power system within very short time is also the goal of this study, because turn around time (TAT) in VLSI system design has strong impacts on the sales of products in these days. One of the most effective ways to reduce the time to market is design reuse. This thesis propose a memory power optimization technique which aims to develop low power instruction memory within very short design time.

Energy reduction techniques presented in this thesis can be applied together to wide range of digital systems. Therefore, the great energy reduction can be expected by these techniques, even if the energy improvement by each technique is modest.

#### 1.3 Policy of This Research

Since the energy consumption of CMOS circuits is almost proportional to switching activity, load capacitances and the square of supply voltage, lowering these design parameters leads to the energy reduction. However, lowering the supply voltage causes performance degradation, because the clock frequency is almost proportional to the supply voltage. Our policy is to reduce energy consumption without essential performance degradation as described below.

• Eliminate wasteful switching activities which are not essential to the result of the computation.

- Saving energy by eliminating extra computational speed which is excessive for a required computational speed.

- Reduce load capacitances of frequently used parts, even if the load capacitances of rarely used parts are increased.

Basic idea of the approach to eliminate wasteful switching is to inactivate unnecessary bits of a datapath. For example, if all bits of a datapath in a 32-bit processor are switched for the computation of 8 bit data, many wasteful switching are occurred in upper 24 bits of the datapath. Inactivating such a wasteful switching activity, we can drastically reduce the power consumption without any changes of computation scheme.

A scheme to save energy by eliminating an extra computational speed which is excessive for a required computational speed is also proposed in this thesis. In CMOS transistor, power dissipation is quadratically proportional to supply voltage. Lowering the supply voltage has strong impact on power reduction for CMOS circuits. However, this causes computational speed degradation. We can reduce the power consumption by lowering the supply voltage until the computational speed of a system matches a desired computational speed. A compiler technique which can find the supply voltage which adjust the computational speed of the target system to the required computational speed are addressed in this thesis.

This thesis also presents a compiler technique to reduce load capacitances of frequently used parts in an instruction memory. A basic idea is to merge frequently executed basic blocks into a set of single complex instructions. Although the load capacitances of rarely used memory blocks are increased, total energy consumption can be dramatically reduced.

#### 1.4 Contributions of This Research

The energy consumption of whole system,  $E_{global}$ , can be defined as the summation of both partial and temporal power consumption of circuits as shown in (1.1).

$$E_{global} = \sum_{i=1}^{X} \sum_{k=1}^{N} p_{ik}$$

(1.1)

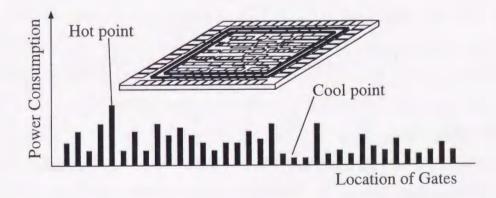

The  $p_{ik}$  denotes a gate  $g_k$ 's power dissipated during the *i*th period of time, X the execution time of a program (software), and N the number of gates in the VLSI chip. In this thesis, we treat  $E_{global}$  as an objective function to be optimized, because the energy consumption

directory affects the heat of chips and the life of battery. Since the  $p_{ik}$ s are dynamically varied according to the behavior of the software and a location of the logic gate on a chip, both the software and the hardware should be taken into account to reduce the energy consumption. This thesis proposes the system level optimization techniques which consider behavior of both the hardware and the software. The most important contribution of this research is to develop methods which enables the software to manage the energy consumption, and methods to optimize application specific systems utilizing a history of the application programs. Detailed contributions of this research are described below.

- A compiler technique to determine the optimal supply voltage which minimizes energy consumption under a time constraint is proposed.

- Some theorems which give guidelines to find an optimal operating supply voltage for microprocessors in practical situations are proved.

- A microprocessor architecture which enables the software to control the supply voltage and active datapath width dynamically is proposed.

- A reconfigurable instruction memory architecture targeting low power application specific systems is proposed.

- An object code merging technique to reduce power dissipation in an instruction memory is proposed.

First, a new microprocessor architecture, called *Power-Pro: Programmable Power Management Architecture*, is presented. This architecture can vary its supply voltage and active datapath width by special instructions. They make it possible to control the power consumption and the performance of microprocessors by software.

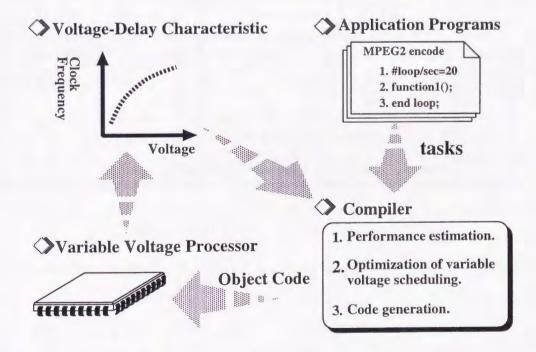

Next, a compiler technique to determine the optimal supply voltage for dynamically variable voltage processors, which minimizes energy consumption under a time constraint is proposed. A procedure to deciding optimal supply voltage for given tasks is called voltage scheduling. Two kinds of information are required for the voltage scheduling. One is a voltage-delay relations of the dynamically variable voltage processor. The other information is a program source in which real-time constraints are explicitly specified. Firstly, the compiler estimate the worst case execution cycles of the application program. Secondly, the

compiler finds an optimal voltage schedule, using the informations of the estimated execution cycles of the program and the voltage-delay relations of the processor. The voltage scheduling is done based on the theorems presented in chapter 3. The optimal voltage schedule minimizes energy consumption without any real-time violations. Finally, an object code including the special instructions which can vary the supply voltage is generated for the dynamically variable voltage processor. A problem to find optimal voltage schedule is formulated as an integer linear programming (ILP) problem. An voltage scheduling algorithm for the problem is also proposed in this thesis.

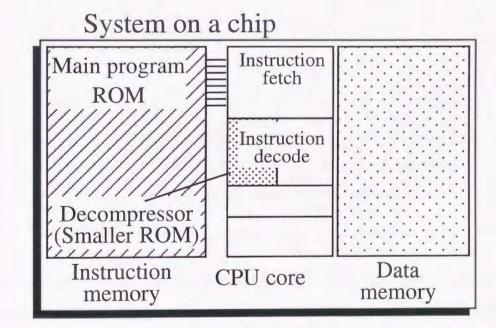

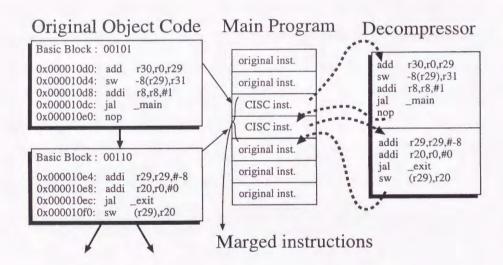

A compiler technique with object code merging to reduce power dissipation of an instruction memory is also proposed. This technique targets a microprocessor which has an instruction decompressor to restore the merged sequences of object codes. Merging frequently executed sequences of object codes into a set of single complex instructions reduces energy during memory access, because the number of memory access to the main program memory is extremely reduced. However, merging too many sequences of object codes into single instructions leads to an increase of energy consumption in the instruction decompressor. The proposed technique finds optimal point of this trade-off where total energy consumption is minimized. A problem to find the optimal point of the trade-off is formulated as an integer linear programming (ILP) problem. An algorithm to solve the problem is also proposed.

#### 1.5 Organization of This Thesis

This thesis addresses mainly tree topics, variable voltage scheduling, a programmable power management architecture, and an object code merging for application specific systems, and is organized as follows.

First, in Chapter 2, low power design methodologies at the system level abstraction are outlined.

Chapter 3 presents the variable voltage scheduling method for the dynamically variable voltage processors. Chapter 4 presents a programmable power management architecture which enables the software to control supply voltage and active datapath width. Chapter 5 proposes a new architecture for embedded instruction memories, and presents a memory power optimization technique with an object code merging.

Chapter 6 concludes this thesis with a summary and a direction of future research.

## Chapter 2

## Low Power System Design

#### 2.1 Power Dissipation Models

With the popularization of portable electronics and the rising demands for cooling down the heat of high-end products, it becomes more important for VLSI systems to reduce power consumption. Recently, many power minimization schemes at various levels of abstraction, such as at device, circuit, layout, architectural and system levels are proposed[43]. As for the low level design, power optimization techniques are well studied. However, there is much scope left to study in the system level area such as architectural, algorithm, or software level. In this chapter, we present system level power and energy reduction approaches.

In many applications, not only power dissipation but also energy dissipation is critical design concern. We can define the energy consumption as the summation of both partial and temporal power consumption in a VLSI circuit as shown in Figure 2.1 and 2.3.

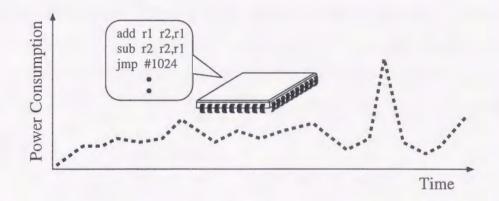

Figure 2.1: Partial power dissipation in CMOS circuits.

In this thesis, we treat the energy consumption as an objective function to be improved, because the energy consumption directory affects the heat of chips and the life of the battery. Our challenge is to model and optimize the energy consumption of whole system at the higher level of abstraction. The dominant source of energy dissipation throughout a digital CMOS circuit synchronized by a system clock is the dynamic energy dissipation,

$$E_i = \sum_{k=1}^{M} CL_k \cdot Swit_{ik} \cdot V_{DD}^2$$

(2.1)

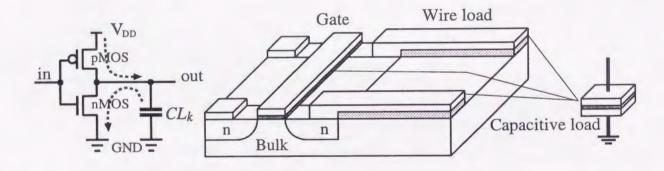

where  $E_i$  is energy dissipation while the *i*th clock cycle is executed, M the number of gates in the circuits,  $CL_k$  the load capacitance of a gate  $g_k$ ,  $Swit_{ik}$  the switching count of  $g_k$  while the *i*th clock cycle is executed, and  $V_{DD}$  the supply voltage. Basically, the dynamic energy arises only when the capacitive load of the output of CMOS circuit is charged through the power supply or is discharged to ground as shown in Figure 2.2.

Figure 2.2: Power dissipation in CMOS circuits.

Some researchers have proposed several accurate energy dissipation model for CMOS circuits [59, 10, 28, 5], and make sure accuracy of their models. We have also examined the accuracy of (2.1) by measuring the energy dissipation of actual chips[48, 49]. An analog ammeter, an oscilloscope, and an in-house energy measuring instrument are used to measure the energy of the chips. The experimental result with actual chips and many kinds of test vectors demonstrates that the maximum error of (2.1) is 12% at most, and the accuracy of (2.1) is very good.

Next, let us consider a task j with the number of total execution cycles  $X_j$ , where the task means a fragment of a program. Since the energy for the task is a summation of  $E_i$  by the number of the execution cycle  $X_j$ , the energy consumption for the task is formulated as (2.2).

Figure 2.3: Temporal power dissipation in CMOS circuits.

$$E_{task} = \sum_{i=1}^{X_j} E_i = \sum_{i=1}^{X_j} \sum_{k=1}^{M} CL_k \cdot Swit_{ik} \cdot V_{DD}^2$$

(2.2)

We can reduce the energy consumption for the task by lowering  $V_{DD}$ ,  $Swit_{ik}$ ,  $CL_k$ , M, or  $X_j$ . However, lowering these design parameters causes increase of execution time for the task. The circuit delay  $\tau$  which determines maximum clock frequency of VLSI systems synchronized by a system clock is formulated as (2.3), and an execution time for the task  $T_{task}$  can be formulated as (2.4),

$$\tau \propto \frac{V_{DD}}{\left(V_G - V_T\right)^2} \sim \frac{1}{V_{DD}} \tag{2.3}$$

$$T_{task} = \tau \cdot X_j \tag{2.4}$$

where  $V_T$  is the threshold voltage, and  $V_G(\sim V_{DD})$  the voltage of the input gate. Formulas (2.2) and (2.4) demonstrate design trade-offs in CMOS VLSI systems, because of the following reasons.

- The  $E_{task}$  is quadratically proportional to the  $V_{DD}$ , and the  $T_{task}$  is inversely proportional to the  $V_{DD}$ .

- The  $X_j$  strongly depends on the  $CL_k$ , M, and the  $Swit_{ik}$ . For example, highly parallelized circuits which require large  $CL_k$ s, M, and  $Swit_{ik}$ s can execute the task within a small  $X_j$ . Conversely, serialized computation which requires small M,  $CL_k$ s, and  $Swit_{ik}$ s needs large  $X_j$ .

Our challenge is to minimize the total energy consumption for the task under a given computation time constraint. According to the relations among  $V_{DD}$ ,  $Swit_{ik}$ ,  $CL_k$ ,  $X_j$ ,  $E_{task}$  and  $T_{task}$ , we can consider the following approaches for the minimization of the energy consumption.

- 1. Lowering the  $V_{DD}$  under the computation time constraints.

- 2. Reducing the  $\sum_{i=1}^{X_j} \sum_{k=1}^{M} (Swit_{ik})$  keeping the  $T_{task}$ .

- 3. Reducing the  $\sum_{i=1}^{X_j} \sum_{k=1}^{M} (CL_k \cdot Swit_{ik})$  keeping the  $T_{task}$ .

- 4. Optimizing the  $X_i$  so as to minimize the  $E_{task}$  under the computation time constraints.

In this chapter, we will make a brief survey on the above approaches in system level LSI design and show several examples in detail. The rest of the chapter is organized in the following way. In Section 2.2, we present approaches for supply voltage optimization. Approaches for lowering the switching activity and frequently activated capacitance are presented in section 2.3 and 2.4, respectively. Section 2.5 presents the optimization of the number of the execution cycles to minimize the energy for the task. The chapter is concluded in Section 2.6.

#### 2.2 Optimization of Supply Voltage

Since energy dissipation is quadratically proportional to supply voltage  $V_{DD}$  (see equation (2.2)), controlling  $V_{DD}$  has strong impacts on energy reduction[41]. A main difficulty of energy reduction by  $V_{DD}$  optimization is how to resolve the trade-off between system performance and energy dissipation formulated in (2.2) and (2.4). We have to develop design methods to minimize energy consumption keeping system performance required in specifications of systems. Basically, we have the following two ways to reduce  $V_{DD}$  in system level design.

#### 2.2.1 Power Reduction by Parallel Computation

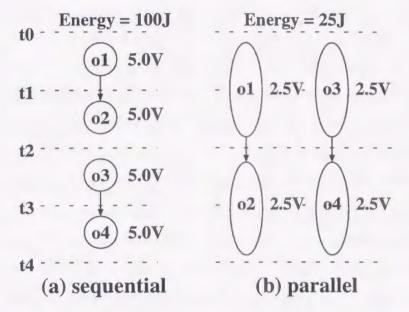

Figure 2.4: Power reduction by parallel computation.

This method utilizes performance improvement by parallel computation. Suppose that our computation is completely parallelizable into two parallel tasks. Introducing two circuits for the tasks, we can reduce the performance of each task without loss of system performance as shown in Fig. 2.4. If ideally we can reduce the performance of each circuit into half of the original one, we can reduce  $V_{DD}$ s of them into half because of the power-performance relation of equation (2.3). Although load capacitance and switching activities in a cycle may increase up to twice respectively, we can reduce the number of cycles into half and  $V_{DD}^2$  into quarter. Although this is a very attractive approach, parallelization of computation is difficult in general because of the control and data dependency in many programs. Some computations are inherently sequential and it is difficult to enjoy the power reduction scheme for them.

In the past few years, multiple supply voltage scheduling technique were proposed [26, 39, 34]. The techniques refer to the assignment of a supply voltage to each operation in a data flow graph so as to minimize the average energy consumption under given computation time or throughput constraints or both. Since in such techniques, supply voltage is statically

assigned to each functional module, they become ineffective if performance requirements dynamically change according to the operating conditions.

#### 2.2.2 Power Reduction by Adaptive Voltage Scaling

More practical approach is adaptive power control techniques. Since the load of our computation is not constant, we can control power consumption according to the required computation load. Preparing multiple supply voltages, we can assign them for tasks of computation keeping the total performance of the system. The assignment can be done statically or dynamically. In the rest of this section, we will discuss the adaptive power control.

Low power techniques with dynamic voltage scaling also have been studied [60, 33, 18]. Nielsen et al. have shown a low-power system using self-timed circuits. The circuits achieve maximum power savings by lowering the supply voltage until the performance of chip can meet the specific performance requirement. In this system, the supply voltage is controlled by hardware directly. This can be a disadvantage for some kinds of applications, because it is difficult to know detailed behavior of the application program from the hardware. Therefore, a technique to control the supply voltage from software is required for sophisticated power management system.

Intel and Microsoft have proposed a specification called Advanced Power Management (APM)[13]. This specification defines an interface between power management software in BIOS, and a hardware-independent power management driver in operating system. This driver can manage APM-aware applications, by notifying them processor state changes. Although the APM makes possible to manage the power consumption from application program, how to decide the optimal operating supply voltage, or hardware specification which control the supply voltage from application program are not presented.

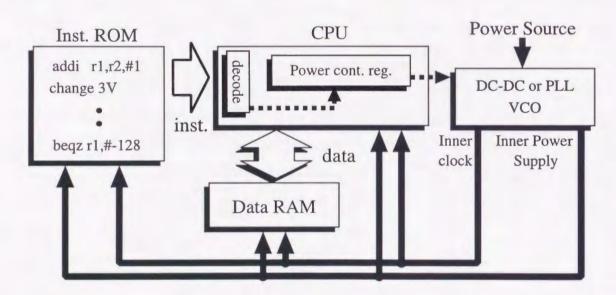

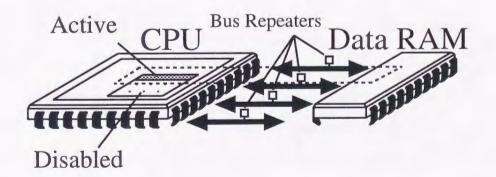

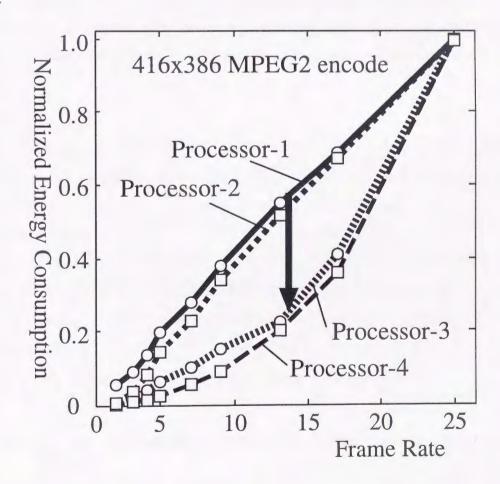

We have proposed a dynamically variable voltage processor architecture called *Power-Pro* architecture in [52, 50]. The architecture can use dynamically variable supply voltage but can use a single supply voltage at a time. The architecture has special instruction, called *voltage* control instruction to vary its own supply voltage and clock frequency. Using the instruction, software programmers can directly specify the operating supply voltage of the hardware in an application program. The most important issue for the variable voltage processor is how to select suitable voltages according to the operating condition. We have also proposed a voltage

scheduling problem which treats dynamically variable supply voltage, and have proposed theorems and an algorithm for the problem in [53, 50, 56]. In[24, 63] theories to determine the optimal supply voltage for dynamically variable voltage processors are presented.

In many practical applications, the number of cycles is changed depending on the sort of data. Since it is difficult to know statically the number of execution cycles, which are often much smaller than the worst case, an application of the voltage scheduling by the compiler will be limited. Dynamic voltage scheduling by operating systems will be an important technique for system level power reduction [63]. A real-time operating system which assigns voltage as low as possible to each task without any real-time violations has proposed [56].

Developing low power DC-DC converters is one of the most important themes for variable voltage VLSIs, because the power dissipation of the DC-DC converter is not negligible for very low power VLSI circuits. Recently, many types of DC-DC converters have been proposed [18, 44, 41, 46, 16]. In [16], a DC-DC converter whose energy efficiency reaches up to 95% in the supplying power range of 40-100mW is proposed. These low power DC-DC converters promise the variable voltage techniques to be essential in prospective low power applications.

#### 2.3 Reducing the Switching Activity

In system level design, we have three basic approaches to reduce the switching activity.

#### 2.3.1 Reducing Wasteful Switching Activity

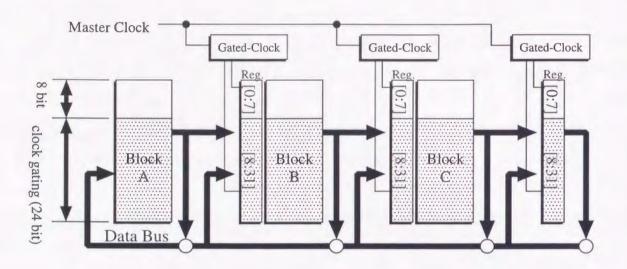

Usually, computation contains many wasteful switching activities, which are not essential to the result of the computation. For example, all bit lines of data bus in a 32-bit processor are switched for the computation of 8 bit data. If we take care of these wasteful switches, we can drastically reduce power consumption without any changes of computation scheme. Gated clock is a popular method in this approach[36, 61, 8].

#### 2.3.2 Optimizing Signal Protocols and Encoding

Protocols and encoding schemes of long communication lines, which have large capacitive loads, strongly affect power consumption. In system level design, the protocols and coding schemes can be designed for minimizing power consumption. For application specific system

design, statistic information on data and/or control flows are useful for the optimization. As examples of this approach, optimization of ordering of data transfer and coding on buses are discussed by several researchers[42, 21].

#### 2.3.3 Optimization by Algorithm Selection

Above two approaches do not require essential change of computation algorithms. The number of switching is, however, inherently depends on the computation algorithm. Unfortunately, techniques of algorithms selection for power reduction have not been established yet. But it is a very important research area both theoretically and practically. In order to demonstrate the effects of the algorithms selection, we show, in table 2.2, an example of energy consumption of different multiplication algorithms in table 2.1[55]. All multiplier circuits are automatically synthesized with an automatic synthesis tool of SYNOPSYS co. ltd., and automatic place and route tool of Avant! co. ltd.. Energy consumption of each circuit is estimated with post-layout simulation. Bit width of the all the multipliers are 16 bits. Toggle count is a criterion of switching activity. The toggle count of Mult-3 is 70% of one of Mult-4. The energy consumption of Mult-3 is also 70% of one of Mult-4.

Table 2 1. Specifications of multipliers

| Table 2.1: Specifications of multipliers.        |                                                  |  |  |

|--------------------------------------------------|--------------------------------------------------|--|--|

| Circuits                                         | Algorithms                                       |  |  |

| Mult-1 A array multiplier with Booth's algorithm |                                                  |  |  |

| Mult-2                                           | A Wallace tree multiplier with Booth's algorithm |  |  |

| Mult-3                                           | A multiplier with 7-3 parallel counters          |  |  |

| Mult-4                                           | A multiplier with redundant binary adders        |  |  |

Table 2.2: Switching activity of multipliers.

| Circuits | Area $[\mu m^2]$ (# of cells) | Delay[ns] | Toggle count/Cycle | Energy/Cycle [pJ] |

|----------|-------------------------------|-----------|--------------------|-------------------|

| Mult-1   | 666462.7 (786)                | 23.76     | 926.95             | 65.48             |

| Mult-2   | 800846.2 (1,067)              | 15.77     | 779.78             | 65.40             |

| Mult-3   | 978017.0 (1,344)              | 12.98     | 604.37             | 63.97             |

| Mult-4   | 896409.4 (1,440)              | 13.95     | 861.42             | 87.15             |

#### 2.4 Reducing the Frequently Switched Capacitance

#### 2.4.1 Memory Power Optimization

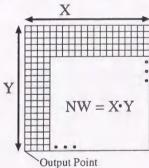

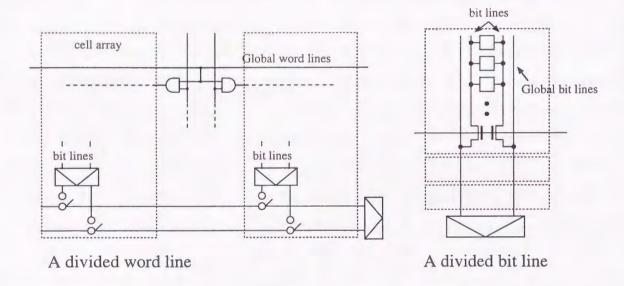

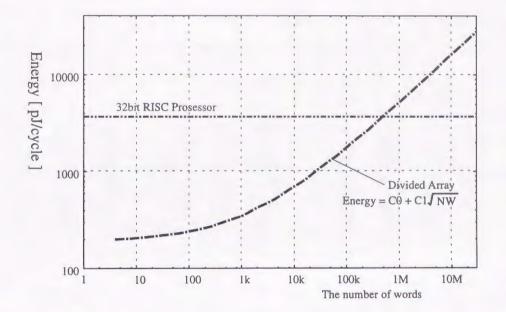

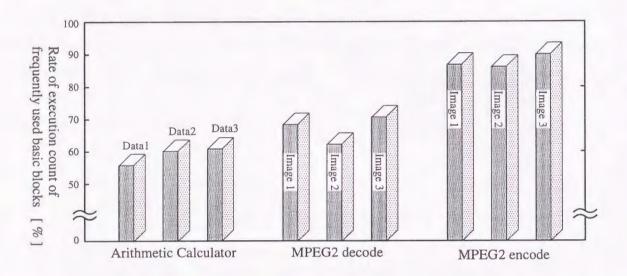

Some parts of a system are more active than other parts. According to equation (2.2), reducing load capacitance of the active parts leads to energy reduction of a whole system. This kinds of design efforts are usually done in circuit and layout design levels. But there are rooms to discuss efforts on the switching capacitance reduction in system level design. In many applications, only a few parts of programs are frequently used. Furthermore, some parts of the programs or some parts of circuits are not activated for some kinds of input data. Therefore, reducing the load capacitance of frequently accessed memory blocks or frequently activated parts of circuits may be effective way to reduce total energy consumption[32]. Here, we will show a challenge of the power reduction of memory-intensive systems, such as video image processing and speech recognition [54]. Detailed discussion will be done in chapter 5.

#### 2.4.2 Power Reduction for Cache Memory Systems

Because of the large load capacitance in off chip buses, local computation with cache memory is one of the most effective way to reduce power consumption during memory access. Some low power cache approaches which are aiming to reduce the cache miss ratio have proposed [40, 29, 20]. In [30], way-predictable set-associative cache memory architecture is proposed. Basic idea is to predict which way of four way contain a data desired by a processor. The experimental results demonstrate that about 70% energy improvement is achieved by the way predicting cache with 10% performance degradation, compared with a conventional set-associative cache.

#### 2.4.3 Optimization of Standard Cell Library

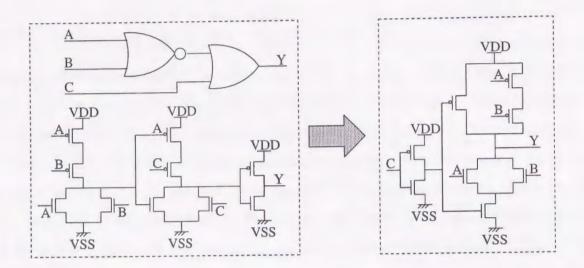

An application specific library generation techniques for low power VLSI design has been proposed[19, 47]. Main purpose of the techniques are to suit gate size, P/N size ratio, or a function set to the applications. In [47], a function set of cell library is determined for each target circuit so as to take frequently switching interconnects into cells. For example, if an output node of a NOR gate in Figure 2.5 is frequently switched, this node should be taken into a complex gate so as not to dissipate a wasteful power in this node. When the

logic function Y is realized by a complex gate and the logic value of the C is 1, no energy is dissipated in the complex gate ideally.

Figure 2.5: Power optimization with complex gates.

It is wide consensus that a power consumption in interconnects becomes much dominant in the near future. Therefore, the application specific library generation techniques can be much important power reduction technique in the future. The experimental results with some benchmark circuits demonstrate that this library generation technique can reduce much power consumption.

#### 2.5 Optimization of the Number of Execution Cycles

A glance at the equations (2.2) and (2.4) shows that reducing the number of execution cycles  $(X_j)$  leads to the reduction of both energy consumption and execution time for the task. However, reducing the number of execution cycles without increase of M,  $CL_k$ , or  $Swit_{ik}$  is difficult in general (See equations (2.2) and (2.4)). In addition, reducing  $X_j$  may cause an increase of circuit delay  $\tau$  (See equation (2.3)), because the most simple approach to reduce the  $X_j$  is utilizing highly parallelized large circuits, and large circuits often contains long interconnects which cause large wire delay. Therefore, techniques which resolve trade-offs among  $CL_k$ ,  $Swit_{ik}$ ,  $\tau$  and  $X_j$  are required for energy reduction. In this section, we present

a technique to resolve the trade-offs among  $CL_k$ ,  $Swit_{ik}$ , and  $X_j$  by tuning up the datapath width of a core processor.

The datapath width of a processor strongly affects to the power consumption in the system including, the processor, data RAMs, and instruction ROMs. In the following discussion, we suppose that the precision of computation should be preserved.

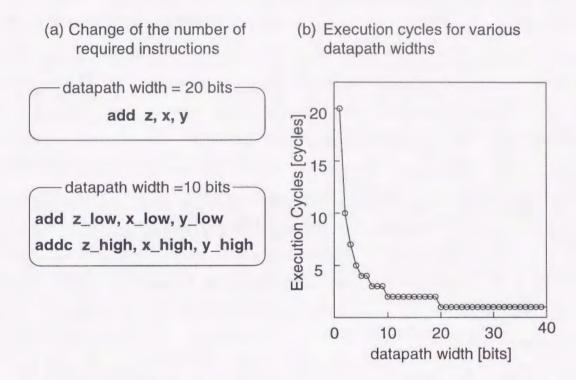

Figure 2.6: The number of execution cycles for various datapath width.

The datapath width of the processor also affects to the number of execution cycles of a given task, i.e., narrowing the datapath width causes the increase of the number of execution cycles because of the increase of cycles for multiple-precision operations. Assume that an addition of 20 bit data shown in Figure 2.6 is executed by only one instruction on a 20 bit processor. If the datapath width is 10 bits, two instructions including additions of lower 10 bits and higher 10 bits with carry (See Fig. 2.6 (a)) are required. Figure 2.6 (b) demonstrate trade-offs between datapath width and the number of execution cycles. Although a processor with narrower datapath width dissipates lower power per clock cycle, the total energy for the task can not always be reduced by narrowing the datapath width[1].

18

To determine whether computing with wide bit width and small number of execution cycles, or computing with narrow bit width and large number of execution cycles is a major concern for a hardware and software design. In this section, we present a hardware/software codesign approach for the datapath width optimization which minimize the energy consumption under computation time constraints.

Most important issue for the datapath width optimization is how to determine the effective size of variables. The effective size of a variable stands for the minimum required size which can hold both the largest and smallest values of the variable. A method to analyze effective sizes of variables in C program is proposed in [22]. A programming language and a compiler technique which support programmers to specify the minimum required bit width for each variable directly in source program was proposed in [23, 2]. The proposed language and the compiler are called Valen-C and Valen-C compiler, respectively. The Valen-C compiler preserves the precision of programs in the following manner: If a variable v is defined as a v bit variable, the v valen-v compiler allocates physical storage resources (registers and memory words) of not less than v bits for v. Arithmetic and logic operations for v are also performed with the precision of not less than v bits. In cases that the precision of an operation is larger than the datapath width, the operation is performed by more than one machine cycles as a multi-precision operation.

A new design methodology of embedded systems based on the *Valen-C* and a user defined application specific processor, called a *soft-core* processor, is proposed in [23]. The *soft-core* processor is a prototype of an embedded processor design, which has some design parameters, such as the datapath width, the number of registers, the kind of functional units, and the size of memories[17]. Designers can change the parameters for each application, and then obtain a customized processor optimized for the application. In other words, the total power consumption of a system including the *soft-core* processor, ROM and RAM can be optimized by changing the word length.

A system level energy optimization technique using *Valen-C* and the *soft-core* processor is proposed in [1]. Their objective is to optimize the datapath width so as to minimize the energy consumption for the task using the method of variable size analysis, the *Valen-C*, and the *soft-core* processor.

#### 2.6 Summary

This chapter reviews some system level low power design techniques that have been proposed to overcome the power issue, and demonstrate that a system level decision has strong effect to energy consumption as well as to system cost and performance. Although hardware approaches for power reduction at higher level of abstraction are studied well, there may be much scope left to explore in software area. The key technologies that we believe to be important in prospective VLSI system design are summarized below.

- Create a model of the system including hardware and software at higher level of abstraction.

- Estimate power consumption of the system including hardware and software at higher level of abstraction.

- Optimize the total energy consumed by the system for given applications considering behavior of both hardware and software.

Power concerns must be most important issue for VLSI system design, and breakthrough to overcome the power issue will be required in the near future. This thesis will outline future challenges to develop high performance and low power VLSI systems.

## Chapter 3

## Variable Voltage Scheduling

#### 3.1 Background

Lowering the supply voltage has strong impact on power reduction, because the power consumption of CMOS circuits is quadratically proportional to the supply voltage. However the circuit delay is almost inversely proportional to the supply voltage. Basically, therefore, system designers have to consider the trade-off between a computational speed and energy consumption to realize high performance computation with low power consumption. In recent researches, datapath scheduling techniques and behavioral synthesis techniques with multiple supply voltage were proposed [26, 39, 62]. The proposed scheduling problem refers to the assignment of a supply voltages to each operation in a data flow graph so as to minimize the average energy consumption for given computation time or throughput constraints or both. The experimental results demonstrates 20-30% power reduction. However, these techniques can sometimes be ineffective when the computation time constraints are dynamically varied, because such techniques statically assign the supply voltage to each functional module. Power reduction techniques which treat dynamically variable supply voltage have much effect for actual systems in which the computation time constraints are changed according to the performance requirements of applications.

#### 3.1.1 Motivation

In the past few years, some low power techniques by dynamic voltage scaling have been studied [60, 33, 18, 45]. L. Nielsen et al. has shown a low-power system using self-timed circuits

and adaptive scaling of the supply voltage in [33]. The self-timed circuits achieve maximum power savings by lowering the supply voltage until the chip can just meet the specific performance requirement. Their approach scales supply voltage dynamically according to the quantity of processing data per unit time. Similar to our approach, their approach can find optimal supply voltage which is fitting to the desired performance. However, the problem definition is quite different from our approach, because their approach is based on an adaptive method. Our approach is based on an intentional voltage scheduling method[53, 50]. In this chapter, we address a voltage scheduling problem and formulate it to an ILP(Integer Linear Programming) problem. Target systems include the dynamically variable voltage processor which can dynamically vary its supply voltage but can use only a single voltage at a time[52].

This chapter is organized in the following way. In section 3.2 and 3.3, we prove basic and more generalized theorems, respectively. Section 3.4 and 3.5 present ILP formulation and an algorithm for the problem, respectively. Experimental results are shown in section 3.6. Section 3.7 concludes this chapter.

#### 3.1.2 Power Delay Trade-off

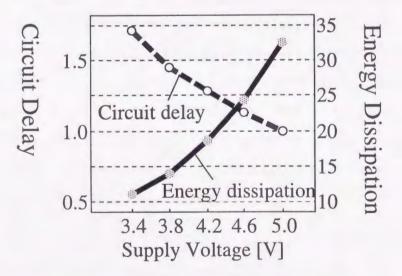

The dominant source of energy dissipation in a digital CMOS circuit is the dynamic energy dissipation, as shown in (2.1), and is quadratically proportional to the supply voltage. Conversely, the circuit delay is inversely proportional to the supply voltage as shown in (2.3). As is shown in Fig. 3.1, (2.1) and (2.3) demonstrates the power-delay trade-off in CMOS circuits.

Figure 3.1: The power-delay trade-off in CMOS circuits.

System designers have to take this design trade-off into account to reduce energy consumption without essential performance degradation.

#### 3.1.3 Motivational Example

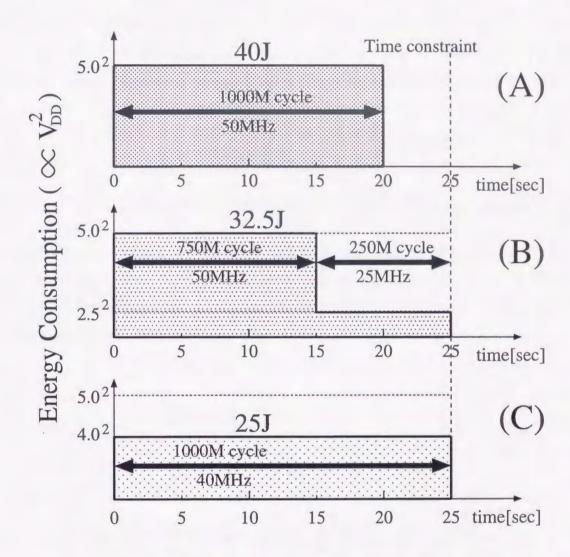

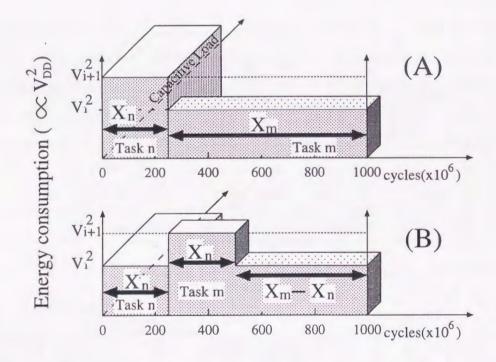

Figure 3.2: An example of power-delay optimization.

The main purpose of our power saving approach is to optimize the power-delay trade-off. The goal of the power-delay optimization is minimizing the power consumption by scheduling the supply voltage for each task under a given time constraint, where the task is a fragment of a program. Assume that the energy consumptions for a given program are 10nJ/cycle, 25nJ/cycle and 40nJ/cycle at 2.5V, 4.0V and 5.0V, respectively. The computational speeds

26

of the processor with 5.0V, 4.0V, and 2.5V are  $(50 \times 10^6 \text{ clock cycles})/\text{second}$ ,  $(40 \times 10^6 \text{ clock cycles})/\text{second}$ , and  $(25 \times 10^6 \text{ clock cycles})/\text{second}$ , respectively. This assumption roughly accords to (2.1) and (2.3). Figure 3.2 shows three voltage schedules for the given program whose total execution cycles are  $1000 \times 10^6 \text{ cycles}$ . In Fig. 3.2(A), the total energy consumption is 40J, because a processor uses only a 5.0V supply voltage. Given a time constraint of 25 seconds, the voltage scheduling with 2.5V and 5.0V which adjusts the finishing time to the given timing deadline reduces the energy consumption from 40J to 32.5J. Fig. 3.2(C) shows the lower bound case of this example. If the processor uses a single supply voltage which adjusts the finishing time just to the given timing deadline, the total energy consumption is minimized. We generalize these features in next section.

#### 3.2 Basic Theorems on a Simple Model

In this section, we target processors which assume to use continuously variable voltage between 0[V] and  $V_{max}[V](>0)$ . The energy consumption is assumed to be independent from operation types or input data but depends only on supply voltage. We regards the number of execution cycles to be a continuous value in this chapter, since the number of execution cycles is assumed to be enough big to regard a continuous value.

In deep submicron electronics, it is necessary to consider the effect of mobility degradation. After this, we use more accurate delay model (3.1) rather than (2.3), which takes the effect of mobility degradation into account [12],

$$\tau = \frac{k \cdot V_{DD}}{(V_{DD} - V_T)^{\alpha}} \tag{3.1}$$

where  $\alpha$  is a parameter which reflects the effect of mobility degradation upon circuit delay, and k is constant.

**Lemma 1** If a processor completes a program before the timing deadline T (0 < execution time < T), the energy consumption is not minimized.

**Proof.** At first, we prove that the circuit delay  $\tau(v)$  and energy consumption of CMOS circuits are the monotonous function of supply voltage v.

Let

$$au(v) = rac{k \cdot v}{(v - V_T)^{lpha}}$$

(k is a constant)

can not minimize energy consumption if the processor can use continuously variable voltages.

**Proof.** For any v, x, and  $\alpha$  which satisfy  $0 < V_T < V_1 < v < V_2 < V_{max}$ ,  $0 \le x \le Cycle$ , and  $1 \le \alpha \le 2$ , let us prove (3.3) under the constraint (3.2). Where Cycle stands for total execution cycles of the given program.

$$\frac{x \cdot V_1}{(V_1 - V_T)^{\alpha}} + \frac{(Cycle - x) \cdot V_2}{(V_2 - V_T)^{\alpha}} = \frac{Cycle \cdot v}{(v - V_T)^{\alpha}}$$

(3.2)

$$V_1^2 \cdot x + V_2^2 \cdot (Cycle - x) > v^2 \cdot Cycle \tag{3.3}$$

The left side of (3.2) and (3.3) represent the total execution time and normalized energy consumption, respectively, when x cycles are executed with voltage  $V_1$  and Cycle - x cycles are executed with voltage  $V_2$ . The right side of (3.2) and (3.3) represent, total execution time and energy consumption, respectively, when all cycles are executed with voltage v.

Put

$$T = \frac{x \cdot V_1}{(V_1 - V_T)^{\alpha}} + \frac{(Cycle - x) \cdot V_2}{(V_2 - V_T)^{\alpha}} = \frac{Cycle \cdot v}{(v - V_T)^{\alpha}}$$

$$f = V_1^2 \cdot x + V_2^2 \cdot (Cycle - x)$$

, and  $g = v^2 \cdot Cycle$ ,

then, x and v are functions of T. f and g are functions of x and v respectively.

Therefore, both f and g are function of T. The result which is differentiated by T is described below.

$$\frac{d f}{dT} = \frac{(V_1^2 - V_2^2) \cdot (V_1 - V_T)^{\alpha} \cdot (V_2 - V_T)^{\alpha}}{V_1 \cdot (V_2 - V_T)^{\alpha} - V_2 \cdot (V_1 - V_T)^{\alpha}} = constant < 0,$$

and,

$$\frac{d^2g}{dT^2} = \frac{\alpha \cdot \{2 \cdot V_T + (\alpha - 1) \cdot v\}(v - V_T)^{2\alpha + 1}}{Cycle^2 \cdot \{V_T + (\alpha - 1) \cdot v\}^3} > 0$$

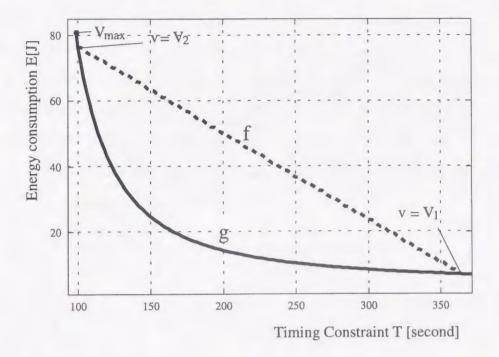

It is obvious that f is a linear function of the timing constraint T as shown in Figure 3.4. In addition, g is a below convex function of the timing constraint T.

Consequently, we have (3.4) under the condition (3.2).

$$f - g > 0 \tag{3.4}$$

25

we have,

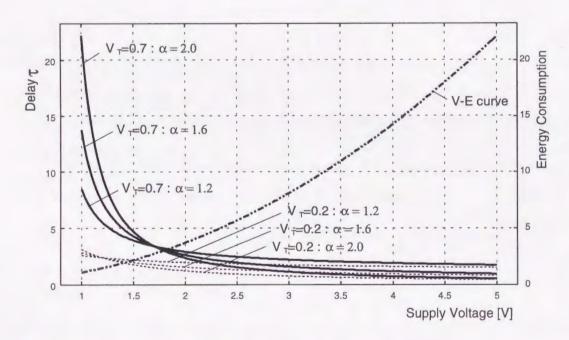

$$\frac{d\tau(v)}{dv} = -\frac{(\alpha-1) + k \cdot V_T}{(v - V_T)^{\alpha+1}}$$

Therefore, for  $\alpha$  (1.0  $\leq \alpha \leq$  2.0) and  $V_T$  (0  $< V_T < V$ ), the  $\tau(v)$  is monotonously decreased function of voltage v as shown in Figure 3.3. The  $\alpha$  strongly depends on the mobility degradation of electrons in MOS transistors, and tends to be decreased from 2.0 to 1.0 according to the channel size shrinkage. Threshold voltage  $V_T$  also tends to be decreased so as to improve transition delay and propagation delay of transistors.

It is immediate that the energy consumption is monotonously increased function of voltage v as shown in Figure 3.3. Therefore, high speed processing with high energy can be replaced by low speed processing with low energy. Namely, if a processor completes the processing before the timing deadline, slower and lower energy processing than such processing is possible. This lemma substantiates a well known power-delay trade-off in CMOS circuits for any practical  $\alpha$  and  $V_T$ .

Figure 3.3: V- $\tau$  curve for various  $V_T$  and  $\alpha$ .

**Lemma 2** If a processor uses a single supply voltage v and completes a program just at a timing constraint T(>0), the v is an unique supply voltage which minimizes energy consumption for the given program. In other words, voltage scheduling with multiple supply voltage

Figure 3.4: Energy consumption versus timing constraint.

(3.4) indicates that the voltage scheduling with two voltages can not minimize energy consumption. Furthermore, it is obvious that the voltage scheduling with more than two voltages can not minimize energy consumption.

An important information from Lemma 1 and Lemma 2 is that the voltage scheduling with the single voltage is optimal even if the transistor size and  $V_T$  are scaled down.

For ideal systems which can supply continuously variable voltages, Lemma 2 can be derived. However, using continuously variable voltages may be infeasible[11], since suppling any kinds of stable supply voltages and clock frequency wastes the significant power and hardware cost. In other words, processors do not always have a specified voltage which minimizes energy consumption. For processors which have only a small number of discretely variable voltages, we have the following theorem.

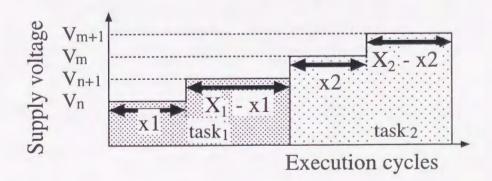

Theorem 1 If a processor can supply only a small number of discretely variable voltages, the voltage scheduling with at most two voltages minimizes the energy consumption under any time constraint.

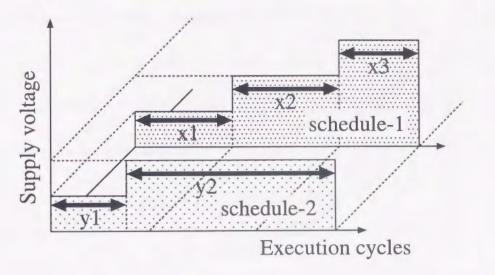

**Proof.** Consider the following two kinds of voltage scheduling: schedule-1 is the schedule with three voltages  $V_1$ ,  $V_2$ , and  $V_3$  ( $0 < V_1 < v_{ideal} < V_2 < V_3$ ), and schedule-2, the schedule with two voltages  $V_1$  and  $V_2$ . Now, let the execution cycles with  $V_1$ ,  $V_2$ , and  $V_3$  in schedule-1 be  $x1(\geq 0)$ ,  $x2(\geq 0)$ , and  $x3(\geq 0)$ , respectively. In addition,  $y1(\geq 0)$  and  $y2(\geq 0)$  cycles are assumed to be executed with  $V_1$  and  $V_2$  in schedule-2, respectively. We prove (3.5), under the constraints of (3.6) and (3.7).

$$V_1^2 \cdot x1 + V_2^2 \cdot x2 + V_3^2 \cdot x3 \ge V_1^2 \cdot y1 + V_2^2 \cdot y2 \tag{3.5}$$

$$\frac{x1 \cdot V_1}{(V_1 - V_T)^{\alpha}} + \frac{x2 \cdot V_2}{(V_2 - V_T)^{\alpha}} + \frac{x3 \cdot V_3}{(V_3 - V_T)^{\alpha}} = \frac{y1 \cdot V_1}{(V_1 - V_T)^{\alpha}} + \frac{y2 \cdot V_2}{(V_2 - V_T)^{\alpha}}$$

(3.6)

$$x1 + x2 + x3 = y1 + y2 (3.7)$$

The left and right sides of (3.5) represents the energy consumption of *schedule-1* and *schedule-2*, respectively. (3.6) and (3.7) explain that the total execution time and the execution cycles of two schedules must be same.

Firstly, assuming x1 < y1. If x1 < y1, the constraints (3.6) and (3.7) can not simultaneously be satisfied. Therefore, the situation x1 < y1 can not be occurred. We have only to consider the situation  $x1 \ge y1$  as shown in Figure 3.5. In this situation, (3.5), (3.6) and (3.7) can be deformed as (3.8), (3.9), (3.10), and (3.11).

$$(x1 - y1) + x3 = y2 - x2 (3.8)$$

$$\frac{(x_1 - y_1) \cdot V_1}{(V_1 - V_T)^{\alpha}} + \frac{x_3 \cdot V_3}{(V_3 - V_T)^{\alpha}} = \frac{(y_2 - x_2) \cdot V_2}{(V_2 - V_T)^{\alpha}}$$

(3.9)

$$V_1^2 \cdot (x1 - y1) + V_3^2 \cdot x3 \ge V_2^2 \cdot (y2 - x2) \tag{3.10}$$

$$x1 - y1 > 0, \quad y2 - x2 > 0, \quad x3 > 0$$

(3.11)

Figure 3.5: Voltage schedule-1 versus schedule-2.

From Lemma 2, (3.10) can be immediately proved under the constraints of (3.8), (3.9), and (3.11). Therefore, voltage scheduling with  $V_1$ ,  $V_2$ , and  $V_3$  can not minimize energy consumption, when  $0 < V_1 < v_{ideal} < V_2 < V_3$ . Similarly, it is easy to prove that the energy consumption of voltage scheduling with  $V_2$  and  $V_3$  is smaller than that with  $V_1$ ,  $V_2$  and  $V_3$ , when  $0 < V_1 < V_2 < v_{ideal} < V_3$ . Consequently, voltage scheduling with three voltage can not minimize energy consumption. The voltage scheduling with more than three voltages also can not minimize energy consumption.

**Theorem 2** If a processor can use only a small number of discretely variable voltages, the two voltages which minimize the energy consumption under a time constraint T are immediate neighbors to the voltage  $v_{ideal}$ .

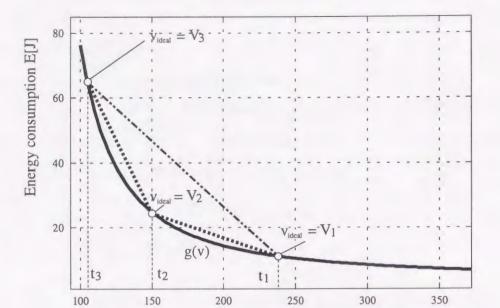

**Proof.** Assume that the processor can supply three voltages  $V_1$ ,  $V_2$ , and  $V_3$ . It has already been proved that the energy consumption is a linear function of the time constraint when the processor uses only two voltages as shown in Figure 3.6. If the time constraint T satisfies  $t_3 < T < t_2$ , voltage scheduling with  $V_3$  and  $V_2$  minimize energy consumption. In case that the time constraint T satisfies  $t_2 < T < t_1$ , voltage scheduling with  $V_2$  and  $V_1$  minimize energy consumption. Therefore, it is clear that the voltage scheduling with  $V_3$  and  $V_4$  can not minimize energy consumption. Consequently, the scheduling with two voltages which are immediate neighbors to the ideal voltage  $v_{ideal}$  minimizes the energy consumption.

Time Constraint T [seconds]

Figure 3.6: Voltage scheduling with two voltages.

Theorem 1 and Theorem 2 demonstrate significant feature of voltage scheduling. That is, only one time voltage alteration can minimize the energy consumption. Therefore time and power overhead of voltage alteration can be neglected for the practical real-time constraints.

#### 3.3 Generalized Theorems on a More Realistic Model

Up to here, we do not consider loads of tasks, which can be associated with charging and discharging the capacitive load occurred by the tasks. For example, charged and discharged capacitive load for an addition operation is quite different from the capacitive load for a multiply operation. If the capacitive load of each task is taken into account, processing the program with a single voltage which adjusts the execution time to the timing deadline does not always minimize energy consumption. In this section, we introduce a new term *capacitive load* which is formulated by (3.12).

Now, let us define new terms to make explanation more clearly.

- $task_j$  The jth task.  $task_j = \{X_j, C_j\}$ .

- $X_i$  The number of execution cycles of the jth task.  $(1 \le j \le N)$ .

- $C_j$  Average capacitive load for the jth task.

- M The number of gates in the processor.

- $Swit_{ijk}$  The switching count of  $gate_k$  while the *i*th cycle of  $task_j$  is executed.

The average capacitive load per cycle of  $task_j$  can be calculated by (3.12).

$$C_{j} = \frac{\sum_{i=1}^{X_{j}} \sum_{k=1}^{M} CL_{k} \cdot Swit_{kij}}{X_{j}}$$

(3.12)

Figure 3.7: Power-delay optimization considering the capacitive load.

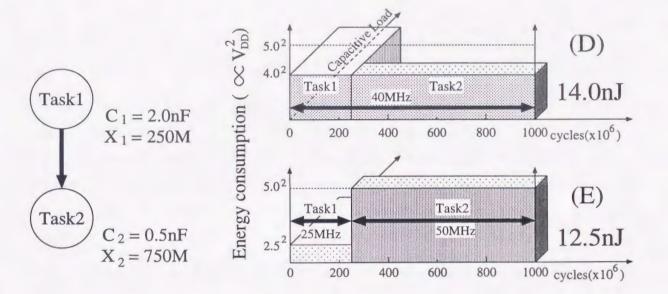

If the  $C_j$ s are much different from each other, voltage scheduling with multiple voltages sometimes minimizes the energy consumption for the processing. For a given task set =  $\{task_1, task_2\}$  as shown in Figure 3.7, the voltage scheduling with 2.5V and 5.0V as shown in Figure 3.7(E) reduces much energy compared to that with a single voltage (4.0V) as shown in Figure 3.7(D). For the both voltage scheduling, processor completes the 1000M cycles of program just at the timing constraint. The x, y, z axis of both graphs (D) and (E) in Figure 3.7 indicate the execution cycles, the square of supply voltage, and the capacitive load respectively. The volume of cubes indicates the energy consumption for processing.

32

Therefore, minimizing the total volume of cubes leads to a solution of the voltage scheduling problem.

Energy for scheduling(D) =  $(2.0nF \cdot 250M \cdot 4.0^2) + (0.5nF \cdot 750M \cdot 4.0^2) = 14.0J$

Energy for scheduling(E) =  $(2.0nF \cdot 250M \cdot 2.5^2) + (0.5nF \cdot 750M \cdot 5.0^2) = 12.5J$