## 組込みシステムの開発における協調検証手法と技術者教育への適用実践

清尾, 克彦

---

<https://doi.org/10.15017/1866322>

---

出版情報：九州大学, 2017, 博士（工学）, 課程博士

バージョン：

権利関係：

KYUSHU UNIVERSITY

# 組込みシステムの開発における協調検証手法と 技術者教育への適用実践

2017 年 8 月

清尾克彦

# 目次

|                                              |    |

|----------------------------------------------|----|

| 第1章 序論.....                                  | 1  |

| 1.1 研究の背景 .....                              | 1  |

| 1.2 組込みシステム開発における課題.....                     | 2  |

| 1.3 関連研究と本研究の位置付け .....                      | 3  |

| 1.4 研究の概要 .....                              | 4  |

| 1.5 論文の構成 .....                              | 5  |

| 第2章 組込みシステム開発の現状と課題.....                     | 7  |

| 2.1 組込みシステムとは.....                           | 7  |

| 2.2 組込みシステム開発の変遷.....                        | 9  |

| 2.3 組込みシステム製品の技術成熟度の変遷.....                  | 10 |

| 2.4 組込みシステムのプロダクト .....                      | 11 |

| 2.4.1 組込みシステム製品は多様な技術の集成体.....               | 12 |

| 2.4.2 ハードウェアとソフトウェアの協調設計 .....               | 13 |

| 2.4.3 組込みシステムにおけるトレードオフ設計 .....              | 15 |

| 2.4.4 組込みシステム製品のライフサイクル .....                | 17 |

| 2.5 組込みシステムにおける開発プロセス .....                  | 20 |

| 2.6 組込みシステム製品開発におけるプロジェクト .....              | 23 |

| 2.7 組込みシステムの開発に必要なスキル .....                  | 26 |

| 2.8 IoT 時代の組込みシステム .....                     | 27 |

| 2.9 組込みシステム開発における課題 .....                    | 31 |

| 2.9.1 検証の課題とその解決策 .....                      | 31 |

| 2.9.2 技術者育成の課題とその解決策 .....                   | 33 |

| 2.9.3 組込みシステムを包含した IoT システム開発について .....      | 33 |

| 2.10 まとめ.....                                | 34 |

| 第3章 トップダウン協調検証手法の提案と適用評価 .....               | 35 |

| 3.1 はじめに .....                               | 35 |

| 3.2 組込みシステムにおける検証の課題 .....                   | 36 |

| 3.3. 階層的な検証における現状と課題 .....                   | 37 |

| 3.3.1 階層的な検証における現状 .....                     | 37 |

| 3.3.2 階層的な検証における課題 .....                     | 40 |

| 3.4. トップダウン協調検証手法の提案 .....                   | 41 |

| 3.4.1 検証環境の統合と共通テストベンチの適用 .....              | 41 |

| 3.4.2 コンポーネント論理バスアーキテクチャによるインターフェースの統一 ..... | 42 |

| 3.5 マルチメディア系組込みシステムによる適用評価 .....             | 45 |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 3.5.1 協調設計・検証ツール .....                                 | 45        |

| 3.5.2 プロセッサのモデリング .....                                | 48        |

| 3.5.3 線描画システムによる評価 .....                               | 50        |

| 3.5.4 映像圧縮処理システムによる評価 .....                            | 53        |

| 3.6 考察 .....                                           | 62        |

| 3.7 まとめ .....                                          | 64        |

| <b>第4章 複合領域での教育手法をベースとした組込みシステム技術者教育の提案と実践評価 .....</b> | <b>66</b> |

| 4.1 はじめに .....                                         | 66        |

| 4.2 組込みシステムにおける必要なスキルと組込みシステム技術教育の現状 .....             | 66        |

| 4.2.1 組込みシステム製品開発で必要となるスキル .....                       | 66        |

| 4.2.2 組込みシステム分野の技術者育成の現状 .....                         | 68        |

| 4.3 組込みシステム技術教育の問題点 .....                              | 72        |

| 4.4 組込みシステム技術の教育手法の提案 .....                            | 73        |

| 4.4.1 組込みシステム技術教育の問題点に対する解決策の提案 .....                  | 73        |

| 4.4.2 組込みシステム開発におけるキャリアパスの提案 .....                     | 75        |

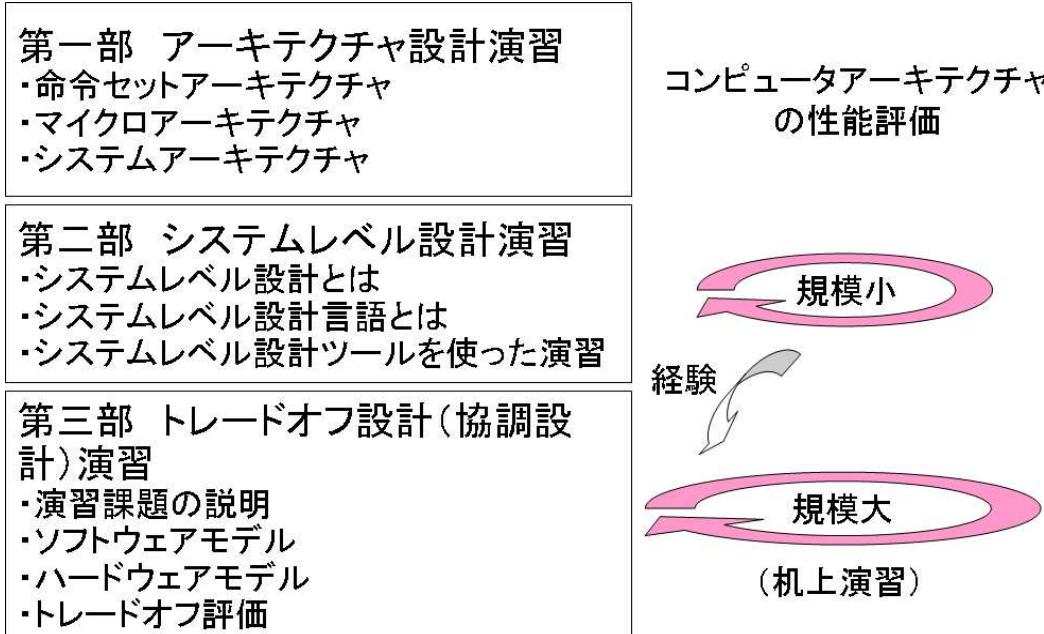

| 4.4.3 カリキュラムの構成 .....                                  | 76        |

| 4.5 組込みシステム教育への適用評価 .....                              | 77        |

| 4.5.1 入門コースでの取り組み .....                                | 78        |

| 4.5.2 初級コースでの取り組み .....                                | 79        |

| 4.5.3 中級コースでの取り組み .....                                | 81        |

| 4.6 考察 .....                                           | 83        |

| 4.7 IoT 時代の技術者育成についての考察 .....                          | 85        |

| 4.8 まとめ .....                                          | 86        |

| <b>第5章 結論 .....</b>                                    | <b>88</b> |

| 5.1 研究の成果 .....                                        | 88        |

| 5.2 今後の課題と取り組み .....                                   | 90        |

| 5.2.1 検証における今後の課題と取り組み .....                           | 90        |

| 5.2.2 技術者育成における今後の課題と取り組み .....                        | 91        |

| 謝辞 .....                                               | 94        |

| 参考論文（年代順） .....                                        | 95        |

| 参考文献 .....                                             | 96        |

| 用語集 .....                                              | 104       |

## 表目次

|                                  |    |

|----------------------------------|----|

| 表 3.1 各検証ステージでの評価内容              | 40 |

| 表 3.2 協調シミュレーションにおけるプロセッサのモデリング  | 49 |

| 表 3.3 協調エミュレーションにおけるプロセッサのモデリング  | 49 |

| 表 3.4 線描画システムにおける協調シミュレーションの実行結果 | 52 |

| 表 3.5 映像圧縮処理ユニットのトップダウン協調検証の実行結果 | 61 |

| 表 4.1 受講生の評価結果と主なコメント            | 84 |

## 図目次

|                                             |    |

|---------------------------------------------|----|

| 図 1.1 組込みシステム開発における課題分析と各研究の位置づけ            | 3  |

| 図 2.1 組込みシステムの主な特性                          | 8  |

| 図 2.2 情報通信社会の発展動向                           | 9  |

| 図 2.3 組込みシステム製品の技術的成熟度の変遷                   | 11 |

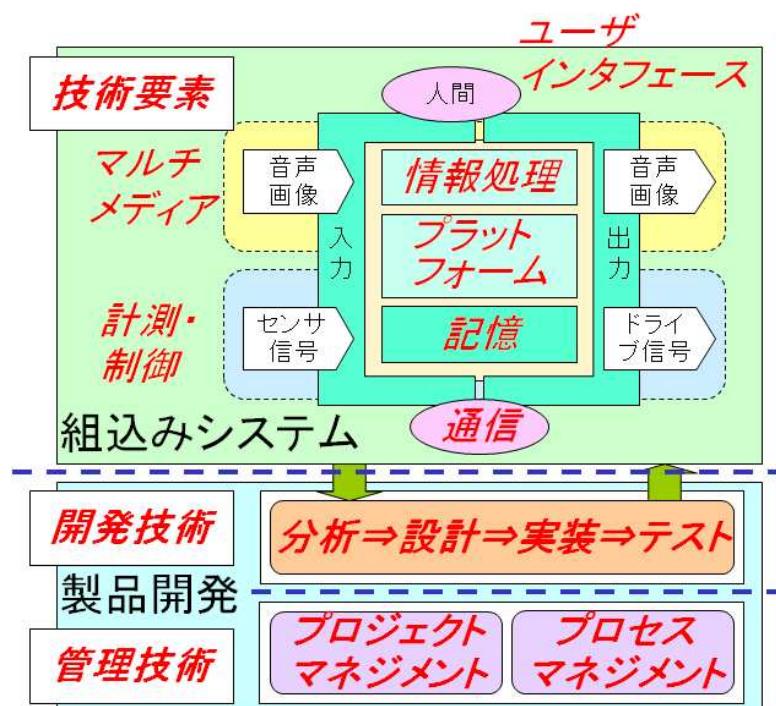

| 図 2.4 組込みシステムの概念的な構成                        | 12 |

| 図 2.5 組込みシステムのコンピュータ・システムの構成                | 14 |

| 図 2.6 トレードオフ設計の概要                           | 15 |

| 図 2.7 実行時間（性能の逆数）とコストによるトレードオフ評価の例          | 16 |

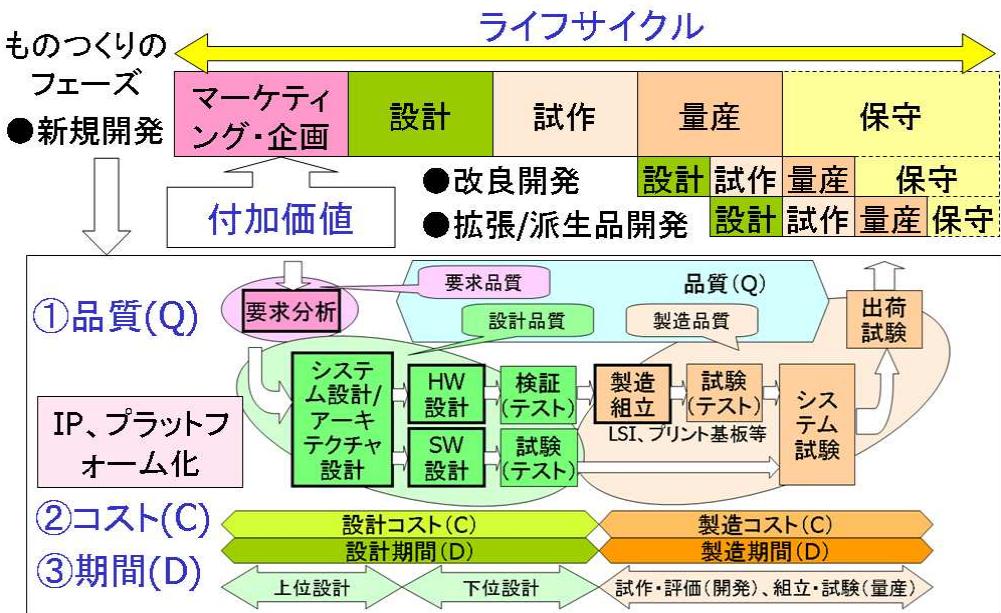

| 図 2.8 組込みシステム製品の開発ロードマップ                    | 17 |

| 図 2.9 組込みシステム開発のライフサイクルと開発プロセス              | 18 |

| 図 2.10 ライフサイクルにおける実現方法の変化                   | 19 |

| 図 2.11 JPEG（静止画圧縮伸張）の HW と SW のトレードオフ例      | 20 |

| 図 2.12 組込みシステムの開発プロセス                       | 21 |

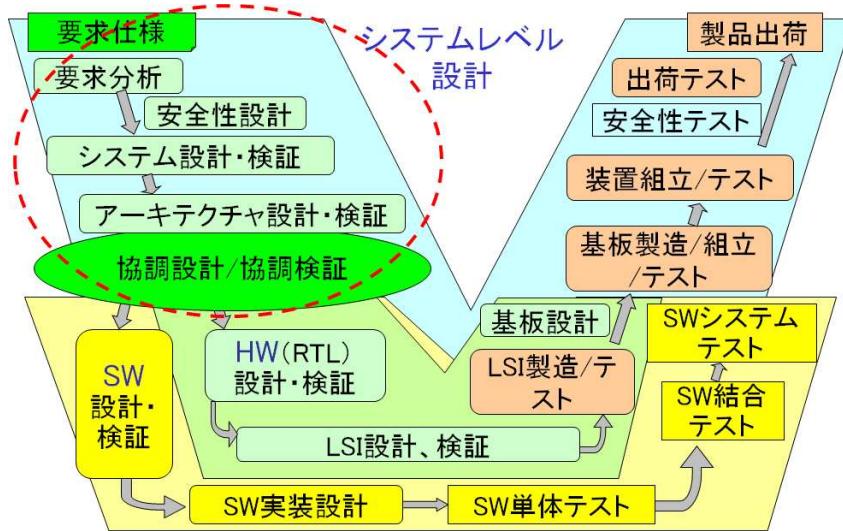

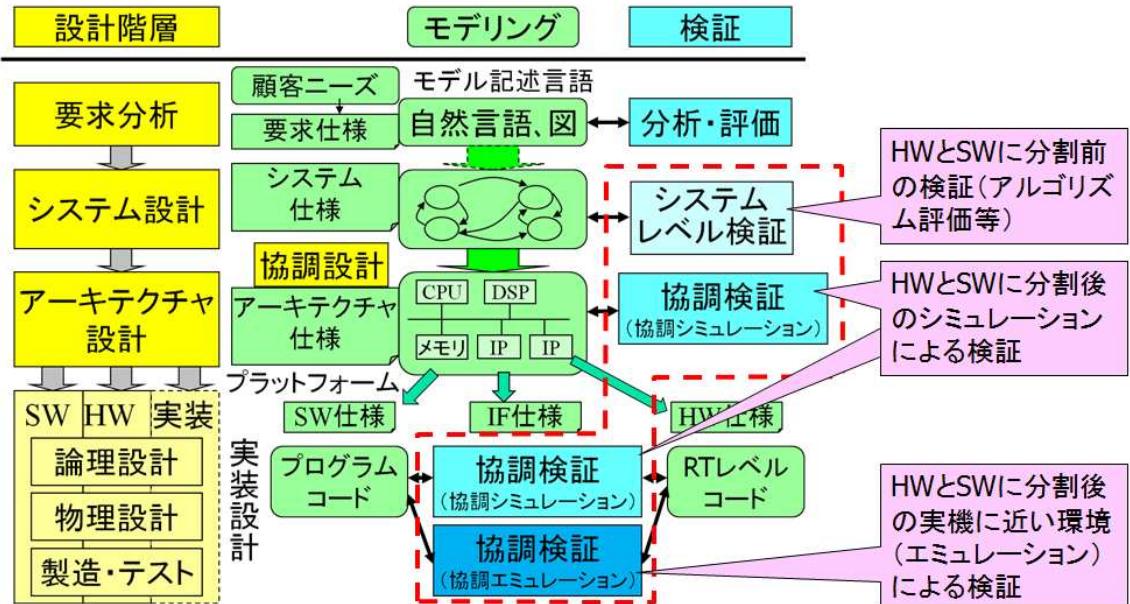

| 図 2.13 開発プロセスにおける協調設計・協調検証の位置づけ             | 22 |

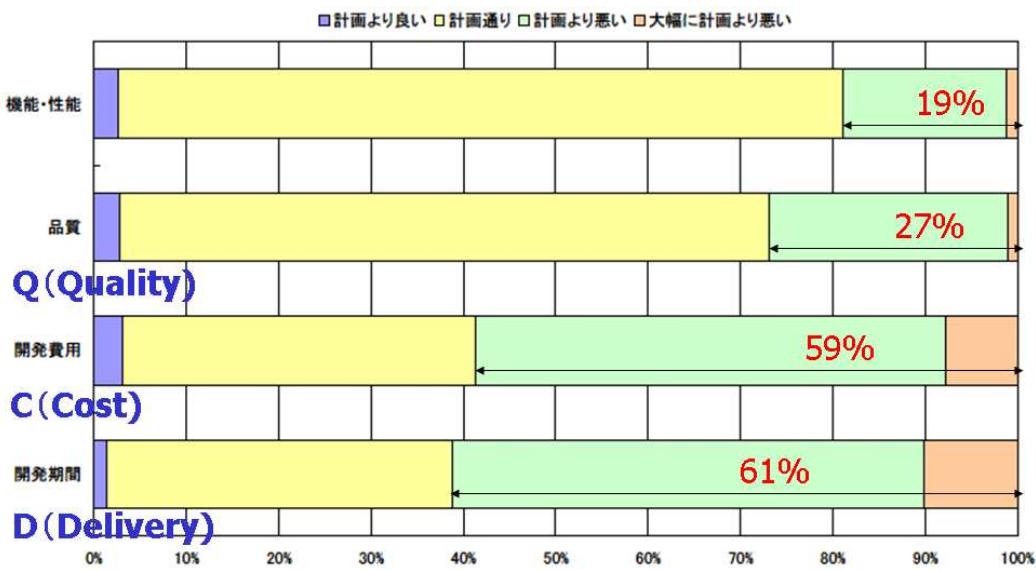

| 図 2.14 開発計画に対するプロジェクトの結果                    | 24 |

| 図 2.15 ハードウェアに起因して直面した課題                    | 24 |

| 図 2.16 プロジェクトマネジメントの概要                      | 25 |

| 図 2.17 組込みシステム開発に必要なスキル体系                   | 27 |

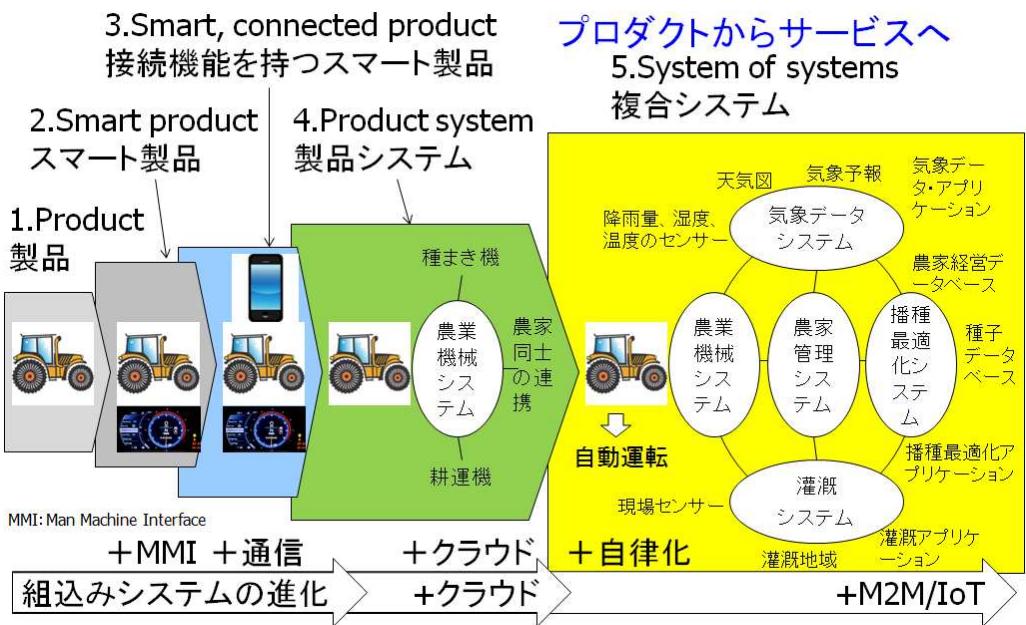

| 図 2.18 組込みシステム事業領域の変化（プロダクトからサービスへ）         | 28 |

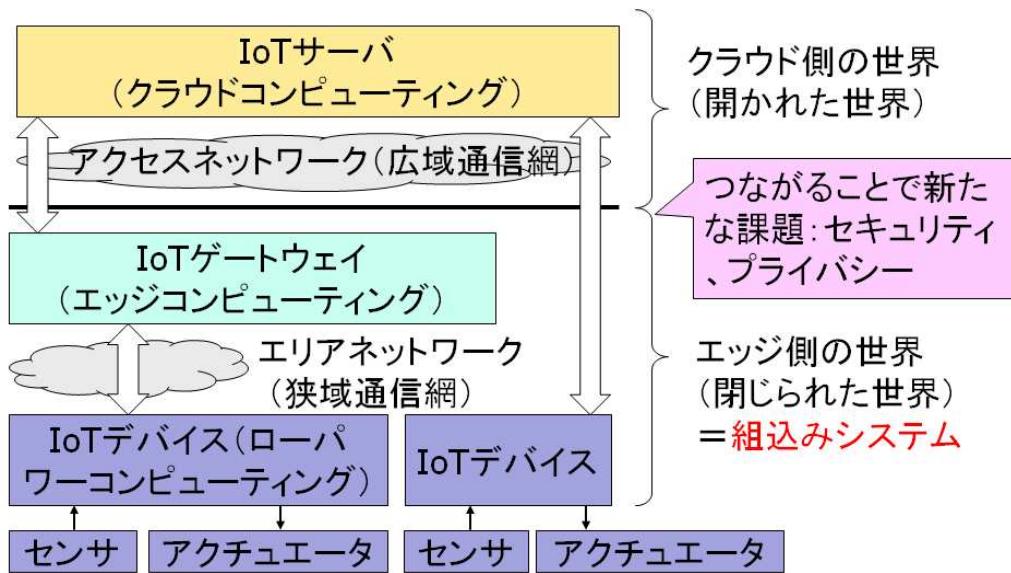

| 図 2.19 IoT 時代における組込みシステムの位置づけ（IoT システムの全体像） | 29 |

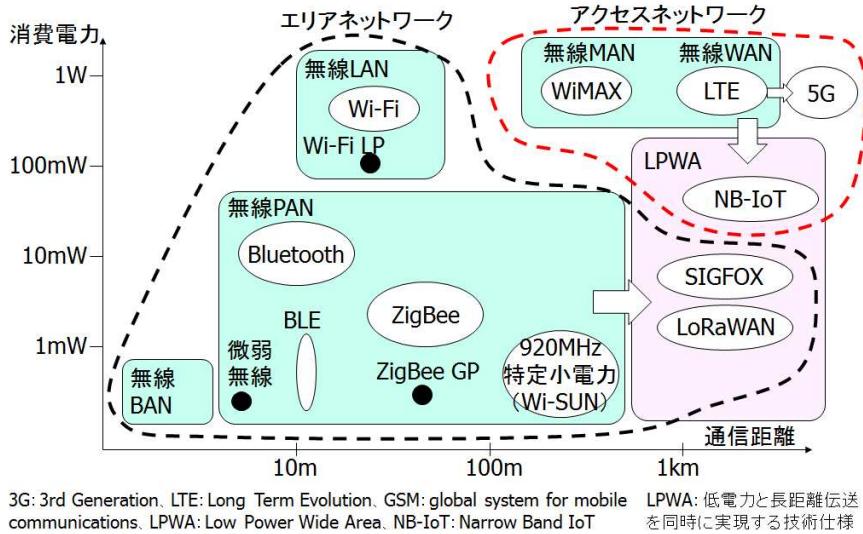

| 図 2.20 IoT ネットワークの全体像                       | 30 |

| 図 3.1 不良による影響度と発生コスト                        | 36 |

| 図 3.2 検証時間、検証工数の推移                          | 37 |

| 図 3.3 階層的な検証の全体像                            | 38 |

| 図 3.4 トップダウン協調検証手法の提案                       | 41 |

| 図 3.5 検証環境の統合と共に仕様のテストベンチの適用                | 42 |

| 図 3.6 コンポーネント論理バス（CLB）アーキテクチャの構成            | 43 |

| 図 3.7 協調シミュレーションにおけるインターフェースの実現方式           | 44 |

| 図 3.8 Tsutsuji の実行画面例                       | 46 |

| 図 3.9 Tsutsuji の開発環境                        | 46 |

| 図 3.10 Aptix 社システムエミュレータ MP4 の構成            | 47 |

| 図 3.11 システムエミュレータのアダプタ（自製）の例                | 47 |

| 図 3.12 システムエミュレータの開発環境                      | 48 |

|        |                                 |    |

|--------|---------------------------------|----|

| 図 3.13 | 線描画システムの構成                      | 50 |

| 図 3.14 | 線描画システムのコンポーネント論理バス（CLB）モデルの構成例 | 51 |

| 図 3.15 | 線描画システムの協調シミュレーション実行例           | 52 |

| 図 3.16 | 画像圧縮処理システムの構成例                  | 54 |

| 図 3.17 | トップダウン協調検証システムにおける検証ステージ        | 55 |

| 図 3.18 | システムレベルシミュレーション                 | 56 |

| 図 3.19 | 高位言語モデルによる協調シミュレーション            | 56 |

| 図 3.20 | 命令セットモデルによる協調シミュレーション           | 57 |

| 図 3.21 | 実チップモデルによる協調エミュレーション            | 58 |

| 図 3.22 | 映像圧縮処理システムのブロック図                | 59 |

| 図 3.23 | 映像圧縮処理システムの協調シミュレーション実行画面例      | 60 |

| 図 3.24 | 映像圧縮処理システムの協調エミュレーションの実行例       | 60 |

| 図 3.25 | 繰り返し検証の効率化                      | 62 |

| 図 3.26 | トップダウン協調検証手法の適用による効果            | 63 |

| 図 4.1  | 組込みシステム開発に必要なスキル体系と本論文での対応      | 67 |

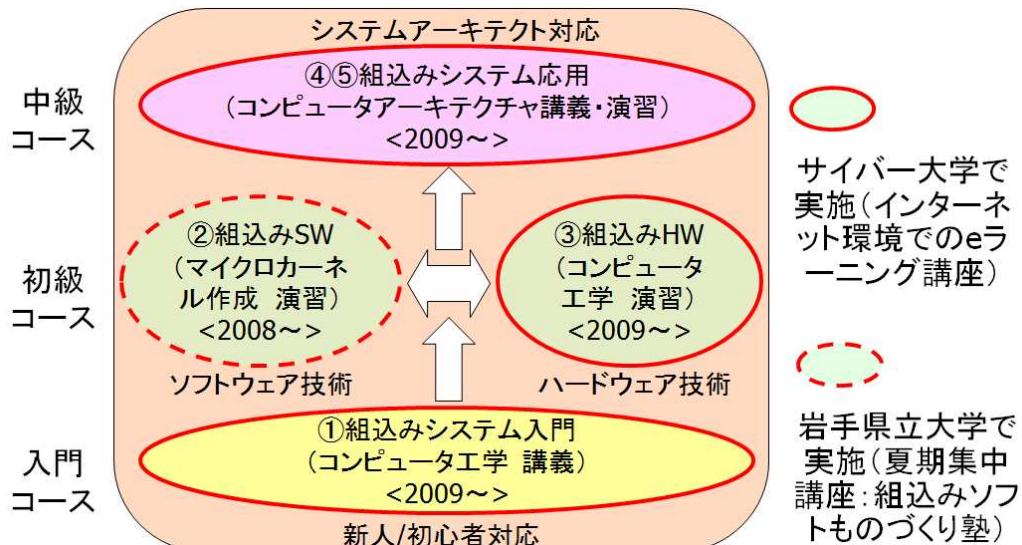

| 図 4.2  | 組込みシステム分野の技術者育成の現状              | 69 |

| 図 4.3  | 領域間のインターフェースの両面からの取り組みの例        | 74 |

| 図 4.4  | 組込みシステム開発におけるキャリアパス             | 75 |

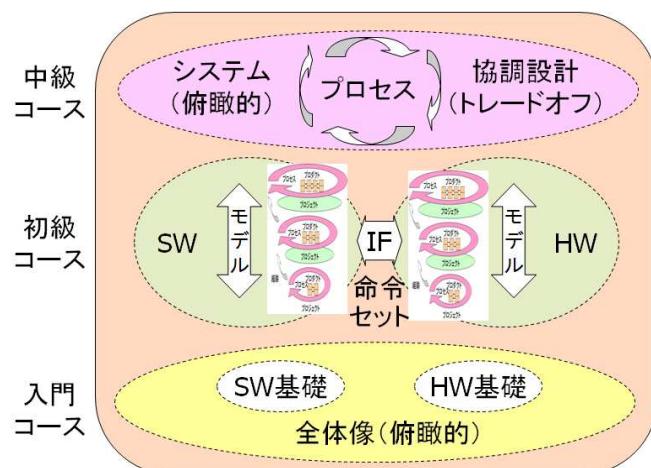

| 図 4.5  | カリキュラムの構成例                      | 76 |

| 図 4.6  | 高等教育機関でのカリキュラム体系                | 77 |

| 図 4.7  | 入門コースのカリキュラム例                   | 78 |

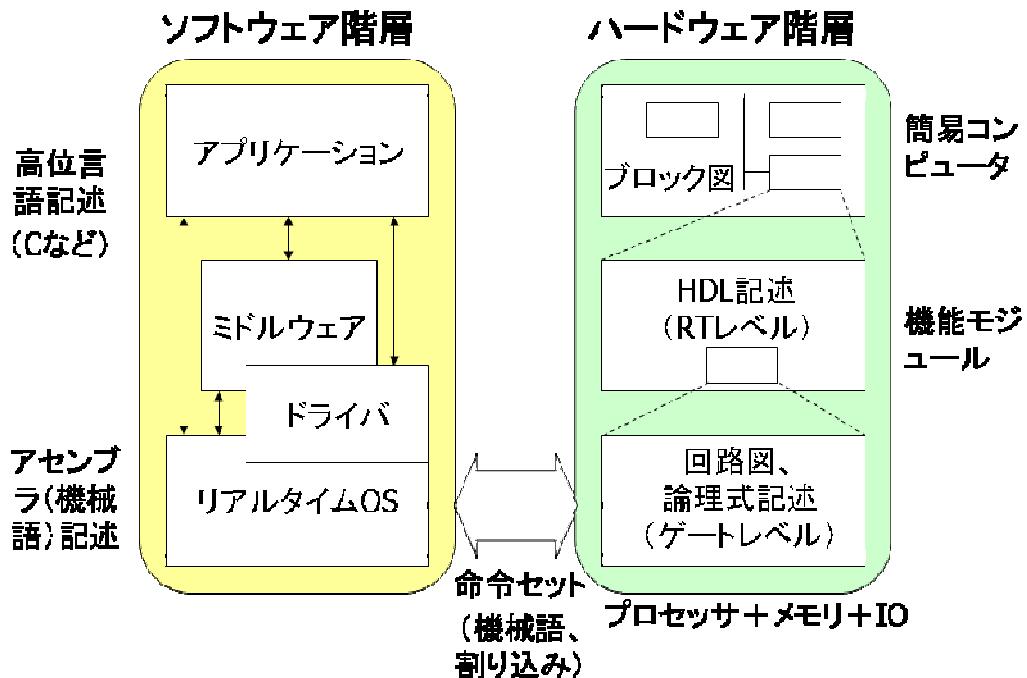

| 図 4.8  | 初級コースにおけるソフトウェアとハードウェアの関係       | 79 |

| 図 4.9  | マイクロカーネル制作コースのカリキュラム例           | 80 |

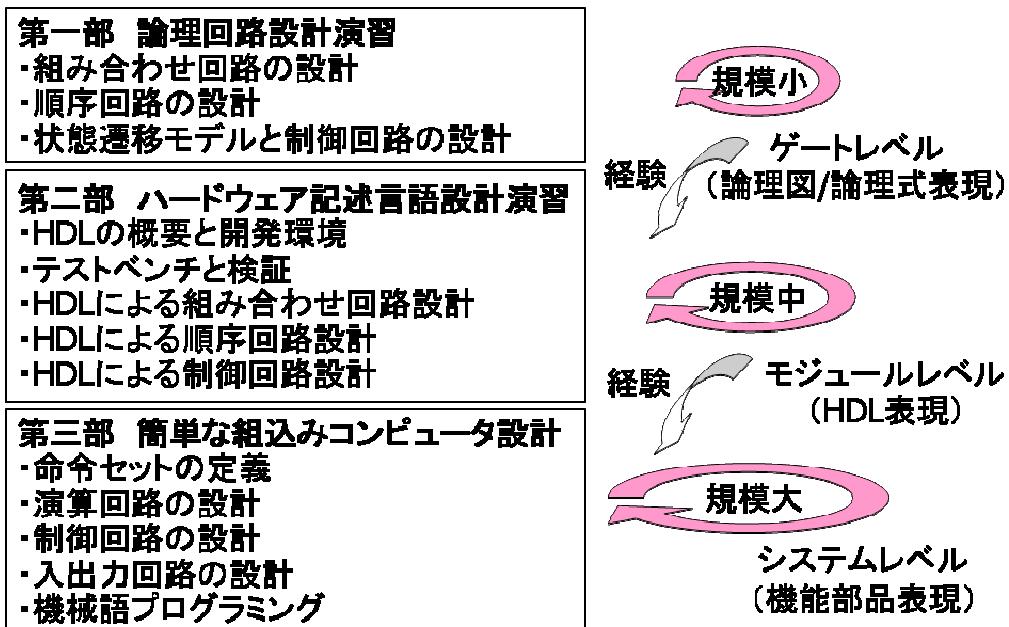

| 図 4.10 | コンピュータ工学演習のカリキュラム例              | 81 |

| 図 4.11 | コンピュータアーキテクチャ講義のカリキュラム例         | 82 |

| 図 4.12 | コンピュータアーキテクチャ演習のカリキュラム例         | 83 |

## 概要

1990 年代後半から 2000 年代にかけて、半導体技術の進歩とデジタル化の進展によりコンピュータの高性能化・低価格化・低消費電力化が進み、あらゆる分野の電子機器や制御機器にコンピュータ機能が組み込まれて製品が実現されるようになってきた。このように、コンピュータ機能を組み込んで実現される電子機器や制御機器は総称して「組込みシステム」と呼ばれる。

組込みシステムは応用分野ごとに性能・コスト・納期・消費電力などに関して最適なバランスになるようにハードウェアとソフトウェアによる協調設計（コデザイン）により実現される。ハードウェアは半導体の進歩で 1 チップのシステム LSI で実現されるようになり、組込みソフトウェアと組み合わせて事前に検証をしっかり行なうことが必要となってきた。また、組込みシステムは時代の進展とともにいろいろな機能をハードウェアとソフトウェアで積み重ねて大規模化・複雑化した複合システムであり、内部はますますブラックボックス化してきている。

競争が激しい最先端の分野では、独創的なアイデアを含んだ新しい組込みシステム製品の開発が求められており、ニーズを満たし不具合のない組込みシステムを如何に短期間で実現するかが重要になってきている。このような組込みシステムの開発における問題点を分析してみると大きく設計、検証と技術者育成の 3 つの課題に分類できる。

設計については、再利用可能な設計資産（IP）の活用、IP の搭載を容易にするプラットフォームベース設計の採用や、抽象度の高い表現ができる高位言語の採用と高位合成ツールの利用により、設計の生産性向上と品質向上などが実現されつつある。

検証については、独創的なアイデアがニーズを満たしているかを評価したり、設計の不具合を取り除くために、システム全体を繰り返し動作させてみる必要があり、如何に効率良く評価していくかが大きな課題となっている。設計の上流ステージでのシステム機能を高位言語で記述した動作モデルによる評価・検証、その後のアーキテクチャ設計ステージでのハードウェアとソフトウェアによる協調検証、設計の下流にあたる実機に近い動作環境ステージでの人間の五感による評価・検証によって問題ないことが確認されてはじめてシステム LSI のモノづくりに入ることができる。

従来のやり方では、各設計ステージにおいて、設計モデル（コンピュータで実行できるように表現した設計対象）の抽象度に応じた検証環境を使ってバラバラに評価が行なわれてきた。そのため、設計の上流から下流まで効率良く検証を行なうことができなかつた。また、ハードウェアとソフトウェアによる協調検証が必要になることから、そのインターフェースを各検証ステージでどのように実現するかも課題であった。

本研究では、組込みシステム開発における上流でのシステムレベルシミュレーションによる検証ステージから、下流の実機に近い環境での検証ステージまで、検証環境の統合と共通テストベンチの適用、および、コンポーネント論理バスアーキテクチャによるハードウェアとソフトウェアのインターフェースの統一により、階層的に効率良く繰り返し検証を行うトップダウン協調検証手法を提案する。トップダウン協調検証手法をマルチメディア系の2つの事例に適用し、各検証ステージにおいて実用レベルの性能で実行し、階層的に効率よく繰り返し検証できた成果を報告する。

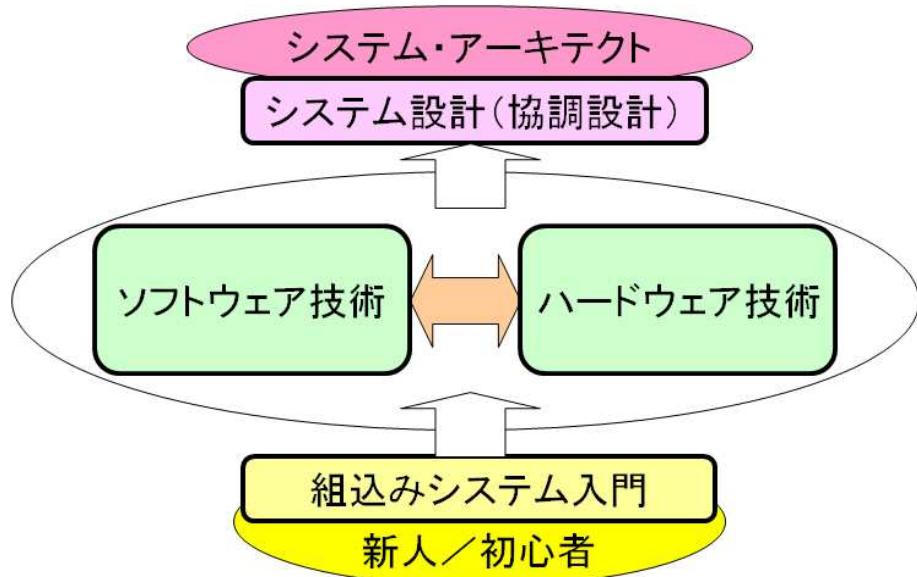

技術者育成においては、最先端の組込みシステムの新規開発で、性能・コスト・消費電力などの目標を満足できるように、ハードウェアとソフトウェアの協調設計により、最適な分担を実現するシステムアーキテクトの育成が求められている。既に、組込みシステム分野では、システムLSI開発の立場からのハードウェアとソフトウェアを含めた技術者の育成や、組込みソフトウェアに重点をおいた技術者の育成が行われているが、組込みシステム開発の課題を踏まえた技術者育成の取り組みも必要であると考えられる。

本研究では、組込みシステム開発の課題の分析や経験から抽出した「全体を俯瞰しながら基礎から応用へのスパイラルアップの取り組み」、「領域間のインターフェースの両面からの取り組み」、「ブラックボックス化した技術の階層的なモデリングの取り組み」、および、「ハードウェアとソフトウェアの最適な組み合わせを評価・選択する協調設計の取り組み」という4つのアプローチに基づいて、ハードウェアとソフトウェアの基本、およびインターフェースである命令セットを理解した上で、トレードオフを行えるシステムアーキテクトを育成するためのカリキュラムを提案する。実際にサイバー大学や岩手県立大学で実践した成果を報告する。

2017年現在のIoT時代を迎え、モノつくりの考え方が組込みシステム単体によるプロダクト指向から、ネットワークを介して、クラウドで評価・分析して付加価値を提供するサービス指向に変わっている。IoT時代では独創的なアイデアの創出が求められており、デザイン思考のアプローチが提案され、プロトタイピングによる評価検証による素早い繰り返しプロセスが提唱されている。本提案の「トップダウン協調検証手法」による効率の良い繰り返し検証のアプローチはIoT時代と言われる2017年の今の視点から見ても役に立つと考えられる。また、IoT時代の技術者育成について2017年現在取り組み中であるが、今回提案した4つのアプローチがクラウドコンピューティングと通信ネットワークを含めたIoTシステムの教育へ拡張するのに有効と考えている。

# 第1章 序論

本論文は、組込みシステムの開発における協調検証手法と技術者教育への適用実践についての研究に関してまとめたものである。

本章では、研究の背景、組込みシステム開発の課題、関連研究と本研究の位置づけ、研究の概要、および論文の構成について述べる。

## 1.1 研究の背景

1990年代後半から2000年代にかけて、半導体技術の進歩とデジタル化の進展によりコンピュータの高性能化・低価格化・低消費電力化が進み、あらゆる分野の電子機器や制御機器にコンピュータ機能が組み込まれて製品が実現されるようになってきた。このように、コンピュータ機能を組み込んで実現される電子機器や制御機器は総称して「組込みシステム」と呼ばれ、デジタル情報家電や通信機器、自動車制御機器など産業の基幹製品を占めるようになってきている。

組込みシステムはハードウェアとそれを動かすソフトウェアで構成されることから、応用分野の特性に応じてハードウェアとソフトウェアでどのように機能を分担して実現するかということが、製品の性能・コスト・納期・消費電力などを決める重要なファクタとなってきている。このように、製品にとって性能・コスト・納期・消費電力などが最適なバランスになるようにハードウェアとソフトウェアの分担を決めていく設計は協調設計（コデザイン）と呼ばれている。協調設計は製品の良し悪しを決める重要な位置づけにあり、製品全体に精通したシステムアーキテクトとよばれる人材が対応している。

初期（1990年以前）の組込みシステムでは、実現する機能もシンプルで、まずはハードウェアを開発してから、そのハードウェアの上でソフトウェアを開発するやり方が行われてきた。ソフトウェアの開発中に機能やハードウェアの不具合が発見された場合は、ハードウェアを比較的容易に改修することができ、ソフトウェアを変更することで、組込みシステム全体の開発への影響は必ずしも大きくならずに対応することができた。

しかし、その後のムーアの法則による半導体の集積度の向上により、組込みシステムのハードウェアの大部分を1チップで実現するシステムLSI時代（1990年代後半以降）を迎えるようになった。市場ニーズとのミスマッチやハードウェアとソフトウェアから構成される組込みシステムの不具合により、システムLSIを作り直すことになると膨大な対策費用と機会損失が発生してしまうことから、LSIを作成する前に評価や検証により問題点や不具合を取り除く必要がでてきた。

また、組込みシステムは、時代の進展とともにいろいろな機能をハードウェアとソフトウェアによる複合技術で積み重ねてきており、最先端の組込みシステムはますます複雑なシステムになってきている。このように技術の階層が深くなるに従い、その内部のブラックボックス化が進んできている。

本研究は、このような 1990 年代後半から 2000 年代における時代背景のもとに、組込みシステム開発を対象に行なわれたものである。しかし、2014 年頃からの IoT (Internet of Things : モノのインターネット) 時代を迎えるにつれて、モノつくりの考え方方が組込みシステム単体を販売するプロダクト指向から、組込みシステムをインターネットに接続してクラウドで評価・分析して付加価値を提供する IoT システムによるサービス指向に大きく変わろうとしている。このような状況を踏まえ、IoT 時代と言われる 2017 年の今の視点から、1990 年代後半から 2000 年代にかけての本研究の取り組みに対して評価・考察を加えている。

## 1.2 組込みシステム開発における課題

1990 年代後半から 2000 年代にかけて、競争が激しい最先端の組込みシステムとして、音や映像を扱うマルチメディア系やものの動きを制御する制御システム系の分野が注目されている。特に、独創的なアイデアを含んだ新製品の開発において、ニーズを満たし不具合のない組込みシステムを如何に短期間で実現するかが重要になってきている。このような組込みシステム開発の 1990 年代後半から 2000 年代における問題点を分析してみると大きく設計と検証と技術者育成の 3 つの課題に分類される。

設計については、再利用可能な設計資産 (IP) の活用、IP の搭載を容易にするプラットフォームベース設計の採用や、抽象度の高い表現ができる高位言語の採用と高位合成ツールの利用により、設計の生産性向上と品質向上など改善が既に進んできている。

それに対して、独創的なアイデアがニーズを満たしているかの評価や、ハードウェアとソフトウェアによる協調設計の不具合を取り除くための検証については、システム全体を動作させてみる必要があり、如何に効率良く実現するかが大きな課題となってきている。設計の上流ステージでシステム機能を高位言語で記述した動作モデルによる評価・検証、その後のアーキテクチャ設計ステージでハードウェアとソフトウェアによる協調検証、設計の下流にあたる実機に近い動作環境ステージでの人間の五感による評価・検証によって問題ないことが確認されてはじめてシステム LSI のモノづくりに入ることができる。従来は各ステージでそれぞればらばらな環境で評価・検証が行われてきたが、設計の上流から下流まで、繰り返しながら評価ができるトップダウン的な検証の取り組みが求められている。

また、複雑化してきた組込みシステムの新規開発において、応用製品として性能・コスト・消費電力などの目標を満足できるように、ハードウェアとソフトウェアによる最適な分担を実現する協調設計がますます重要になってきている。特に、独創的な機能を新たに開発する場合には、ブラックボックス化した内部を含めて、新しい視点でブレークスルーを図ることができるシステムアーキテクトの育成が大変重要になる。既に、組込みシステム分野では、組込みソフトウェアやシステム LSI 開発者の立場から、いろいろな取り組みが行われているが、組込みシステム開発の課題を踏まえて体系的な技術者育成の取り組みが求められている。

IoT 時代と呼ばれる 2017 年においては、モノつくりの対象がプロダクト指向の単体の組込みシステムから、組込みシステムと通信ネットワークとクラウドコンピューティングから構成される IoT システムというサービス指向の複合システム (SoS : System of Systems) に進化しつつある。このような IoT 時代は、第 4 次産業革命の到来と言われており、従来の延長線上とは異なる新しい取り組みが期待され、複雑なシステムの検証や付加価値創造に対応できる技術者育成が求められている。

### 1.3 関連研究と本研究の位置付け

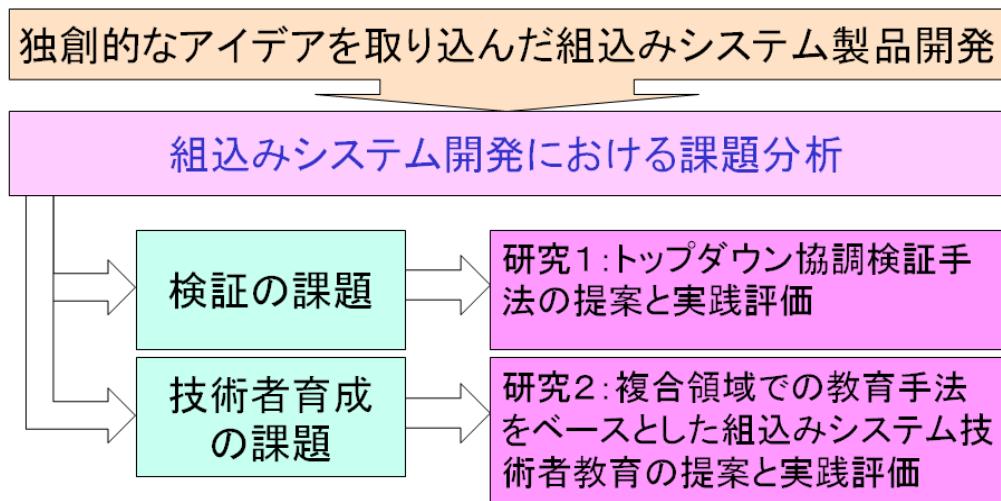

本研究の全体像と位置づけを図 1.1 に示す。独創的なアイデアを取り込んだ組込みシステム製品開発を対象に、組込みシステム開発における課題分析を行ない、抽出された 2 つ課題（「検証の課題」と「技術者育成の課題」）を解決するための 2 つの研究（「トップダウン協調検証手法の提案と実践評価」と「複合領域での教育手法をベースとした組込みシステム技術者教育の提案と実践評価」）を示している。

1990 年代後半から 2000 年代にかけて、独創的なアイデアを含んだ組込みシステムの開発では、設計の上流ステージでシステム機能を高位言語で記述した動作モデルによる評価・検証が行なわれてきた。続くアーキテクチャ設計のステージでは、ハードウェアとソフトウェアによる協調設計・協調検証が、設計の下流にあたる実機に近い動作環境ステージでは、人間の五感による評価・検証が、階層的に行なわれた。このようにシステム全体を動作させて評価する場合には、コンピュータ上のシミュレーションや実機に近い動作環境で対象システムを実際に動かして評価を行なう動的な検証手法が使われている。従来のやり方では、各設計ステージにおいて、設計モデル（コンピュータで実行できるよう表現した設計対象）の抽象度に応じた検証環境を使ってバラバラに評価が行なわれてきた。そのため、設計の上流から下流まで効率良く検証を行なうことができなかつた。また、ハードウェアとソフトウェアでの協調検証が対象となることから、ハードウェアとソフト

図 1.1 組込みシステム開発における課題分析と本研究の位置づけ

ウェアのインターフェースを設計の上位のステージから下位のステージまでどのように表現して検証を進めるかも重要な課題である。従来のやり方では、ある特定のステージにおけるインターフェース部分の合成や仮想CPUの命令セットとの協調シミュレーションについての取り組みが主であった。このため、設計の上流から下流にかけて、インターフェースの実現方法が異なると、変更が必要となり、検証作業の効率は良くなかった。本研究では、設計の最上流ステージから最下流の実機に近い動作環境ステージまで、繰り返し検証を行なうことができるよう、検証環境の統合と共にテストベンチの適用、および、ハードウェアとソフトウェアのインターフェースの統一を図ったトップダウン協調検証手法を提案し、マルチメディア系の映像圧縮伸張システムなどを題材にその有効性を評価した。

組込みシステム開発において、組込みシステムが大規模化・複雑化し、技術のブラックボックス化が進むにつれて、ハードウェアとソフトウェアによる協調設計や協調検証を行う技術者の育成が今まで以上に重要になってきており、いろいろな機関で取り組みが行なわれてきた。これらの取り組みでは、システム LSI 開発の立場からのハードウェアとソフトウェアを含めた技術者の育成や、組込みソフトウェアに重点をおいた技術者の育成がメインで、それぞれ大勢の技術者を育成し大きな成果を上げてきた。本研究では、組込みシステム開発における課題の分析や経験を踏まえて、協調設計・協調検証手法を実践できるシステムアーキテクトを育成するための複合領域での教育手法を提案し、それに基づいた組込みシステム技術者育成のカリキュラムを提案・実践し、その有効性を評価した。

なお、IoT 時代と言われる 2017 年の今の視点から見ると、今回の提案の考え方は、組込みシステム開発に留まらず、IoT システム開発における課題の解決のヒントになるとを考えている。

IoT 時代では独創的なアイデアの創出が求められており、デザイン思考[黒川 12]のアプローチが提案され、プロトタイピングによる評価検証による素早い繰り返しプロセスが提唱されているが、本提案の「トップダウン協調検証手法」のアプローチはその先駆けの取り組みともいえる。また、技術者育成における提案についても、IoT 時代のクラウドコンピューティングと通信ネットワークを含めた複合領域の教育へ拡張する場合のベースになると考えている。

## 1.4 研究の概要

以下に、2つの研究内容の概要を示す。

なお、本研究は、1990 年代後半から 2000 年代にかけての組込みシステムの検証の課題に関する解決策の提案であるが、IoT 時代と言われる 2017 年の今の視点から見た評価も加えている。

### (研究 1) トップダウン協調設計検証手法の提案と評価

組込みシステム開発における上流のシステムレベルシミュレーションの検証ステージから、ハードウェアとソフトウェアによる協調シミュレーションの検証ステージ、さらに下

流の実機に近い環境でのハードウェアとソフトウェアによる協調エミュレーションの検証ステージまで、検証環境の統合と共にテストベンチの適用、および、コンポーネント論理バスアーキテクチャによるハードウェアとソフトウェアのインターフェースの統一により、階層的に効率良く検証を行うトップダウン協調検証手法を提案する。

マルチメディア系の2つの事例に適用して評価を行なった。1つ目の事例では、九州大学安浦研究室との共同研究の成果物である自製の ASAP (Application Specific Adaptable Processor) [Sha96]を使った線描画システムを対象に、協調シミュレーションを適用した。2つ目の事例では、調達した 32 ビットプロセッサ (M32R/D) を使ったマルチメディア系の組込みシステム（映像圧縮処理システム）を対象に、上流のシステムレベルでのアルゴリズムの評価から、ハードウェアとソフトウェアによる協調シミュレーション、さらに下流の人間の感性による実機レベルの協調エミュレーションによる評価まで、階層的にトップダウン協調検証手法を適用した。各検証ステージにおいて実用レベルで検証することができ、階層的に効率よく繰り返し検証をすすめることができた[Seo97][YaM98][Seo98]。

#### (研究 2) 複合領域での教育手法をベースとした組込みシステム技術者教育の提案と実践評価

複合領域である組込みシステムの開発において協調設計手法の重要度が増す中で、協調設計を実践できるシステムアーキテクチャの育成が急務となってきた。本研究では、組込みシステム開発の課題の分析や経験から抽出した「全体を俯瞰しながら基礎から応用へのスパイラルアップの取り組み」、「領域間のインターフェースの両面からの取り組み」、「ブラックボックス化した技術の階層的なモデリングの取り組み」、および、「ハードウェアとソフトウェアの最適な組み合わせを評価・選択する協調設計の取り組み」という 4 つのアプローチに基づいて、ハードウェアとソフトウェアの基本、およびインターフェースである命令セットを理解した上で、トレードオフを行えるシステムアーキテクトを育成するためのカリキュラムを提案する。実際にサイバーハーバー大学や岩手県立大学で実践した成果を報告する[清尾 11A][吉田 11A]。

### 1.5 論文の構成

本論文は、以下の 5 章で構成される。なお、1990 年代後半から 2000 年代にかけての課題が対象であるが、IoT 時代と言われる 2017 年の今の視点からの評価も示している。

第 1 章では、本論文の研究の背景と組込みシステム開発の課題を述べ、課題解決のために行なった研究の概要について述べた。

第 2 章では、組込みシステムの開発における現状と課題について幅広い視点から整理を行う。特に独創的なアイデアを取り入れた組込みシステムを新たに開発する場合における、検証の課題、および、技術者育成の課題を示す。

第 3 章では、組込みシステムにおけるトップダウン協調設計検証手法を提案し、マルチメディア系組込みシステムなど 2 件の事例を対象にトップダウン協調検証手法を適用した

成果について考察する。

第4章では、複合領域である組込みシステムにおける協調設計を主導できる技術者（システムアーキテクト）の教育手法を提案し、それに基づいて作成したカリキュラムの概要と適用結果について考察する。

第5章では本研究の成果をまとめると共に、今後の課題と取り組みについて述べる。

## 第2章 組込みシステム開発の現状と課題

本章では、1990年代後半から2000年代にかけての最先端の組込みシステム開発における現状と課題を示す。組込みシステム開発において、ものづくりの成果物である応用目的に最適化された組込みシステム製品（プロダクト）、いろいろな技術を組み合わせた複雑系の組込みシステムを開発する手順（プロセス）、組込みシステムの開発を目標通りに進めていくプロジェクト、プロジェクトに参画する技術者（ピープル）に必要なスキルについて議論していく[Bra04]。

本章では、まず、組込みシステムとは何かを説明し、組込みシステム開発の発展の変遷、および、組込みシステム製品の技術成熟度の変遷について述べる。

その後、プロダクトの視点から、組込みシステムがいろいろな機能の集全体で複雑系のシステムであることを示す。組込みシステムの機能をハードウェア（ここではシステムLSI）とソフトウェア（組込みソフトウェア）の組み合わせで実現し、性能・コスト・消費電力など相反する要因をトレードオフしながら応用目的に最適な解をもとめていく協調設計（コーデザイン）について説明する。また、組込みシステム製品ではシリーズものとして、設計資産を有効に再利用しながら拡張開発などを行うことから、製品としてのライフサイクルの視点から考える必要がある。

次に、プロセスの視点から、組込みシステムの開発の流れを説明し、特にハードウェアとソフトウェアによる協調設計と協調検証について述べる。

さらに、プロジェクトの視点から、大規模化・複雑化が進む組込みシステムの開発ではプロジェクト管理が重要になってきたことを示す。

最後に、組込みシステム開発のプロジェクトに参画する技術者に求められるスキルについて述べる。

上記の4つの視点から述べた現状を踏まえて、組込みシステム開発における課題を、検証と人材育成の観点からまとめる。

なお、前述したようにIoT時代を迎え、組込みシステムを取り巻く状況が大きくかわりつつある。モノつくりの考え方方が組込みシステム単体を販売するプロダクト指向から、ネットワークで接続されたクラウドで評価・分析して付加価値を提供するサービス指向に大きく変ろうとしている。このような現状を踏まえて、IoT時代の組込みシステムの現状と課題についても言及する。

### 2.1 組込みシステムとは

各種の機械や機器に組み込まれて、それを制御するためのコンピュータシステムは、組込みシステムと呼ばれている。一般にPC（パソコン）は汎用のコンピュータシステムとして、組込みシステムと区別して考えられるが、PC内部のIO制御装置は専用のコンピュータが組み込まれた組込みシステムといえる。また、汎用のコンピュータであるPCを使っ

て実現した ATM (Automated Teller Machine : 自動出納機) は専用目的の組込みシステムといえる。このように、組込みシステムは、組み込まれるコンピュータが専用目的で使われるかどうかに依存していると考えられる。

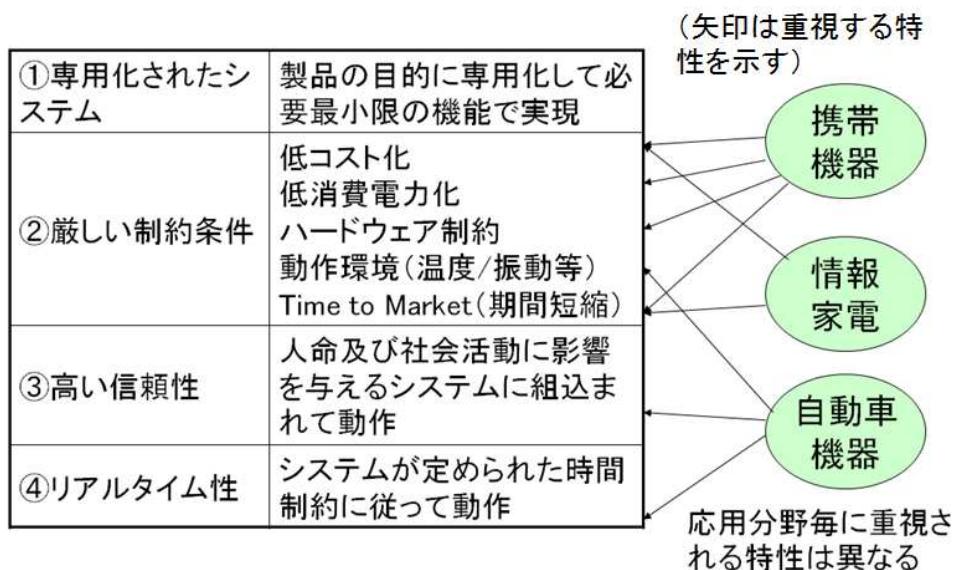

組込みシステムの主な特性をまとめると以下の通りである（図 2.1 参照）。

- ①製品の目的に最適化された専用化されたシステムである。新規開発の場合は、ハードウェアとソフトウェア、および開発環境の同時開発が必要となる。また、開発環境と実行環境が異なる。

- ②大きさや重さ、コスト、消費電力、開発期間などの厳しい制約条件を満足するように機能・性能などを実現する必要がある。

- ③人命や社会活動に影響を与えるシステムに組み込まれて使用される場合には、高い信頼性・安全性が求められる。

- ④定められた時間内に処理を終える必要がある場合には、リアルタイム性が要求される。

なお、組込みシステム製品の応用分野ごとに重視される特性は異なる。図 2.1 に示すように、携帯機器では矢印が示す低コスト化・低消費電力化・ハードウェア制約・期間短縮という厳しい制約条件が重視され、自動車機器では動作環境・高い信頼性・リアルタイム性が重視される。

また、組込みシステムはコンピュータ機能が組み込まれ、ハードウェアとソフトウェアという異なる技術を組み合わせて実現されることから、複合領域の世界といえる。組込みシステムの開発では、性能・コスト・消費電力等の相反する制約がある状態（この状態をトレードオフという）で、要求される機能を満足するようにハードウェアとソフトウェアで分担して実現することになる。

図 2.1 組込みシステムの主な特性

## 2.2 組込みシステム開発の変遷

情報通信社会の発展動向を図 2.2 に示す。ここでは、1960 年代から 2010 年代までの範囲を扱っている。この中で、組込みシステムはコンピュータの小型化・低コスト化・低消費電力化に伴い、あるゆる分野の機器で使われるようになってきている[Wol07] [Wol09]。2000 年には出荷されているコンピュータ（4 ビットから 64 ビットまで）の数の 98%が組込みシステムとして使われているといわれている[Ten00]。また、最近(2010 年以降)では、センサやアクチュエータを搭載した組込みシステムとネットワーク技術、クラウド技術を融合した IoT (Internet of Things) /M2M (Machine-to-Machine) が注目されている[清尾 13A][電気 16]。

組込みシステムの起源は定かではないが、1960 年代の汎用コンピュータの中央処理装置や入出力処理装置などは、制御回路の実現手段としてマイクロプログラム（ファームウェアとも呼ばれた）制御方式が使われていた。これらの制御回路は、専用目的の独自の命令セットを持ったコンピュータ機能であり、組込みシステムの草分けと言える。

炊飯器の例では、1980 年代にタイマー機能のついたマイコン制御の電気炊飯器が出現し、1990 年代には IH (Induction Heating) 式が登場し、好みの焼き加減などを調整できる多機能化が進んだ。2000 年代から高級志向できめ細かな制御によりおいしいご飯が炊けるようになってきている。

また、国内の携帯電話では 1987 年に最初に販売されたが当時の重量は 900g もあった。1990 年代半ばあたりでデジタル化が進み、半導体の高集積化・低消費電力化により重量が 200g を割り 100g に近くなるに従って急速に普及をはじめた。2000 年代に入ると第三世代

|                                               | 1960                                                | 1970                  | 1980                | 1990                     | 2000                           | 2010   |                                                                      |

|-----------------------------------------------|-----------------------------------------------------|-----------------------|---------------------|--------------------------|--------------------------------|--------|----------------------------------------------------------------------|

| 代表機種                                          | emainframe<br>(汎用コンピュータ)                            | ミニコンピュータ、オフィスコンピュータ   | パーソナルコンピュータ         | モバイル機器                   | モバイル機器                         | モバイル機器 | モバイル機器<br>クラウド・コンピューティング<br>ユビキタス⇒アンビエント⇒IoT<br>(Internet of Things) |

| 所有                                            | 会社・部門                                               | 課                     | 家                   | 人                        | 人                              | もの・こと  |                                                                      |

| H<br>W                                        | IC→LSI<br>(バイポーラ)                                   | LSI(TTL)              | VLSI、ULSI<br>(CMOS) | SoC(System on<br>a Chip) | SoC(System on<br>a Chip)       | マルチコア  |                                                                      |

|                                               | マイクロプロセッサ/マイクロコンピュータ<br>4ビット→8ビット→16ビット→32ビット→64ビット |                       |                     |                          |                                |        | 組込みシステムの拡大                                                           |

| S<br>W                                        | HWのおまけ<br>(付属品)                                     | HWと分離<br>(有償化)        | パッケージ               | コンテンツ                    | サービス                           |        |                                                                      |

| 特徴                                            | 性能重視<br>信頼性重視                                       | ダウンサイジング、コストパフォーマンス重視 | コスト重視<br>小型化        | インターネット<br>低消費電力         | サービス<br>仮想化<br>並列分散処理<br>安全・安心 |        |                                                                      |

| 価格                                            | 3億→3千万円                                             | -300万円-               | -30万-               | -3万円-                    | -1万円-                          |        |                                                                      |

| 利用形態: バッチ、TSS、オンライン、リアルタイム、分散、クライアント/サーバ、クラウド |                                                     |                       |                     |                          |                                |        |                                                                      |

図 2.2 情報通信社会の発展動向

が登場しインターネットとの融合が行われ、2007年以降はスマートフォンの普及が進んで、まさにPCの機能が手のひらで実現されるようになってきている。

自動車では、排ガス規制の関係で1990年代にエンジン制御の電子化がはじまり、その後2000年代にかけてエアバックやABS(Antilock Brake System)の電子化が進み、現在では車内の情報系(カーナビ、ETC: Electronic Toll Collectionなど)や画像認識などによる予防安全系の取り組みで進んでいる。2010年代の高級車では、100個程度のコンピュータ機能が搭載されていると云われている。

このように組込みシステムは、ムーアの法則による半導体の微細化とソフトウェア化によって、いろいろな電子機器をより洗練された知的なシステム(スマートシステム)へと変身させてきた。

特にIoT時代(当初はIoTの代わりにM2Mという用語が使われていた)を迎える組込みシステムはユーザに近いエッジ側のセンサとアクチュエータを搭載した機器やクラウドとの中継を行なうゲートウェイ機器として位置づけられている。組込みシステムは従来のプロダクトとしての価値提供から、クラウドコンピューティングと通信ネットワークにより接続され、収集したデータ(ビッグデータ)を評価・分析して、その結果を実世界にフィードバックすることで、ユーザに価値を提供するサービス指向に大きく変わろうとしている。IoT時代の組込みシステムについては、2.8節であらためて論じる。

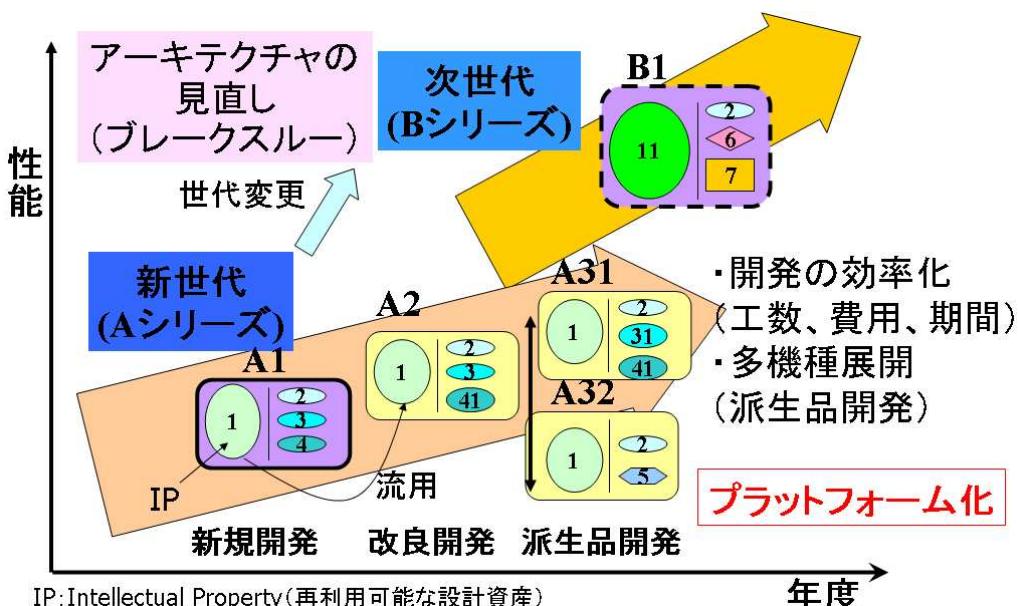

### 2.3 組込みシステム製品の技術成熟度の変遷

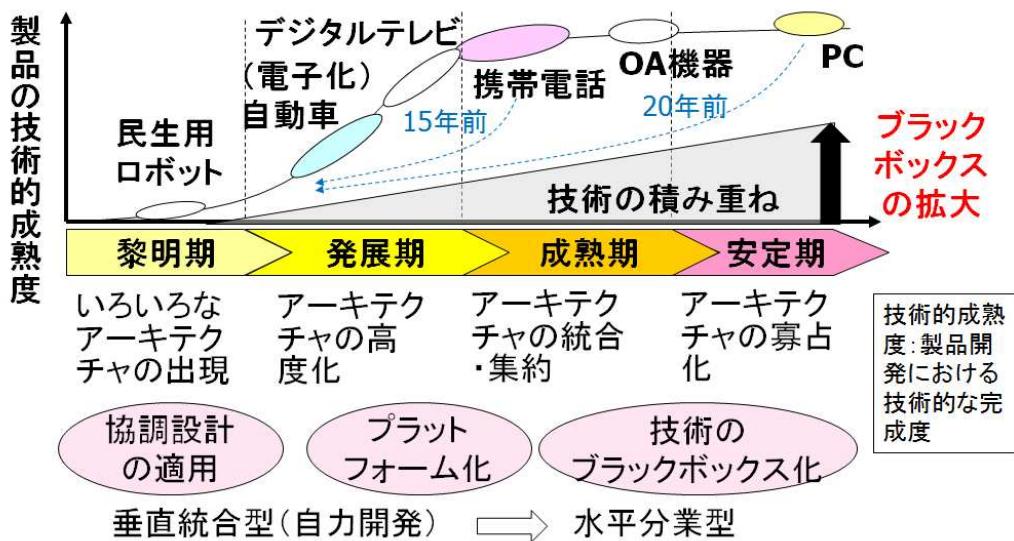

組込みシステム製品の実現方法(コンピューターアーキテクチャ)は、その応用分野の技術の成熟度に応じて変化していく。主な組込みシステム製品の技術的成熟度と実現方法の変遷のイメージ(2007年時点)を図2.3に示す。縦軸に製品に使われている技術の成熟度(ここでは技術の完成度の意味合い)を示し、横軸に成熟度が低い方から黎明期、発展期、成熟期、安定期の4つに期間に分けている。組込みシステムではないが、PCは約20年前(1980年後半)は発展期にあったが現在(2007年時点)は安定期にある。携帯電話は15年前(1990年前半)は発展期にあったが現在(2007年時点)は成熟期にあり、自動車の電子化は現在(2007年時点)発展期にあると位置付けられる。

技術が確立される黎明期には、新たな市場への参入を目指して、いろいろなオリジナリティを持ったアーキテクチャが出現するようになる。次の発展期には、市場の拡大を目指して、それぞれのアーキテクチャが高度化・洗練化されていく。この時期までは、一般に自社を中心に主要部分を自ら開発する垂直統合型に近いビジネスモデルになる。ハードウェアとソフトウェアによる協調設計によるトレードオフが最も行われる時期でもある。成熟期になると、市場での競争が激しくコスト競争となり、すべてを自社だけで対応できなくなってくる。ビジネスモデルも水平分業型に移行し、インターフェースの標準化とともに、効率よく機種展開するためにプラットフォーム化が進んでいく。安定期になると、コスト競争を含めビジネスに勝ち残ったアーキテクチャ(プラットフォーム)が業界標準として

図 2.3 組込みシステム製品の技術的成熟度の変遷

(図 2.3 は、産業構造審議会情報経済分科会、第 11 回情報サービス・ソフトウェア小委員会、「イノベーションの促進について」、2007 年[産業 07]より引用し筆者が改変)

固定化されるようになる。

組込みシステム製品は、黎明期、発展期、成熟期、安定期を通じて、いろいろな技術を積み重ねた結果として実現されており、その内部はブラックボックス化が拡大してきている。

黎明期から参画してきた技術者は、新しい技術を少しづつ積み上げながら、発展期・成熟期・安定期を乗り越えてきた場合が多く、ブラックボックス化された技術をしっかりと身に付けている。それに対して、後半から参画する若手技術者にとって、ブラックボックス化された技術の階層が深く、それを短時間で習得することは大変厳しい状況になってきている。

しかし、次世代を目指して大きなブレークスルーを図る場合には、このブラックボックス化した世界を如何に乗り越えていくかが重要になる。また、複雑化した組込みシステム製品の不具合の分析などでは、ブラックボックス化した内部の理解も必要となる。このように階層化された技術の内部を理解し、独創的な分野で活躍できる人材（システムアーキテクト）の育成が重要であり、それに必要な体系的な教育手法の充実が求められている。

## 2.4 組込みシステムのプロダクト

プロダクト（製品）に関して、以下の 4 つの視点から述べる。

- ① 組込みシステムは、AV (Audio Visual)・制御・通信などの応用技術分野を対象に、いろいろな異なる技術の組み合わせにより実現される多様な技術の集成体といえる。

- ② 組込みシステムは、ハードウェアとソフトウェアによる協調設計で実現されることから、コンピューターアーキテクチャの実現方法（ハードウェアとソフトウェアのインターフェース）は多様である。

- ③ 組込みシステムは、専用システムとして応用分野に特化した形で、トレードオフの関係にある性能・コスト・消費電力等の制約条件を満足するように、ハードウェアとソフトウェアの分担で実現する必要がある。

- ④ 組込みシステム製品の開発では、新規開発にかかる開発費用が膨大になることから、単に1回だけ開発するのではなく、製品開発のロードマップに沿って、改良開発や派生品開発を繰り返しおこない、製品としてのライフサイクル全体を通して費用を回収し利益を出せるように、IPによる設計資産の再利用を含めた効率の良い実現方法を考えることが必要である。

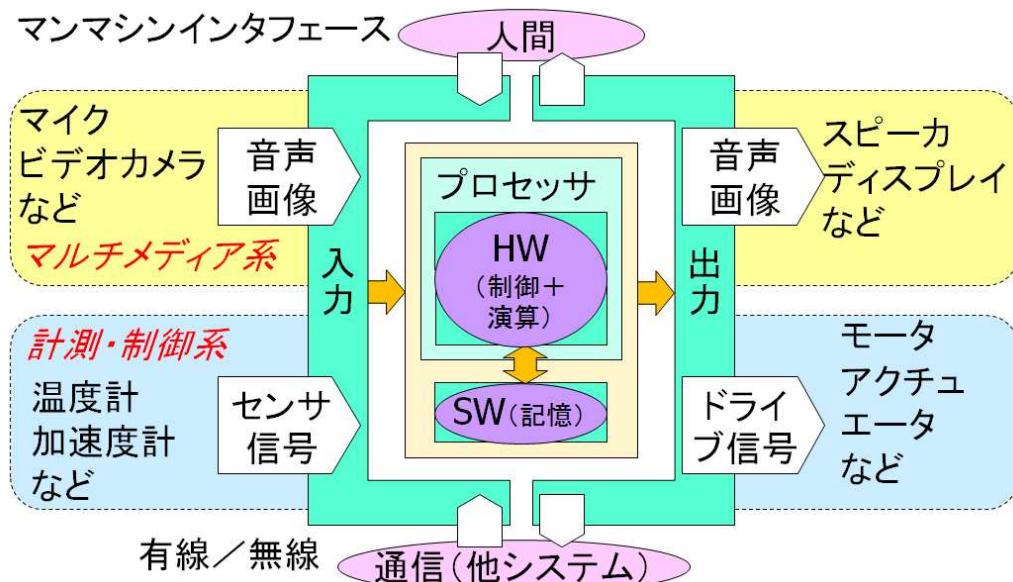

#### 2.4.1 組込みシステム製品は多様な技術の集成体

組込みシステムの概念的な構成を図2.4に示す。図2.4の中心部分がコンピュータシステムであり、ハードウェア（入力+出力+制御+演算+記憶）と記憶に格納されたソフトウェア（プログラムとデータ）で組込みシステムの機能を実現している。対象となる組込みシステムの要求仕様を満足するように、コスト・性能・消費電力などの相反する条件の中でトレードオフをおこない、ハードウェアとソフトウェアの分担を実現する協調設計が求められる。

マルチメディア系の処理では、マイクからの音声やカメラからの画像のアナログ入力信号をデジタルデータに変換してから、データ処理や圧縮伸張処理などの演算を行い、加工された音声や画像のデジタルデータをそれぞれアナログ信号に変換して、音声をスピーカ

図2.4 組込みシステムの概念的な構成

に、画像をディスプレイに出力することが行われる。

計測・制御系の処理では、温度や加速度などのセンサからのアナログ信号をデジタルデータに変換してから、制御アルゴリズムに基づいて演算を行い、制御されたデジタルデータをアナログ信号に変換して出力し、モータなどのアクチュエータを駆動することが行われる。一般に計測・制御系では、駆動した結果をセンサで測定し、アクチュエータを操作して目標の状態になるように制御が行われる。

また、組込みシステムは、専門家でない一般の人が取り扱うことから、人間にやさしい（使い勝手の良い）マンマシンインターフェースが必要となる。

さらに、組込みシステムが単独での使用から、有線や無線でネットワークに接続された形で利用されるようになってきており、他システムとの通信機能も必要とされている。

携帯電話の例をみると、マルチメディア系としてカメラ等による画像処理や音声処理機能が、計測・制御系として各種センサやバイブレータ用のモータなどが、人間とのインターフェースとなる高精度なディスプレイや、本来の機能である通信機能がそれぞれ盛り込まれて、ハードウェアとソフトウェアで分担して実現されている。

このように、組込みシステムは異なる技術を組み合わせて実現される複合領域のシステムであり、応用分野の基本技術を含めいろいろな異なる技術の理解・習得が必要となる。特に、ハードウェアとソフトウェアによる協調設計においては、トレードオフを行うのに必要な両方の技術の習得が必要になる。

また、組込みシステムの規模や適用範囲の急速な拡大により、複合領域としての複雑さがますます増大する中で、システム LSI の実現においてニーズを満足し、不具合を取り除くための検証が大きな課題である。特に、人間の目による画像評価や耳による音声評価が必要なマルチメディア系や、実際の動特性評価が必要な制御系の検証においては、実機レベルに近い環境での評価が必要である。

#### 2.4.2 ハードウェアとソフトウェアの協調設計

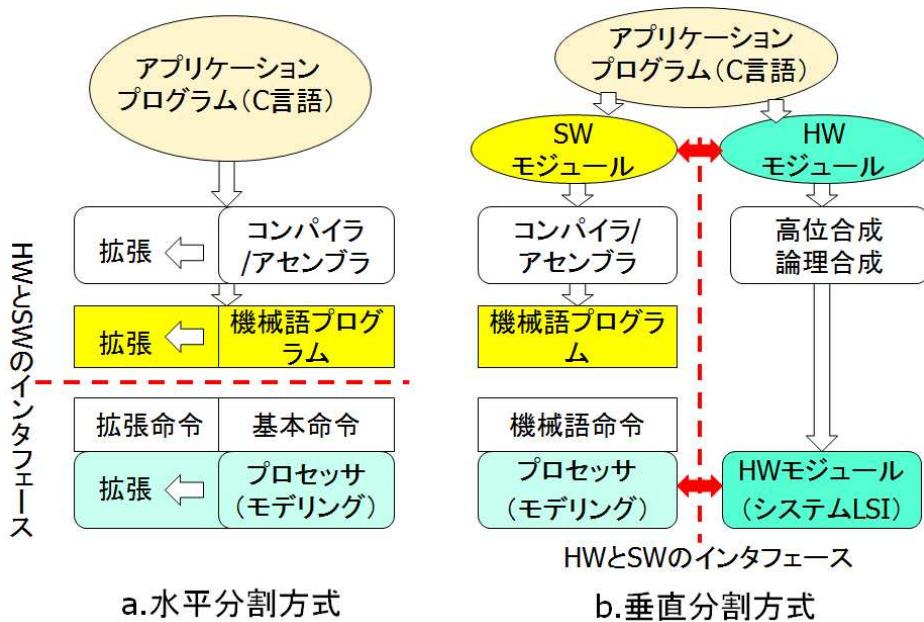

組込みシステムのアプリケーションプログラムを処理するコンピュータシステムの構成（コンピュータ・アーキテクチャ）を図 2.5 に示す。ハードウェアとソフトウェアの協調設計における機能分担の方式として、水平分割方式と垂直分割方式の 2 通りが存在する [Ern98]。

##### (1) 水平分割 (Horizontal Partitioning) 方式

アプリケーションプログラムの処理の目的（高速化、コードサイズの削減など）に適した命令セットをもつプロセッサを実現し、それに対応したコンパイラやシミュレータなどの開発環境を構築するものである。一般的には、基本部（固定部と可変部から構成）と拡張部から構成される。トップダウン協調設計システムの構築で開発した ASAP[Sha96]が該当する。また、九州大学の Soft-Core Processor and Valen-C[Yas95][Yas98]や大阪大学の

ASIP[今井 02]などがこれに相当する。ハードウェアとソフトウェアのインターフェースは、基本部+拡張部の命令セットになる。

## (2) 垂直分割 (Vertical Partitioning) 方式

アプリケーションプログラムを構成する機能モジュール群をハードウェアとソフトウェアで分担して実現する方法である。高位言語 (SystemC[Sys02]など、C 言語や C++ をベースとしたシステムの機能を記述する言語) で記述されたハードウェア部分は、高位合成により RTL (Register Transfer Level) の回路に変換される。また、ハードウェアとソフトウェアのインターフェース部分は、一般にバスを介した動作シーケンスにより実現され、インターフェース合成ツールまたは人手により、ソフトウェア側のドライバなどやハードウェア側のインターフェース回路などが生成される。

プロセッサ部分については、基本部のみの場合には一般に既存のプロセッサを調達して使うことが多く、プロセッサの設計・検証モデルを入手できるかは調達先に依存する。前述の水平分割方式で、アプリケーションを効率よく実現できるように命令を拡張する場合には、プロセッサ部分を自分で作成することになるので、プロセッサの設計・検証モデルは容易に入手することができる。

このように、組込みシステムはハードウェアとソフトウェアにより実現されることから、協調設計・協調検証において、ハードウェアとソフトウェアのインターフェース、および、プロセッサのモデリングをどのように取り扱うかが課題である。

図 2.5 組込みシステムのコンピュータ・システムの構成

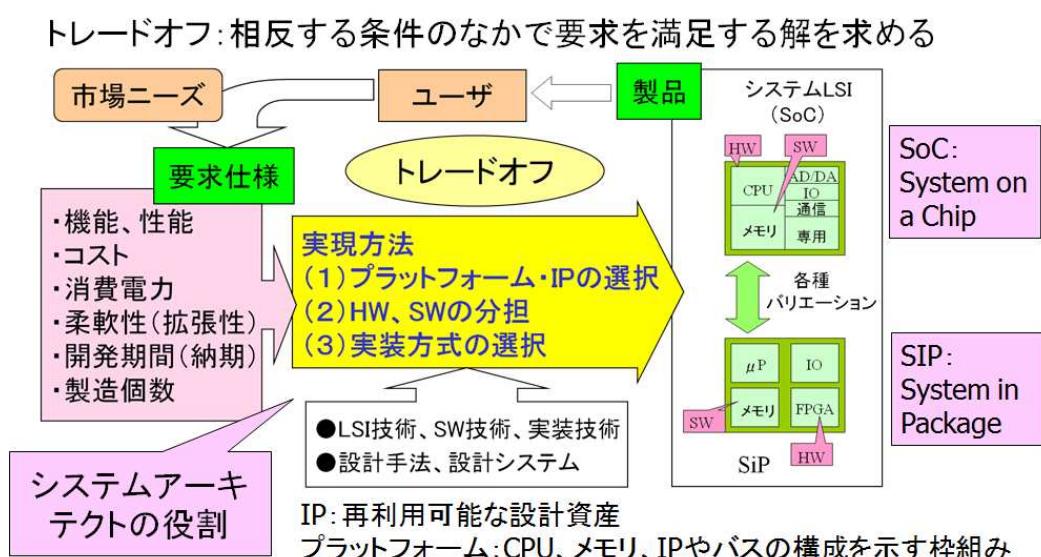

### 2.4.3 組込みシステムにおけるトレードオフ設計

組込みシステム製品の開発では、アーキテクチャ設計の段階において、いくつかの実現方法の選択肢の中から、いくつかの相反する項目を評価して、全体としてあらかじめ設定した条件を満足した解を求めるトレードオフ設計が行われる。組込みシステムにおけるトレードオフ設計の概要を図 2.6 に示す。この例では、トレードオフ項目として、性能・コスト・消費電力・柔軟性（変化への対応のしやすさ）などを取り上げる。以下、図 2.6 に示した 3 つの実現方法 ((1)、(2)、(3)) について述べる。

#### (1) プラットフォームと IP の選択

組込みシステム製品の特性に合うように、基本となるプロセッサやバスなどのハードウェア構成を定め、その上で動作する組込み OS などの基本的なソフトウェア構成を定めたものをプラットフォームと呼ぶ。なお、ハードウェア構成部分をハードウェア・プラットフォームと呼び、ソフトウェア構成部分をソフトウェア・プラットフォームと呼ぶ。

再利用可能な付加価値の高い設計資産のことを IP (Intellectual Property) と呼ぶ。設計生産性向上の観点から、IP の活用が注目されている。競争領域でない IP については、外部の IP ベンダーから調達することが多い。逆に、差異化を図るために新たに開発した機能を自らの IP として有効活用することにより、付加価値の高い製品開発を継続することが可能になる。

組込みシステム製品をシリーズ化して開発を行う場合には、開発コストの低減、開発期間の短縮などから、プラットフォームの選定と IP の活用が重要となる。

#### (2) ハードウェアとソフトウェアの分担

新規に開発するシステム機能の各動作部分をハードウェアまたはソフトウェアで実現

図 2.6 トレードオフ設計の概要

し、通信部分をハードウェアとソフトウェア、ハードウェア同士、ソフトウェア同士の間のインターフェースとして実現する。ハードウェアとソフトウェアのトレードオフにおける主な評価項目として、性能・コスト・消費電力・柔軟性などが使われる。コスト・柔軟性を優先するのであればソフトウェアで、性能・低消費電力を優先するのであればハードウェアで実現するのが一般的である。トレードオフの対象となる機能モジュールについて、それぞれハードウェアで実現する場合とソフトウェアで実現する場合について性能・コスト・消費電力の見積もりを行い、あらかじめ設定した条件を満足する組み合わせの中から総合的に判断して分担を決める。

図2.7に実行時間（性能の逆数）とコストによるトレードオフ評価の例を示す。Aはコスト最優先ですべてソフトウェアで実現した場合で、Cは性能最優先で大部分をハードウェアで実現した場合である。Bは、システム全体の性能評価でボトルネックとなっているソフトウェア部分をハードウェア化することにより、あらかじめ設定された最適解の候補エリアの中におさまった場合である。

### (3) ハードウェアの実装方式の選択

ハードウェアとして実現する場合、ASIC (Application Specific Integrated Circuit) または FPGA (Field Programmable Gate Array) で実現したり、SoC (System on a Chip) または SiP (System in Package) で実装したりする選択肢がある。開発の初期は、変更の可能性が高いことから、より柔軟性のある FPGA や SiP で実現し、システムが安定して量産化への移行段階ではコスト・パフォーマンスの高い ASIC や SoC 化に移行することも行われる。

実際の開発では、(1)(2)(3)のトレードオフは独立に行われるのではなく、並行して実施される。また、評価項目として、ここでは性能・コスト・消費電力・柔軟性をあげたが、実際の開発では開発工数（開発期間）、信頼性なども考慮して行われる。

図2.7 実行時間（性能の逆数）とコストによるトレードオフ評価の例

このトレードオフの結果が、その組込みシステムの価値を決めるところから、関連する技術をマスターし経験を踏まえて判断できるシステム・アーキテクトの育成が必要である。

また、設計の上流での見積りを支援する設計システムの充実も重要である。

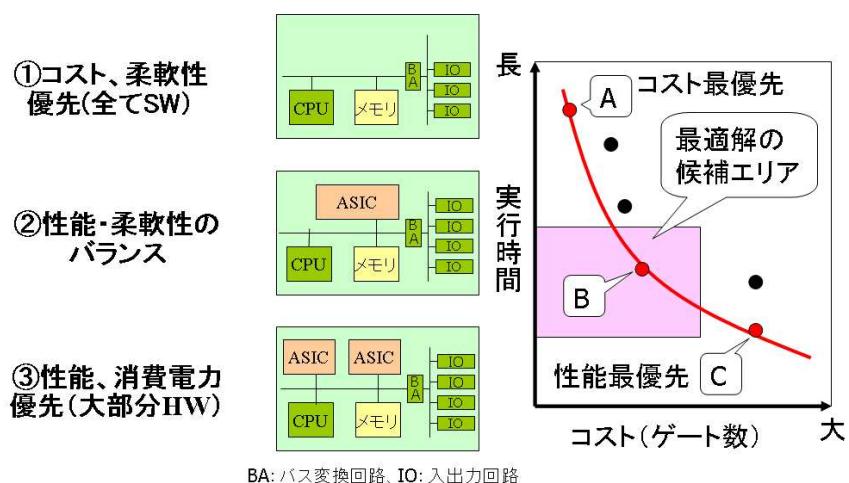

#### 2.4.4 組込みシステム製品のライフサイクル

組込みシステム製品の開発は、図 2.8 に示すように、1回だけの開発ではなく、製品展開のロードマップに基づいて、継続的にシリーズ化として開発が繰り返されていくのが一般的である。シリーズ内の製品展開においては、繰り返し行われる改良開発や派生品開発の効率化の観点から、ハードウェアとソフトウェアのプラットフォーム化と IP の活用が行われるようになってきた。図 2.8 の新世代である A シリーズの一連の開発において、最初の A1 の開発においてプラットフォームを確立し新規に開発した部分を IP 化（図 2.8 の A1 の 1~4）していく。次の開発 A2 では、4 の IP を改良して 41 とし、残りは以前の IP をそのまま活用して、短期に性能向上を狙う。さらに、IP の一部を高性能化したり、IP の一部を削除したりして、高機能品から低機能品までの派生品開発を繰り返し行うことによりシリーズ製品の寿命を延ばす取り組みが行われる。また、このようなシリーズ内の製品展開（A シリーズ）と並行して、技術的なブレークスルーを行い、次世代開発（B シリーズ）の立ち上げが行われていく。

組込みシステム製品のシリーズ開発は、図 2.9 の上側に示すように、最初の製品企画から、設計・試作・量産の開発サイクルによる何回かの製品展開を経て、最終的に開発終了・保守フェーズに入り、そのシリーズ製品の一生が終わることになる。このように組込みシステム製品のライフサイクルの観点から、効率の良い実現方法を考えることが重要である。

図 2.8 組込みシステム製品の開発ロードマップ

図 2.9 組込みシステム開発のライフサイクルと開発プロセス

開発における重要な管理項目である QCD (Quality、Cost、Delivery) の観点から開発プロセスやライフサイクルの関係を図 2.9 の下側に示す。

①の製品の品質については、顧客のニーズを満足しているかどうかの要求品質と設計が仕様どおりに作られているかどうかの設計品質と製品が不良なく作られているかの製造品質により決まる。特に独創的な製品開発のときは、ニーズを満足しているかの要求品質が特に重要となる。また、大規模化・複雑化が進むにつれ、設計品質の確保が難しくなり、検証手法の充実が必要である。

②の製品のコストについては、設計コストと製造コストから算出される。設計コストについては新規開発部分と再利用部分 (IP) に分けそれぞれの出荷個数を考慮して製品コストに反映する必要がある。出荷数が少ない場合にはコスト全体に占める設計コストの割合が高くなり、出荷数が多い場合には製造コストの占める割合が高くなるので、出荷数に応じて、適用する設計方法や実装方法を検討する必要がある。

③の製品の納期については、設計期間と製造期間から算出される。競争の激しい分野では、市場投入時期が遅れると売上機会 (先行利益) を逃してしまうことから、できるだけ短い期間で納期が遅れないように品質を確保した上で出荷する必要がある。大規模化・複雑化にともない、設計と検証の効率化 (生産性向上) が大きな課題である。

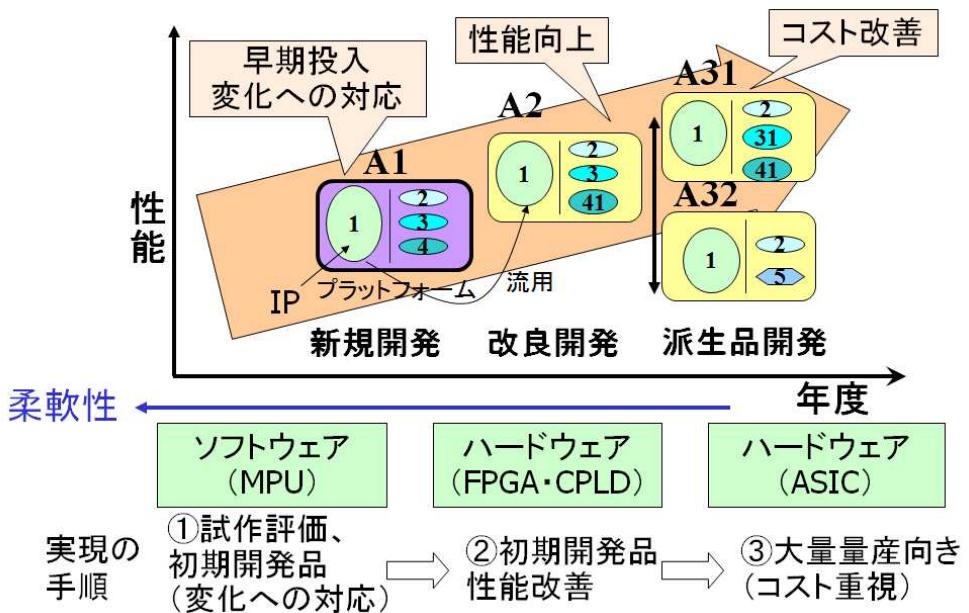

図 2.10 に組込みシステム製品のライフサイクルにおける実現方法の変化を示す。組込みシステム製品のライフサイクルにおいて、協調設計のトレードオフの判断基準が異なることにより、実現方法が異なってくる。①の新規開発時の試作評価や初期開発では、早期に

図 2.10 ライフサイクルにおける実現方法の変化

製品レベルの動作が必要であることから変化への対応が容易なソフトウェアで実現し、②の初期開発品の改良開発では仕様や設計品質が安定してきたので FPGA により性能向上をはかり、③の大量量産向けでは ASIC 化によるコスト削減を図るようなことが行われる。

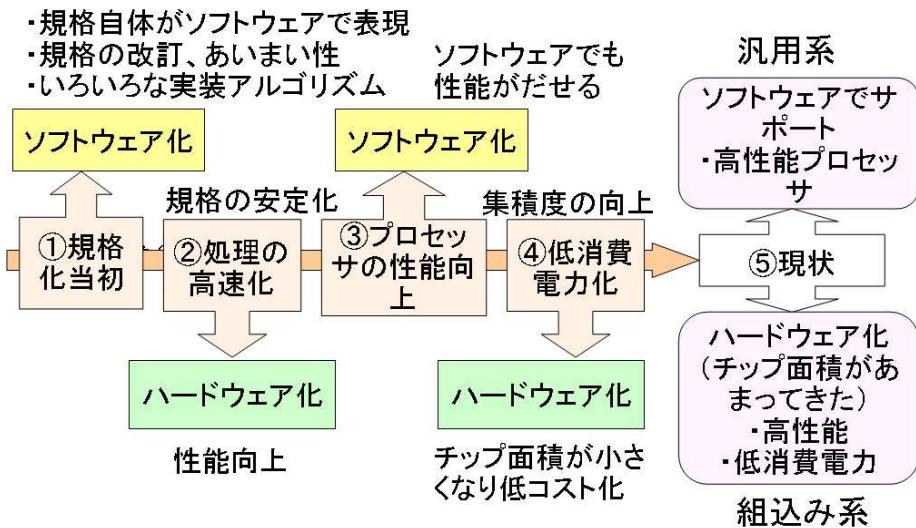

例として、静止画圧縮伸張アルゴリズム（国際標準規格）である JPEG について、ハードウェアとソフトウェアのトレードオフがどのように行われてきたかを図 2.11 に示す。

JPEG のような国際標準規格では、基本仕様のアルゴリズムが C 言語で記述（定義）されることが多い。

- ①規格が制定されたころは、まだ規格自体にあいまいなところがあったり、実装方法の経験が少ないとから性能を犠牲にしてソフトウェアで実現されることが多い。

- ②規格が安定し、実装方法もいろいろ研究されてくると、性能向上を実現するためにハードウェア化が行われるようになる。

- ③プロセッサの性能が向上すると、ソフトウェアでもかなり高速に処理できるようになり、ハードウェア化によるコストを削減するために、ソフトウェアで実現されるようになる。

- ④微細化が進み、チップ面積に余裕ができ、低消費電力が求められるようになると、ハードウェア化が行われるようになる。

- ⑤現状では、低消費電力化を求められる組込みシステムではハードウェアで実現され、プロセッサの性能が高い汎用系のシステムではソフトウェアで実現されている。

このように、同じ機能でも、適用する製品の特性やライフサイクルにおける状況に応じて、ハードウェアまたはソフトウェアで実現されることになる。このように、製品のライフサイクルにおいて、それぞれ適した実現方法がとれるように、製品のライフサイクル全体を見通して判断できるようになることが必要である。

図 2.11 JPEG (静止画圧縮伸張) の HW と SW のトレードオフ例

## 2.5 組込みシステムにおける開発プロセス

組込みシステムの大部分の機能をシステム LSI とその上で動作する組込みソフトウェアで実現するためには、設計の上流で品質の作り込みを行うと共に、LSI 製造までに不具合を取り除くようにシステムレベルで評価・検証を行う必要がある。しかも、競争の激しい領域ではタイムリーな開発が必要である。従来のようなハードウェアとソフトウェアの分担開発や、LSI 部品を開発するというアプローチでは対応できず、システム全体を見通した効率の良い設計手法と検証手法を確立する必要がある。組込みシステムが、大規模・複雑になるに従い、単にプロダクト（ハードウェアとソフトウェア）の品質だけではなく、要求分析からシステム設計、ハードウェア/ソフトウェア設計、ハードウェア/ソフトウェア実装、テスト、保守までの開発プロセスが正しく行われることが重要となる。

独立行政法人 情報処理推進機構 (IPA) のソフトウェアエンジニアリングセンター (SEC) がまとめた「組込みソフトウェア向け開発プロセス」[情報 07B]を参考に、ハードウェア向けの開発プロセスを加えた組込みシステムの開発プロセスの構成を図 2.12 に示す。

従来のまだ規模が小さかった組込みシステムの開発においては、ベテラン技術者が経験に基づいて、応用分野に適したプロセッサ（マイクロコンピュータ）を選定し、ハードウェア設計者が論理設計や基板設計を行い、その仕様に基づいてソフトウェア技術者が組込みソフトウェアを開発してきた。後で不具合がみつかれば、基板を修正したり、ソフトウェアを修正することで、なんとか対応ができた。

しかし、半導体の進歩によりシステム LSI 化が進み、対象規模が拡大し、複雑さが増大するに従い、開発の後半での変更は品質・コスト・納期などの観点から不可能になってきている。このような課題を解決し、付加価値の高い製品を実現するためには、開発の上流

図 2.12 組込みシステムにおける開発プロセス

(IPA の「組込みソフトウェア向け開発プロセス」にハードウェア向け開発プロセスを追加)

のシステムレベル設計において、要求仕様をシステム仕様に落とし込み、システム仕様をハードウェアとソフトウェアで最適に分担して設計・評価を行う協調設計・協調検証が重要となる。

既に、このシステムレベル設計・協調設計・協調検証の分野では、1990 年代の前半から、多くの研究や報告が行われている。協調設計関連として、協調設計を実現する方法として水平分割方式と垂直分割方式があり、前者ではアプリケーションに最適なプロセッサの生成方法とそれに必要なコンパイラの自動生成の研究が、後者ではハードウェアとソフトウェアのインターフェースとプロセッサのモデリングについての研究などが行なわれている [Tho93] [Mic94] [Chi94] [Sat94] [Wol94] [Mic95] [今井 95] [安浦 95] [宮崎 95] [Ada96] [Mic96] [Mic97] [Sta97] [Ern98] [今井 98] [Mic01] [Vah03] [Wol03] [Mit09] [Sch10]。協調検証関連として、プロセッサの検証モデルと周辺のハードウェアの検証モデルを連動させてシミュレーションを行なう方法がいろいろ研究されている [Row94] [Gho95] [Pas97] [野々 04]。協調合成・高位合成関連として、ハードウェアとソフトウェアのインターフェース部分のソフトウェアドライバとハードウェアインターフェース回路の合成方法の研究が行なわれている [Gup93] [Hua95]。システムレベル設計関連として、協調設計・協調検証・協調合成を含めたシステムレベルでの取り組みが報告されている [Bal03] [Hen03] [Lee03] [今井 04] [黒坂 04A] [黒坂 04B]、

開発プロセスにおける協調設計・協調検証の位置づけを図 2.13 に示す。

要求分析では、市場ニーズの要求分析から要求仕様をまとめる。要求仕様については、従来は文章で表現されていたが、最近は UML (Unified Modeling Language) による記述

図 2.13 開発プロセスにおける協調設計・協調検証の位置づけ

も行われるようになってきている。

システム設計では、その要求仕様を満足するように、システムを実現するためのシステム仕様をまとめ。システム仕様の記述には、SystemC や C 言語などの高位言語が使われる。この段階では、まだハードウェアとソフトウェアの分担を意識せずに、主にアルゴリズムの最適な実現方法を評価・検証しながら、いくつかの動作モジュールとそれらの間の通信による解を求ることになる。また、Matlab などのモデル記述言語を使って、設計対象（コントローラモデル）とそれにより制御される機器や環境（プラントモデル）をモデル化して、システムの系全体を評価しながら、システム設計を行うモデルベース設計も行われている。この領域は、制御技術分野も含んだ世界であり、広義の協調設計分野といえる [Koi95]。

アーキテクチャ設計では、いろいろな実現方法の選択肢の中から、相反する要件（性能、コスト、消費電力、柔軟性、開発期間など）を評価しながら、対象製品に最適な解を求める設計探索が行われる。

最初に、システム機能としてどの程度のデータ演算量やトラフィック量が必要かを解析するプロファイリングが行われる。このプロファイリング結果に基づいて、性能・コスト・消費電力等の制約条件を満足するように、ハードウェアとソフトウェアの分担を実現する協調設計が行われる。

まず、ベースとなるプラットフォーム（搭載するプロセッサ・メモリ・バス等）を選択する。次いで、動作モジュールをハードウェア（IP/専用回路）またはソフトウェアに割り当てる。また、動作モジュール間の通信部分については、ハードウェアとソフトウェアとのインターフェース回路やハードウェアとの問答を行うドライバ・ソフトウェアに置き換え

ていく。

ハードウェア部分については高位合成により RT レベルに変換され、ソフトウェア部分については高位言語プログラムに変換（ソフトウェア合成）される。インターフェース部分については、インターフェース合成により自動的に変換することも可能になってきている。これらを総称して、協調合成ともいわれる[Mic95]。

また、システム設計では、高位言語でモデル化された内容が仕様どおりであるかをシステムレベルシミュレーションにより確認が行われる。アーキテクチャ設計では、ハードウェアとソフトウェアに分割されたモデルを組み合わせた協調検証が行われる。この段階の協調検証はシミュレーションベースで実行される協調シミュレーションで、分割されたハードウェアモデルと使用するプロセッサモデルの抽象度に応じて、いろいろな実現方法が存在する。

アーキテクチャ設計後は、ハードウェアとソフトウェアの設計が並行して実施されるので、両者を組み合わせて全体として正しく動作するかの協調検証が行われる。この段階の協調検証には、シミュレーションベースでおこなう協調シミュレーションとエミュレータによる協調エミュレーションがある。協調シミュレーションでは、実際のプロセッサがまだ存在しないときに、プロセッサをモデル化して、ソフトウェアの検証に使うことが多い。協調エミュレーションでは、実機に近い環境で応用ソフトウェアを含めた高速検証ができ、人間の感性による評価が可能となる。また、顧客に製品に近い動作を示すこともできる。

LSI の設計規模拡大に対して、プラットフォームや IP を再利用することにより、設計工数の増加を抑えることができるが、検証については再利用したところも含めて全体を動作させる必要があるため、検証規模や検証工数の増加を抑えることが難しい。また、システム LSI 化により、不具合は大きな影響を与えることから、検証環境の充実は非常に重要である。

## 2.6 組込みシステム製品開発におけるプロジェクト

開発プロジェクトの規模が大きくなるほど、QCD の目標を実現するために、PDCA (Plan、Do、Check、Act) のサイクルをまわし、プロジェクトをマネジメントしていくことが重要となる。多くの組込みシステム製品の開発は、プロジェクトリーダー、システムアーキテクト、ハードウェア技術者やソフトウェア技術者を含む関係者（ステークホルダ）によるプロジェクト体制で行われる。組込みシステムの開発プロジェクトでは、ハードウェア技術者とソフトウェア技術者が、お互いのインターフェースを誤解のないように理解して、トラブルなく目標を達成することが求められている。

経産省と IPA が共同で行なった 2007 年版 組込みソフトウェア産業実態調査[経産 07]によれば、組込みシステムの開発計画に対する開発プロジェクトの結果は、図 2.14 のような状況であったと報告されている。機能・性能の面では 19%が目標を未達成であるのに対し

て、品質 (Q) 面では 27% が、コスト (C) 面では 59% が、納期 (D) 面では 61% が目標を未達成となっており、特に納期遅れが問題である。競争の激しい分野では、納期の遅れが損益に大きく影響するので、不具合やトラブルにより開発期間が延びないように、プロジェクトをマネジメントして行くことが重要である。

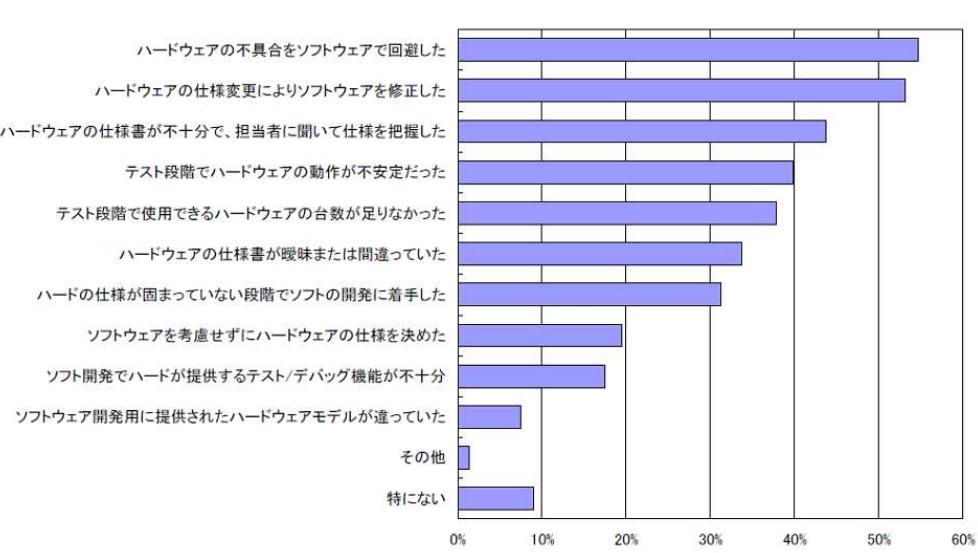

また、組込みソフトウェアの開発でハードウェアに起因して直面した課題について図 2.15 に示す。組込みシステムの開発においては、ハードウェアとソフトウェアの分担とその間のインターフェース仕様を決める協調設計が重要であり、ハードウェア部門とソフトウェア部門が連携して取り組むことが必要であることを示している。

図 2.14 開発計画に対するプロジェクトの結果

図 2.15 ハードウェアに起因して直面した課題

図 2.16 プロジェクトマネジメントの概要

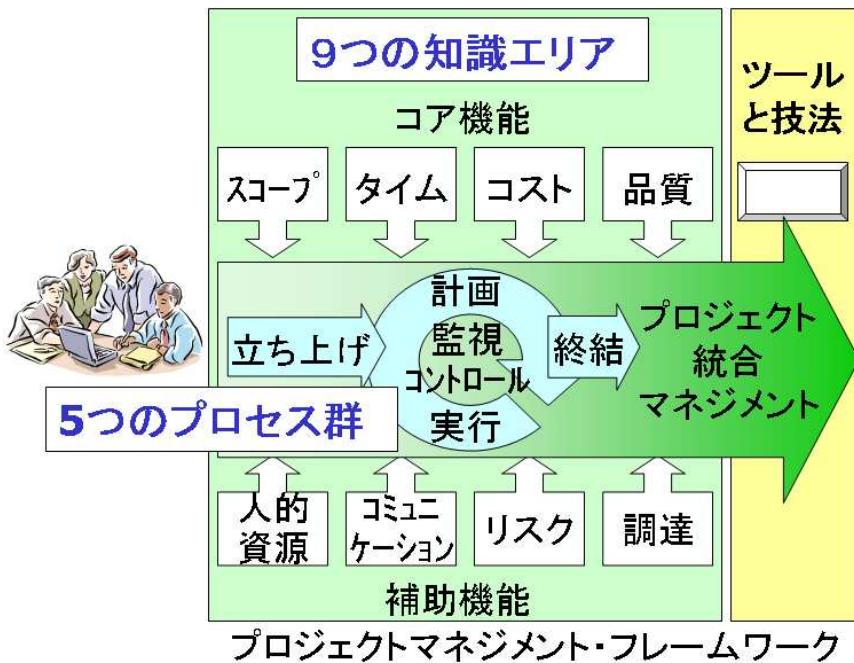

組込みシステムの大規模な開発プロジェクトの推進においては、図 2.16 に示すような PMBOK (Project Management Body Of Knowledge) に基づいた取り組みが必要である。2000 年代の PMBOK は、9 つの知識エリアと 5 つのプロセス群とツールと技法から構成されている。9 つの知識エリアは、プロジェクトを進める上で必須の機能（コア機能）であるスコープ・タイム・コスト・品質と、補助機能である人的資源・コミュニケーション・リスク・調達と、統合から構成されている（なお、2013 年の第 5 版でステークホルダーが追加されて 10 の知識エリアとなっている）。組込みシステム製品のユーザを含む関係者（ステークホルダー）の要件や期待に応えるように、プロジェクトの対象範囲（スコープ）を明確に定義し、目標とする品質 (Q) ・コスト (C) ・タイム (納期 : D) の実現を目指して、人的資源・コミュニケーション・リスク・調達および統合のマネジメントを計画的に行い、立ち上げ→計画→監視・コントロール→終結の 5 つのプロセス群を回していくことが必要になる。

複合領域にある組込みシステムの開発は、大規模化・複雑化が進み、図 2.14 に示したように、目標通りに開発を完了することが難しい面があるが、プロジェクトを正しく進めるためのスキルや仕組みが不足している場合も多い。プロジェクトマネジメントに関するスキルに関しては、PMBOK のような知識レベルでの学習だけでは十分でなく、実際のプロジェクトを模擬した PBL (Project Based Learning, Problem Based Learning) 型の演習を通じて経験しながら修得していくことが必要になっている。PBL については、チームにより目標を達成することから、コミュニケーション力の育成などの基本的な能力育成もかねて、高等教育機関や企業研修の場で行われるようになり、成果を上げてきている。なお、

負荷が特定の人に偏ったり、チームの編成の仕方や評価方法についていろいろな課題が指摘されている。

## 2.7 組込みシステムの開発に必要なスキル

プロジェクトを構成する技術者は、その担当職務に必要となる技術やスキルを習得しておく必要がある。組込みソフトウェア開発力の強化の一貫として、経産省・IPAにより制定された組込み技術スキル標準(ETSS、Embedded Technology Skill Standard) [情報 09A]をベースに考える。ETSS は、IPA の SECにおいて 2005 年に策定され、スキル標準、キャリア標準、教育研修標準から構成されている。

組込みシステム技術者に必要な技術やスキルは、多様であることから、体系的な教育カリキュラムを設定して教育を行う必要がある。特に、付加価値の高い競争力のある組込みシステム製品の実現のために、ハードウェアとソフトウェアに精通したシステムアーキテクトの育成が求められている。

ユーザが満足する組込みシステム製品を開発するためには、開発に必要な業務を担当するそれぞれの技術者（ピープル）がそれぞれの立場・役割（職務）で、対象となる組込みシステム製品（プロダクト）を高い品質で作り込み、正しい組込みシステム開発プロセスをまわし、目標とする QCD を達成するようにプロジェクトを動かしていく必要がある。このように組込みシステム技術者が振舞うためには、それぞれの職務にふさわしいスキルセットを適切なレベルで保持して、活用することが必要になる。

組込みシステムが大規模化・複雑化するに従い、設計生産性の向上や品質向上が求められるようになり、従来の自己流ではなく、標準的なスキル体系に基づいた技術者育成が求められている。

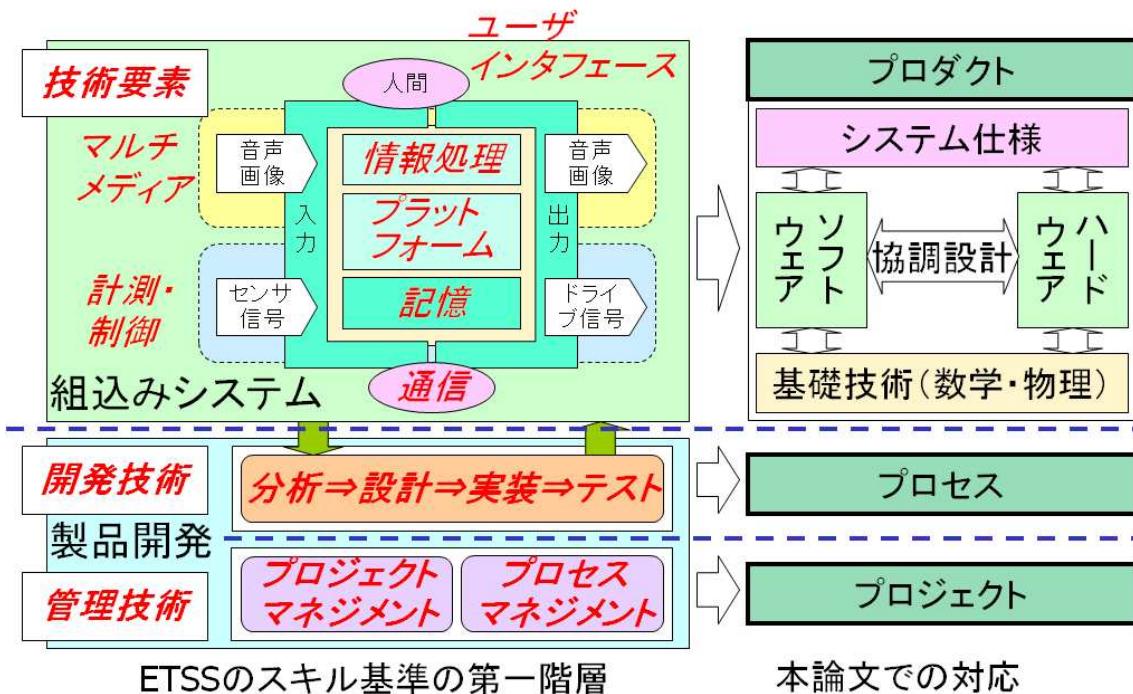

ETSS のスキル標準のフレームワークでは、必要とするスキル群を 3 つのスキルカテゴリ（技術要素、開発技術、管理技術）に分類し、スキル粒度として最上位の抽象的な第一階層からより詳細な第三階層まで階層的に展開し、最下層のスキルに対して必要なスキルレベル（初級、中級、上級、最上級）を設定している。

組込みスキル標準 ETSS をベースに組込みシステム開発に必要となるスキル体系（ETSS スキル基準第一階層）をまとめたものを図 2.17 に示す。ETSS は 3 つのスキルカテゴリである技術要素、開発技術、管理技術から構成されている。ここで、技術要素がプロダクトに、開発技術がプロセスに、管理技術がプロジェクトに対応している。

ETSS では、技術要素として、以下に示すように 7 つの第 1 階層（コロンの後に第 2 階層を示す）について例示している。

- ① 通信：有線、無線、放送、インターネット

- ② 情報処理：情報入力、セキュリティ、データ処理、情報出力

- ③ マルチメディア：音声、静止画、動画、統合

- ④ ユーザインターフェース：人間系入力、人間系出力

図 2.17 組込みシステム開発に必要なスキル体系 (ETSS スキル基準第一階層)

- ⑤ 記憶（ストレージ）：メディア、インターフェース、ファイルシステム

- ⑥ 計測・制御：理化学系入力、計測・制御処理、理化学系出力

- ⑦ プラットフォーム：プロセッサ、基本ソフトウェア、支援機能

ETSS は、組込みソフトウェア技術者向けを想定しているが、組込みシステムとしての要求分析からシステム設計の上流も対象にしていることから、技術要素（プロダクト）はそのまま組込みシステム技術者にも適用可能であると考える。

開発技術（プロセス）については、ハードウェアとソフトウェアでは大きく異なることから、ハードウェアについては、新たな定義が必要となる。九州大学の「システム LSI 設計人材育成実践プログラム (QUBE)」では、システム LSI 設計技術のスキルマップを提案し、教育効果の測定やカリキュラムの改善への取り組みが検討されている[林田 08]。

管理技術（プロジェクト）の基本形は、組込みシステム全体で共通と考えられる。

ETSS は、本研究の 1 つである「複合領域での教育手法をベースとした組込みシステム技術者教育の提案と実践評価」でのカリキュラムの検討のベースとなっている。第 4 章の 4.2.1 項で ETSS のスキル標準と本研究での対応を示している。

## 2.8 IoT 時代の組込みシステム

マイケル・ポーターは、「IoT 時代の競争戦略」[マイ 15]で、IoT を「第 3 の IT 化の波」と位置付けて、モノづくりの世界が製品プロダクトの販売からサービスの提供に大きく転換すると分析し、組込みシステムの事業領域の変遷を農業用トラクターを例に図 2.18 のよ

図 2.18 組込みシステム事業領域の変化（プロダクトからサービスへ）[マイ 15]

うに示している。従来の組込みシステムでは、農業用トラクター単体の製品（プロダクト）として販売されてきた。それに対して、パネル表示が見やすくなり（スマート製品化）、さらに通信機能でスマートフォンに各種情報を伝えることができるようになってきた。IoT時代を迎えると、農業用トラクターに設置されたセンサ情報などが、インターネットを通じて、クラウド上に送信され、農業機械システムとして稼働状況の見える化や他の農業機器との連携が可能になってきた。さらに、クラウド上で農業関連システムとの連携による複合システム（System of Systems）に進化して、従来の製品単体の販売モデルから農家管理システムや播種最適化システムなどのサービスを提供するモデルに変わると予測されている。究極的には位置情報など周囲の環境情報からトラクターを無人で自動運転をするなどの自律化も期待されている。

このように、IoTシステムは、組込みシステムとクラウド上のアプリケーションと通信ネットワークにより構成される複合システムといえる。通信ネットワーク化された組込みシステムにおいて、所有からシェア（共有）することに価値が移るとビジネスモデルも大きく変わると予想されている。このような IoT 時代を迎えると、組込みシステムの位置づけも大きく変わってきていると言える。

IoTシステムとその中の組込みシステムの位置づけを図 2.19 に示す。組込みシステムはユーザ側に近いエッジ側に位置づけられ、アクセスネットワーク（広域通信網）を介して、クラウドと接続されている。組込みシステムはセンサやアクチュエータを取り扱うデバイス群とそれらをエリアネットワーク（狭域通信網）で接続して全体を制御するゲートウェイから構成されている。自動車でいえば、デバイスは各種センサユニットやアクチ

図 2.19 IoT 時代における組込みシステムの位置づけ (IoT システムの全体像)

ユエータユニットに、エリアネットワークは車内ネットワークの CAN バス等に、ゲートウェイについてはエンジン制御ユニット等に相当する。

携帯電話などの通信系機器を除いて、組込みシステムがアクセスネットワーク（広域通信網）でクラウドにつながることはほとんどなかった。IoT 時代を迎えると、組込みシステムが通信ネットワークでクラウドにつながるようになってくると、以下のような 4 つの新しい課題が出てくると考えられる。

- ・1 つ目は、大量のデバイスからのデータ量が少ないセンサデータを如何に低コスト・低消費電力で通信を行なうか。

- ・2 つ目は、収集したセンサデータなどをどこでコンピューティング処理するか。

- ・3 つ目は、データのビッグデータ化と人工知能（機械学習）の実用化に対応してコンピューティング能力を如何に提供するか。

- ・4 つ目は、クラウドにつながることで今まで組込みシステムで考えてこなかったセキュリティやデータの利活用とプライバシーについてどのように扱っていくか。

以下、順番にそれぞれの課題について説明する。

### (1) 低コスト・低消費電力な通信ネットワーク

図 2.19 に示すように、狭い領域に設置されたデバイスからのセンサデータをエリアネットワーク経由ゲートウェイに集約してから、アクセスネットワーク経由でクラウド上のサーバに送信する場合と、組込みシステムからアクセスネットワーク経由で直接サーバに送信する場合がある。

このエリアネットワークとアクセスネットワークから構成される IoT ネットワークの全

図 2.20 IoT ネットワークの全体像

体像を図 2.20 に示す。エリアネットワークで低消費電力なネットワークは BLE、ZigBee、Wi-SUN が該当する。アクセスマルチキャストでは 3G/LTE の通信モジュールでの消費電力は小さくなっているが限界があり、現状では長い通信距離と低消費電力の両方を両立させた LPWA (Low Power Wide Area) ネットワークの SIGFOX、LoRAWAN、NB-IoT が注目されている。

また、アクセスマルチキャストでの通信プロトコルについても低消費電力化を目指した軽量のプロトコルである CoAP/6LoWPAN や MQTT が注目されている。

実際に低コスト・低消費電力の通信ネットワークを実現するために、それぞれの通信方式や通信プロトコルを評価して、最適な通信システムを構築していく必要がある。

## (2) エッジコンピューティングとクラウドコンピューティング

組込みシステムからのセンサデータなどは、通常はクラウド上のサーバに送信され、クラウド上に蓄積されたビッグデータに対して、統計解析や機械学習などの分析処理が行われる（クラウドコンピューティング）。クラウドに送信して処理して結果を得るまでのレスポンスタイムは 10ms 以上かかる。リアルタイム性を要求される場合や、アクセスマルチキャストでのトラフィックがネックになる場合やセキュリティの観点から、クラウドではなく閉じられた世界であるゲートウェイの位置づけで分析処理が行なわれるケースがある（エッジコンピューティング）。

また、外部電源から電力が供給されず遠隔に配置されるデバイスの場合には、徹底した低消費電力化を図る必要がある（ローパワーコンピューティング）。この場合は、コンピュータ能力の少ないマイコンで動かす必要があり、コンピュータパワーを必要とする処理は、よりコンピュータパワーのあるゲートウェイやサーバで処理することになる。

このように IoT システムでは、アプリケーションに応じて、コンピューティングの階層を使い分ける必要がある。

### (3) コンピューティング能力の提供方法

ビッグデータの統計解析や機械学習などの分析処理では、高性能な並列処理計算が必要とされる。これを実現するために当初は汎用高性能 CPU が使われてきたが、最近では汎用グラフィック処理ユニットである GPGPU が使われるようになってきた。さらに低消費電力で性能向上を目指して FPGA によるカスタマイズされた処理が注目されている。コンピューティング能力の実現方法として、歴史的には汎用化と専用化の繰り返しが行なわれてきたが、現在の IoT 時代は専用化の流れに入りつつあるともいえる。

### (4) セキュリティおよびデータの利活用とプライバシー

従来、通信機器以外の組込みシステムは外部とネットワークにつながれず、セキュリティについてはあまり考慮されてこなかった。IoT 時代を迎えると、インターネットなどでクラウドに接続されるようになると、従来の Web システムでのセキュリティとは異なった対応が必要になる。人を介さないでネットワークに接続されること、低消費電力化による低性能なマイコンでの実現など課題も多く、実システムではセキュリティ問題の解決が必要となる。また、豊富なデータを所有することがサービスの品質向上に貢献し価値の源泉になると言われている。プライバシー問題を回避するために匿名化処理を行なうことにより、データをうまく利活用することが望まれている。

## 2.9 組込みシステム開発における課題

2.1 節から 2.7 節まで述べてきた 1990 年代後半から 2000 年代にかけての組込みシステムの現状を分析すると、設計の課題、検証の課題、および、技術者育成の 3 つの課題に分類される。この中で設計の課題については、設計手法の革新を狙いとした「トップダウン協調設計システム」の取り組みなどを通じて解決に取り組んできた[清尾 99A][遠藤 00]。また、IP の活用やプラットフォームベース設計、抽象度の高い高位言語と進化した高位合成ツールの活用により、設計の生産性は大きく向上してきている。このように設計の課題は大きく改善されてきているので、残された検証と技術者育成についてそれぞれの課題と解決策について以下に述べる。

### 2.9.1 検証の課題とその解決策

検証の課題をまとめると以下のようになる。

- ・ 組込みシステムにおける協調設計では、ハードウェアとソフトウェアの分担を性能・コストなどの観点からトレードオフを行い、LSI 作りの前に事前に評価・検証を繰り返し行って、最適な分担を決めておく必要がある。

- ・組込みシステム自体が1チップのシステムLSIで実現されるようになり、不具合によるLSIの作り直しは、開発コストの増大や開発期間の大幅な遅延を招くことになる。LSI作りを行う前に、事前に不具合がないかを、システムレベルでハードウェアとソフトウェアを含めて検証を行うことが必要となる。このようなソフトウェアを含めた検証は協調検証と呼ばれている。

- ・独創的なアイデアを取り込んだ組込みシステムの開発では、LSI作りの前に、実機に近い環境でハードウェアとソフトウェアを動作させて人間の五感による評価や動くものによる実証評価を繰り返すことも必要である。

- ・組込みシステムの大規模化・複雑化に対して、システムLSIの設計では再利用可能設計資産であるIPを活用し、新しい追加機能のみを高位設計言語を使って記述し高位合成ツールを使って処理すれば、対処可能になってきているが、検証に関しては、再利用されたIPを含めてシステム全体の検証が必要となり、検証規模・検証コストは拡大する一方である。

- ・競争が激しい分野では短期開発が求められ、検証の効率化が求められている。

このような課題に対して、今回対象とする組込みシステムに関する検証に求められる要求をまとめると以下になる。

- ① 組込みシステムのいろいろな機能をハードウェアとソフトウェアで分担して実現する場合、まず最初に対象となるいろいろな機能を高位言語で表現したモデルを作成し、正しい機能がモデル化されたかを検証する。その後、ある機能のモデルをハードウェアにした時とソフトウェアにした時の性能・コストなどを評価し、全体として満足解が得られるまで繰り返し評価を行う必要がある。

- ② ハードウェアとソフトウェアの分担が決まったら、その間のインターフェースの実現方式を決め、ハードウェアとソフトウェアによる協調検証により、システム全体としての動作を検証する必要がある。

- ③ 独創的なアイデアを取り込んだ組込みシステムの開発では、人間の五感による評価や動くものによる実証評価が必要であることから、実機に近い環境でハードウェアとソフトウェアを動作させる協調検証も行う必要がある。この段階で不具合が見つかった場合には、最初の①の段階に戻って、改善を行う必要があり、①から③までの繰り返し検証作業をLSIを作る前に効率良く行う必要がある。

従来の検証手法では、①から③まで、個別に検証が行われてきた。今回のように①から③までを、繰り返し効率良く検証を行うためには、トップダウンにハードウェアとソフトウェアを組み合わせて効率良く検証を行う協調検証手法が期待される。

本論文では、第3章でトップダウン協調検証システムを提案し、マルチメディア系組込みシステム（映像圧縮処理システムなど）2件の事例に適用した成果について論じる。

### 2.9.2 技術者育成の課題とその解決策

技術者育成の課題をまとめると以下のようになる。

- ・組込みシステムは、応用分野に対して関連するいろいろな技術を統合して実現されることから、幅広いスキルの修得が必要である。

- ・組込みシステムは、ハードウェアとソフトウェアという異なる技術で実現される複合領域にあることから、両方のスキルを修得しておく必要がある。

- ・組込みシステムは、過去の技術の積み重ねの上に構築されており、内部のブラックボックス化が進んでいる。創造的な製品を開発するなどブレークスルーを図る場合や、複雑なトラブルを解決する場合などは、内部の基本的な原理・原則を理解しておくことが求められる。

- ・組込みシステムの価値は、ハードウェアとソフトウェアの分担を決めるアーキテクチャ設計までの段階で決まることから、性能・コストなどの相反する制約条件のもとで要求事項を満足するようにハードウェアとソフトウェアの協調設計により実現を図るシステムアーキテクトの役割は大変大きい。

特に、独創的な機能を新たに開発する場合には、ブラックボックス化した内部を含めて、新しい視点でブレークスルーを図ることができるシステムアーキテクトの育成が大変重要になる。既に、組込みシステム分野では、組込みソフトウェアやシステム LSI 開発者の立場から、いろいろな取り組みが行われているが、前述の課題を解決するためには、組込みシステム開発の課題を踏まえて体系的な技術者育成の取り組みが必要と考える。

筆者はいろいろな活動に参画した経験を踏まえて、第 4 章において、複合領域である組込みシステム分野の技術者育成手法について提案し、その実施成果を論じる。

### 2.9.3 組込みシステムを包含した IoT システム開発について

組込みシステムを包含した現在の IoT システムの開発においても、1990 年代後半から 2000 年代と同じように設計の課題、検証の課題、および、技術者育成の課題があると考える。組込みシステムの技術に加えて、さらに通信ネットワークとクラウドコンピューティングに関する技術を組み合わせて、サービスとしてのアプリケーションにふさわしい IoT システムを構築するには、幅広い技術力と全体を見通せる能力を必要とする。

IoT システムの開発においては、新しい価値の創出が期待されており、その開発方法として迅速にプロトタイプ作成を繰りかえし行なう「デザイン思考」のアプローチが注目されている[黒川 12]。何回かのプロトタイプ作成を経て、アプリケーションに最適になるように、構成要素であるハードウェア、ソフトウェア、および通信ネットワークを組み合わせて実現していくことになる。これは、組込みシステムにおける「ハードウェア」と「ソフトウェア」による協調設計に「通信ネットワーク」を組み込んで拡張したことにも相当する。

また、ポスト「京」プロジェクトにおいて「スーパーコンピュータ開発」と「アプリケーション開発」の協調設計（コザイン）の必要性が提唱されており[ポスト 17]、アプリケーションにとって最適になるように取り組む協調設計は今後とも必要なアプローチと考えられる。

設計の課題については、インターフェースの標準化、機能のモジュール化や API (Application Program Interface) 化が進み、プロトタイプ事例[秋山 16]やノウハウの公開サイトが充実してきており、使い方を理解すれば比較的容易にシステムを構築できるようになってきている。

それに対して、検証の課題については、IoT システムによる新たな価値創出が期待されており、その効果を早期に確かめるために、「デザイン思考」のアプローチとしてプロトタイプ作成・評価の頻繁な繰り返しが期待されている。

また、技術者育成の課題については、組込みシステム技術に加えてさらに幅広い技術を習得する必要があり、さらに新しい価値を創造し、評価する能力を持つことが期待されており、技術者育成の取り組みはますます重要になってきている。

本節での議論は本論文の主体ではないが、後の章において、IoT 時代と言われる 2017 年の今の視点からの考察を加えている。

## 2.10 まとめ

1990 年代後半から 2000 年代にかけての最先端の組込みシステム開発における現状と課題について、ものづくりの成果物である応用目的に最適化された組込みシステム製品（プロダクト）、いろいろな技術を組み合わせた複雑系の組込みシステムを開発する手順（プロセス）、組込みシステムの開発を目標通りに進めていくプロジェクト、プロジェクトに参画する技術者（ピープル）に必要なスキルの観点から整理を行なった。

主な課題として、設計の課題と検証の課題と技術者育成の課題の 3 つが考えられるが、設計の課題については、IP の活用やプラットフォームベース設計、抽象度の高い高位言語と進化した高位合成ツールの活用により、大きく改善されてきている。

本研究では残された検証の課題と技術者育成の課題を対象として、課題の分析と解決策を検討した。検証の課題に対しては、設計の上流から下流までハードウェアとソフトウェアを組み合わせて効率良く検証を行うトップダウン協調検証手法を提案し、第 3 章で具体的な研究内容について論じる。技術者育成の課題については、今後重要な役割を担うと期待されているシステムアーキテクトの育成を目標に、複合領域である組込みシステム分野の技術者育成手法について提案し、第 4 章で具体的な研究内容について論じる。

また、IoT 時代と言われる 2017 年の今の視点から、組込みシステムを包含した IoT システムの開発における現状と課題についても考察を行ない、検証の課題と技術者育成の課題の解決が重要であることを示した。

## 第3章 トップダウン協調検証手法の提案と適用評価

本章では、1990年代後半から2000年代にかけての組込みシステムにおける検証の課題に対して、設計の上流におけるシステムレベルの検証ステージから、ハードウェアとソフトウェアによる協調シミュレーションの検証ステージを経て、実機に近い環境での協調エミュレーションの検証ステージまで、効率よく繰り返しながら検証を行っていくことができるトップダウン協調検証手法を提案し、その適用評価について論じる[Seo97][Seo98][YaM98][安田98][安田99]。

### 3.1 はじめに

組込みシステムの最初のシステム設計の段階で、ターゲットシステムのアーキテクチャとアルゴリズムが、ターゲットシステムに求められる機能を満足するか評価される。評価の結果が満足されるまで繰り返し変更が行われる。満足な結果が得られると、組込みシステムはハードウェアとソフトウェアに分割される。このハードウェアとソフトウェアによる協調設計の段階では、最初はともにC言語などの抽象的なレベルで記述したモデルを使って、ハードウェアとソフトウェアによる協調シミュレーションにより機能と大まかな性能の評価が行われる。設計の詳細化が進むにつれ、順次より詳細なレベルで表現されたモデルに置き換えて、より精度の高い評価が行われる。さらに、実時間による評価や人間の感性による評価が必要な組込みシステムにおいては、実機に近い環境でのハードウェアとソフトウェアによる協調エミュレーションによる評価が必須となる。特に、独創的なマルチメディア系や制御系などの組込みシステムを開発する場合には、設計の上流から実機に近い環境まで、トップダウンで繰り返しながら検証を効率よく短期間で進めていくことが求められる。これを実現するためには、従来各設計の段階ごとにバラバラに進められてきた検証手法に対して、検証環境の統合や共通テストベンチの適用とともに、ハードウェアとソフトウェアのインターフェースと、ハードウェアとソフトウェアをそれぞれどのように表現して検証モデルを作成していくかというモデリング手法を明確にする必要がある。

ハードウェアとソフトウェアのインターフェースとモデリング手法に関しては、チャネルベースコンポーネントアーキテクチャ[Lin96]やバーチャルCPUアプローチ[Sch96]で報告されている。前者では、コンポーネントの間のインターフェースとその動作仕様は、システムレベルで協調合成を行うために定義されている。後者のアプローチでは、CPUのモデルと他のコンポーネントとのインターフェースは、協調シミュレーション環境を実現するために定義されている。

本章では、検証環境の統合と共通テストベンチの適用、および、コンポーネント論理バス(CLB: Component Logical Bus)アーキテクチャによるハードウェアとソフトウェアのインターフェースの統一により、設計の上流から下流に向けて各検証ステージで評価を繰り返しながら効率良く検証を行っていくトップダウン協調検証手法を提案する。

3.2節で、組込みシステムにおける検証の課題を述べ、3.3節で階層的な検証における現状と課題を整理し、3.4節で提案するトップダウン協調検証手法の概要を述べる。3.5節で提案したトップダウン

協調検証手法を評価するために構築した2つの事例の概要とその評価結果について述べる。3.6節で考察を行い、最後の3.7節でまとめを行う。

### 3.2 組込みシステムにおける検証の課題

組込みシステムの開発は、要求分析、システム設計、アーキテクチャ設計、ハードウェア設計＋ソフトウェア設計のように設計の上流から下流へと進んでいく。各設計フェーズで不具合が残ったまま下位のフェーズに移行すると多大の影響を及ぼすことから、それぞれのフェーズで不具合を取り除くための検証が必要である。特に、機能の大部分がシステム LSI で実現される場合には、製造フェーズに入る前に不具合を取り除くことが必須である。

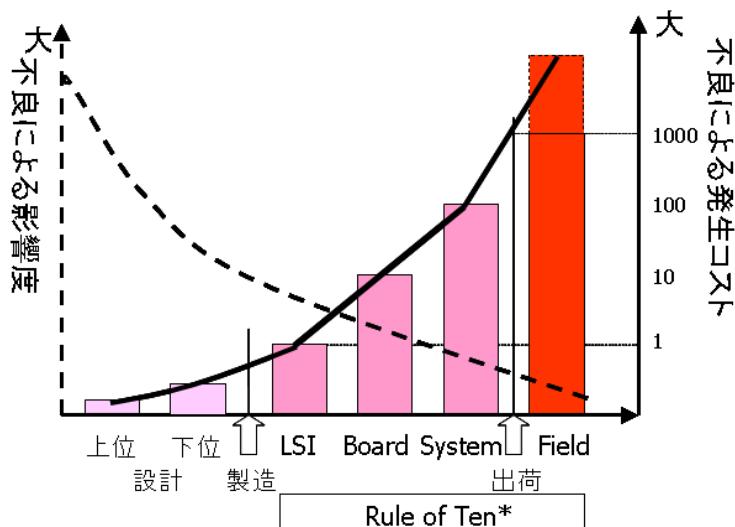

図3.1に開発の工程において発見される不良による影響度と発生コストを示す。横軸に設計・製造・出荷の流れを示す。左側の縦軸は不良による影響度を表し破線で示す。右側の縦軸は不良による発生コストを表し実線で示す。設計不良を見逃して、製造の後工程で設計不良が見つかる程、その不良による対策コストは膨大なものになる。製造工程での不良発見による発生コストは、10倍の法則 (Rule of Ten) に従うと言われている[AMB99]。LSI段階で見つかったときの発生コストを1と仮定すると、モジュールの段階では10、製品段階では100、出荷後で1000 ものコストがかかることを意味している。

特に、システム LSI を含んだ組込みシステム製品を開発する場合には、要求品質や設計品質が十分でなく不良が後工程で見つかると、不良による発生コストと開発遅延による売上の機会損失は膨大なものになり、その組込みシステム製品の事業にも影響を及ぼす可能性が高い。設計上流でのシステムレベルでの評価、アーキテクチャ設計段階でのハードウェアとソフトウェアによる実現における機能や性能の検証・評価、さらに実機に近い環境での実際のデータを使ったシステムレベルの検証・評価が必要である。

\*出典:T. AMBLER, B. BENNETTS, "Test and the Product Life Cycle," IEEE Design & Test of Computers, July-September 1999, Figure1(p.21) より引用

図3.1 不良による影響度と発生コスト

図 3.2 検証時間、検証工数の推移

また、組込みシステム製品（システム LSI）の大規模化が進んでおり、検証にかかるコスト（検証時間）は図 3.2(a)に示すように設計規模の拡大に比べ急激に増加している。設計コストについては、プラットフォーム化+IP 化による再利用設計と高位言語+高位合成により改善される方向にあるが、検証は設計で再利用された部分も含めて全体を扱うために、検証時間（図 3.2(a)）と検証工数（図 3.2(c)）は増え、全体の開発工数に占める割合も増加（図 3.2(b)）している。DVCon2011 のキーノートスピーチ[Rhi11]では検証のプロジェクト全体に占める割合は 55% と言われている。検証規模の拡大に対して検証を高速に実行できる環境が必要になる。設計の上流から下流までのそれぞれの検証段階で、検証目的に対応して実用的なレベルで検証・評価に耐える検証環境の構築が求められる。

特に、競争の激しいマルチメディア系や制御系などの分野で、独創的な製品を新たに開発する場合には、新しいアルゴリズムの考案から、ハードウェアとソフトウェアによる実現方法についてトレードオフを行い、最終的に組込みシステムとして実機に近い環境で目標とする機能・性能を持っているかを確認するまで、繰り返し階層的に検証することが必要とされる。

### 3.3. 階層的な検証における現状と課題

設計の上流でのシステムレベルの検証ステージから、実機に近い環境による検証ステージまで、検証は階層的に行なわれる。最初に、検証ステージの階層を説明し、従来の階層的な検証の取り組みの課題を示す。

#### 3.3.1 階層的な検証における現状

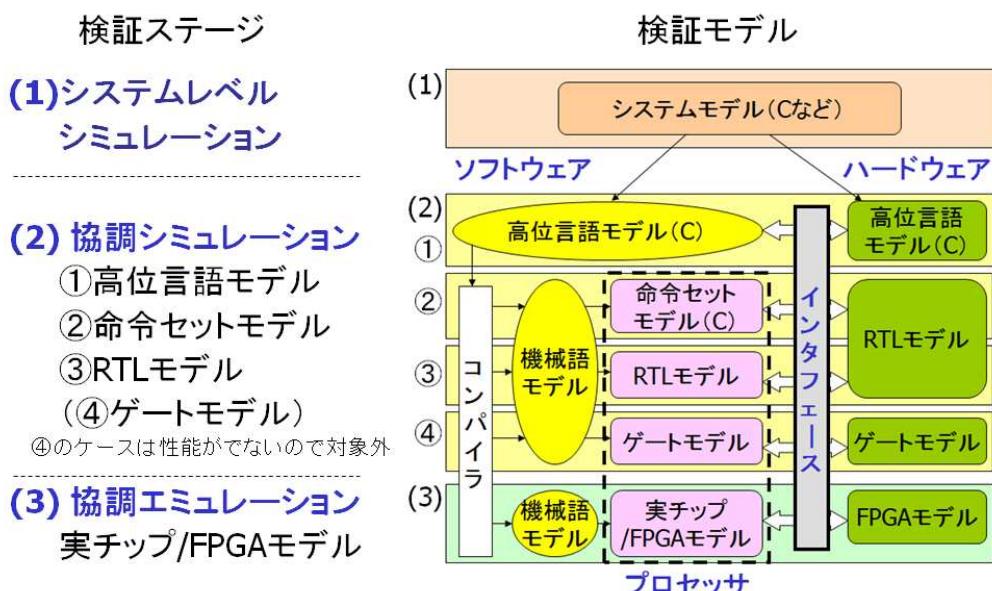

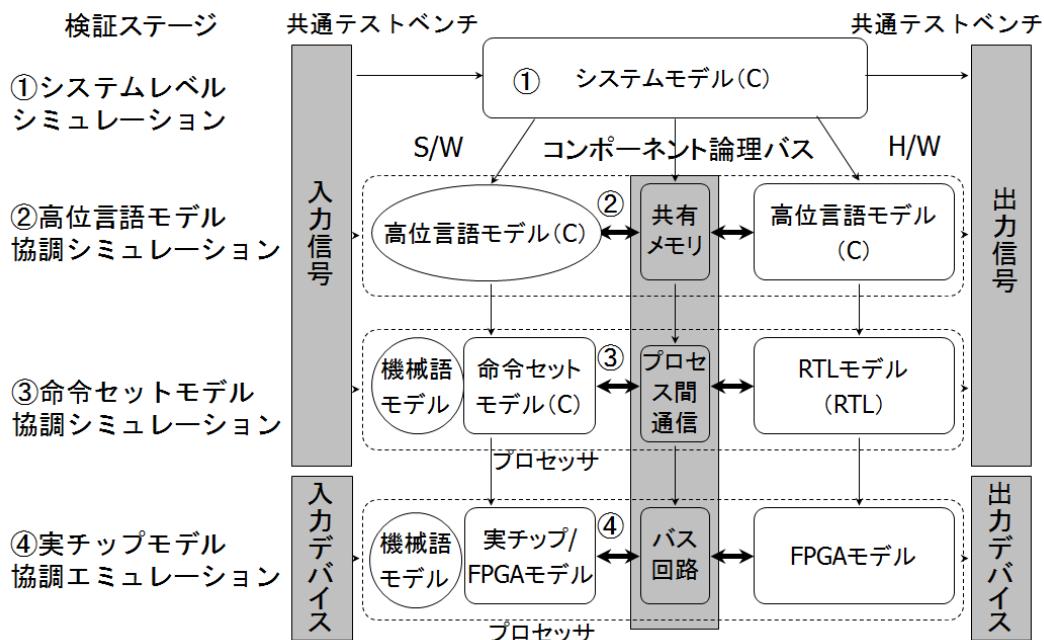

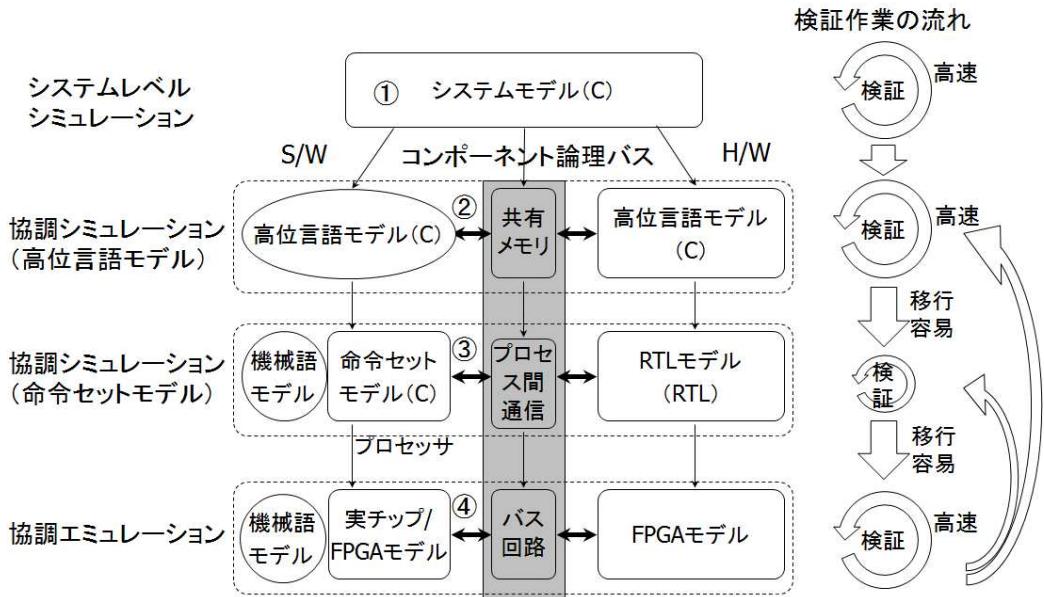

階層的な検証の全体像を図 3.3 に示す。システムレベルシミュレーションの検証ステージと、ハ

ドウェアとソフトウェアによる協調シミュレーションの検証ステージと、実機に近い環境でのハードウェアとソフトウェアによる協調エミュレーションの検証ステージの3つ検証ステージから構成される。協調シミュレーションの検証ステージは、ハードウェアとソフトウェアのモデル化の抽象度に応じて、さらに4つの検証ステージに分類される。

### (1) システムレベルシミュレーションの検証ステージ

システム仕様を実現するためのキーとなるアルゴリズムやアーキテクチャを事前に評価・検証する階層である。対象のアプリケーションをC言語などの高位言語でモデル化し、高速なシミュレーションにより、結果をビジュアルに表示しながら、設計の上流でトレードオフ評価（デザインレビュー）ができることが重要である。C言語やMatlabやStatemateなどでシステムの動作を表現したシステムモデルが使われる。

### (2) 協調シミュレーションの検証ステージ

システムレベルシミュレーションによる評価の結果、仕様がある程度決まった段階でハードウェアとソフトウェアの分担を決める。高性能なパソコンやサーバ上でハードウェアとソフトウェアをモデル化して、ハードウェアとソフトウェアの協調シミュレーションにより、機能の検証とシステム的な性能評価を行う。

この階層では、モデルの抽象度に対応して、さらに4つの検証ステージに分けられる。

#### ①高位言語モデル

システムを構成する機能モジュールをターゲットとなるプロセッサに依存しないC言語などの高位言語で表現した高位言語モデルを使って協調シミュレーションを行う。協調シミュレーションは、

図 3.3 階層的な検証の全体像

ターゲットのプロセッサアーキテクチャが決定される前に開始することができる。ソフトウェアはシミュレーションを実行するホストマシンの高位言語モデルとして実行される。ハードウェアの高位言語モデルと組み合わせて、高速に協調シミュレーションを実行することが可能である。主に、ハードウェアとソフトウェアで分担した機能の検証を行う。

#### ②命令セットモデル

ターゲットとなるプロセッサの命令動作を C 言語などで記述した命令セットモデルを用いて協調シミュレーションを行う。ソフトウェアとして実行される高位言語モデルはターゲットプロセッサの機械語に変換され機械語モデルが生成される。この機械語モデルがターゲットプロセッサの命令セットシミュレータによって解釈され、実行される。残りのハードウェアは、RT レベルで表現された RTL モデルが使われる。命令セットシミュレータが、キャッシュやパイプライン動作を正確に模擬できる場合には、性能の評価を行うことができる。

#### ③RTL モデル

ターゲットプロセッサと残りのハードウェアを RT レベルで表現した RTL モデルを用いて、クロックに同期してサイクルベースで協調シミュレーションを行う。この協調シミュレーションでは、クロックの精度で正確なタイミングの評価が可能であるが、シミュレーションの実行により多くの時間が必要である。なお、プロセッサの RTL モデルを取得することができないときは、この段階で協調シミュレーションを実行することはできない。

#### ④ゲートモデル

プロセッサと残りのハードウェアをゲートレベルで表現したゲートモデルを用いて、タイミング精度の協調シミュレーションを行う。シミュレーションは、正確なタイミングで行われるが、実行時間が非常に長くなるので、この段階での協調シミュレーションは一般に実施されない。

### (3) 協調エミュレーションの検証ステージ

ハードウェアとソフトウェアの協調シミュレーションの速度は実機に比べて  $10^{-6}$  から  $10^{-4}$  程度になる。マルチメディア系や通信系のような人間の感性による評価が必要なものや応用ソフトウェアを含めた組込みシステムの実動作に近い検証・評価等については、実機評価機（ブレッドボード）を作成して行うのが一般的である。特にシステム LSI が出来る前に組込みソフトウェアを動作させて検証するときには必須である。また、顧客獲得のためには、実際に動作する試作モデルを見せることがますます重要になってきている。

従来の実機評価機の作成はその都度基板作成を伴うことから基板設計の開発コストや開発期間が必要になる。また、変更への追随が大変で、複数の実機評価機が必要な場合に同じ状態を保つことも難しくなることから、FPGA などのプログラマブル素子を活用したエミュレーション技術が注目されている。

エミュレーションでは、サーバやパソコン上の設計データをネットワークからこれらのプログラマブル素子にマッピングすることにより、容易に実機に近い形で動作させることが可能となる。適用にあたっては、現状の FPGA などのプログラマブル素子の性能上

表 3.1 各検証ステージでの評価内容

| 検証ステージ             |              | 評価内容                                    |

|--------------------|--------------|-----------------------------------------|

| (1)システムレベルシミュレーション | システムモデル      | アルゴリズムの評価(C言語)<br>(本研究ではC言語を採用)         |

| (2)協調シミュレーション      | ①高位言語モデル     | ハードウェアとソフトウェアの機能の評価                     |

|                    | ②命令セットモデル    | ハードウェアとソフトウェアの性能の評価                     |

|                    | ③RTLモデル      | 主にハードウェアのタイミング評価(実行時間がかなりかかる)           |

|                    | ④ゲートモデル      | 正確なタイミング評価→実行時間がかかるので、静的タイミング検証を適用      |

| (3)協調エミュレーション      | 実チップ/FPGAモデル | 実機に近いシステムレベルの評価<br>人間の感性による評価、プロトタイプの提示 |

1MHz から 20MHz の速度でしか動作できないことを前提に、使い方を工夫する必要がある。

ターゲットプロセッサについては、その論理合成可能な RTL モデルが存在すればプログラマブル素子にマッピングした FPGA モデルが使われる。存在しない場合には実チップを使った実チップモデルが使われる。残りのハードウェアは論理合成可能な RTL モデルをプログラマブル素子にマッピングした FPGA モデルが使われる。実際のシステムに近い環境で高速な検証が可能である。

各検証ステージでの評価内容をまとめると、表 3.1 のようになる。

### 3.3.2 階層的な検証における課題

競争の激しいマルチメディアや制御機器で、独創的な製品を開発する場合には、プロトタイプを何回もつくりながら、設計の上流から下流まで、繰り返し評価・検証を行なう必要があるが、現状では以下の課題が存在する。

①従来の階層的な検証では、各階層の検証ステージ毎に検証モデルの表現方法が異なることから検証環境も異なり、また、検証に必要な入出力信号を扱うテストベンチもばらばらで、上流から下流まで繰り返し検証を行なうことが容易ではなかった。

②従来の階層的な検証では、各階層におけるハードウェアとソフトウェアのインターフェースが異なる場合があり、階層をまたがって検証する度にインターフェース部のモジュールの変換が必要になっていた。

③協調シミュレーションや協調エミュレーションの検証ステージでは、プロセッサを実行するための検証モデルの入手性が大きな問題である。今回は入手できるプロセッサを対象にすることで対応することにした。

このような課題に対する解決策として、次の 3.4 節でトップダウン協調検証手法を提案する。

### 3.4. ツップダウン協調検証手法の提案

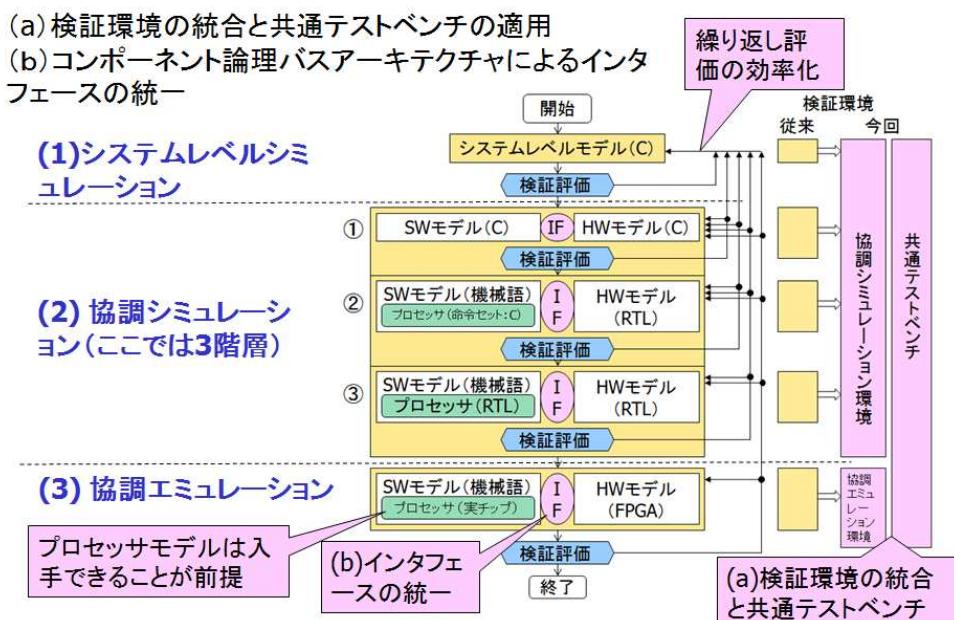

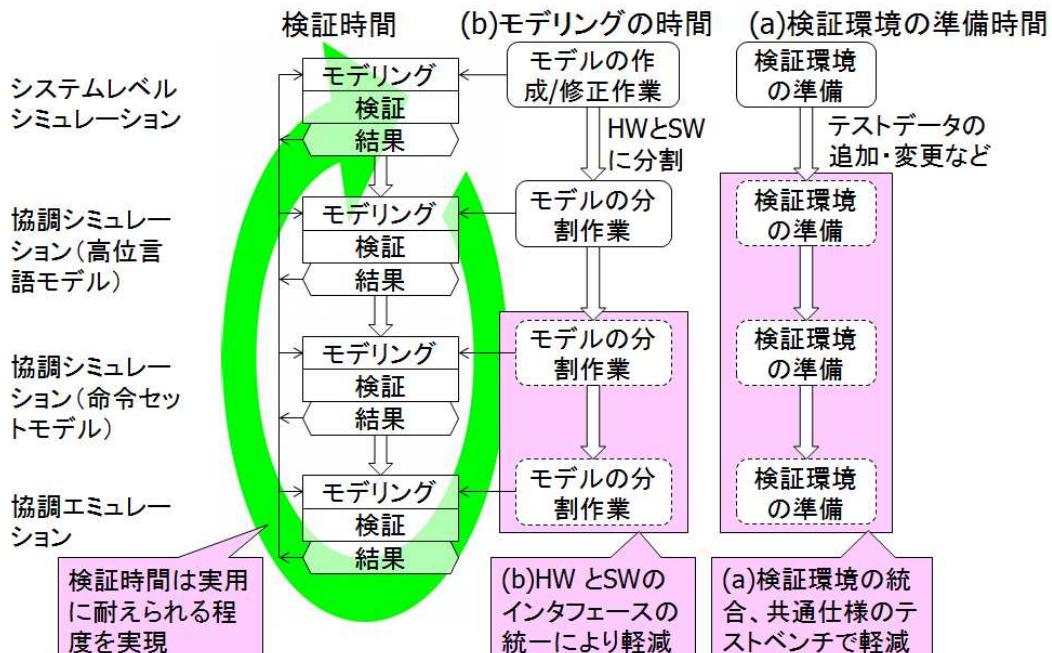

競争の激しいマルチメディアや制御機器で、独創的な製品を開発する場合における階層的な検証の課題を解決するために、設計の上流における検証ステージから下流の実機に近い環境による検証ステージまで効率良く繰り返し検証できるツップダウン協調検証手法を提案する(図3.4参照)。

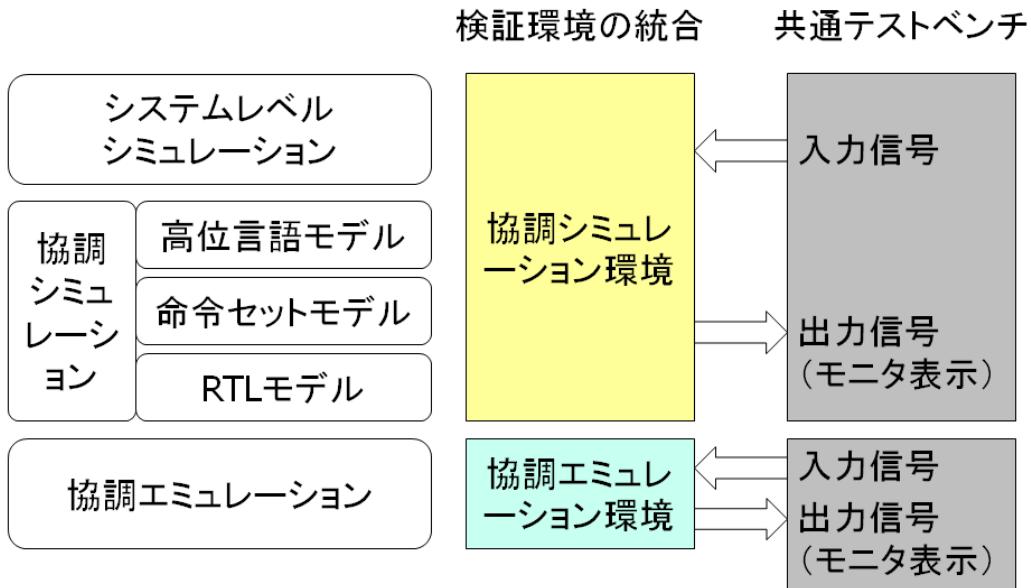

#### (a) 検証環境の統合と共通テストベンチの適用

システムレベルシミュレーションと3階層の協調シミュレーションの検証環境を、高位言語(C)モデルとRTLモデルを混在して検証できる協調シミュレーション環境に統合し、システムレベルシミュレーションの検証ステージから、実機に近い環境での協調エミュレーションの検証ステージまで共通テストベンチを適用することにより、効率よい繰り返し検証を実現する。

#### (b) コンポーネント論理バスアーキテクチャによるインターフェースの統一

ハードウェアとソフトウェアのインターフェースを、コンポーネント論理バスアーキテクチャに統一することで、インターフェース部におけるモジュールの独立性を高め、階層をまたがる検証の効率化を実現する。

#### 3.4.1 検証環境の統合と共通テストベンチの適用

各検証ステージでは、検証の対象となるソフトウェア部分とハードウェア部分をそれぞれコンピュータで検証できるようにモデル化する必要がある。3.3.1節で説明したように、システムレベルシミュレーションと協調シミュレーションの階層におけるモデル化ではC言語モデルとRTLモデルが使われるが、従来の検証ではそれぞれ異なった環境で提供されてきた。今回シミュレーション環境として、C言語モデルとRTLモデルの両方を扱える

図3.4 ツップダウン協調検証手法の提案

図 3.5 検証環境の統合と共通仕様のテストベンチの適用

協調シミュレーション環境に統合する。また、検証のための外部入力信号の生成や外部出力信号の表示などを扱う共通テストベンチを適用する（図 3.5 参照）。このように、シミュレーション環境の統合や共通仕様のテストベンチの適用により、検証につかうテストデータ（入出力信号データ）の共通化などが可能になり、システムレベルシミュレーションから、実機に近い協調エミュレーションまで、何回も繰り返し検証する作業の効率化を実現することができる。

### 3.4.2 コンポーネント論理バスアーキテクチャによるインターフェースの統一

ハードウェアとソフトウェアのインターフェースとして、従来は、検証シミュレーションの命令セットモデルの検証ステージ以降にハードウェアの実装と同じメモリマップド IO 方式を適用し、それ以前の高位言語モデルの検証ステージでは分割に応じて自由なインターフェースを定義する場合が多かった。そのため、高位言語モデルの検証ステージから下位の命令セットモデルの検証ステージに移行するときに、インターフェースを変更しそれに対応したハードウェアとソフトウェアのモジュールの変更が必要であった。

今回の提案では、高位言語モデルの検証ステージでも、インターフェースとしてメモリマップド IO 方式を適用することにより、協調検証シミュレーションの検証ステージから、協調エミュレーションの検証ステージまで、一貫したインターフェースによりインターフェース部分のモジュール化を図り、効率の良い繰り返し検証ができることを狙っている。

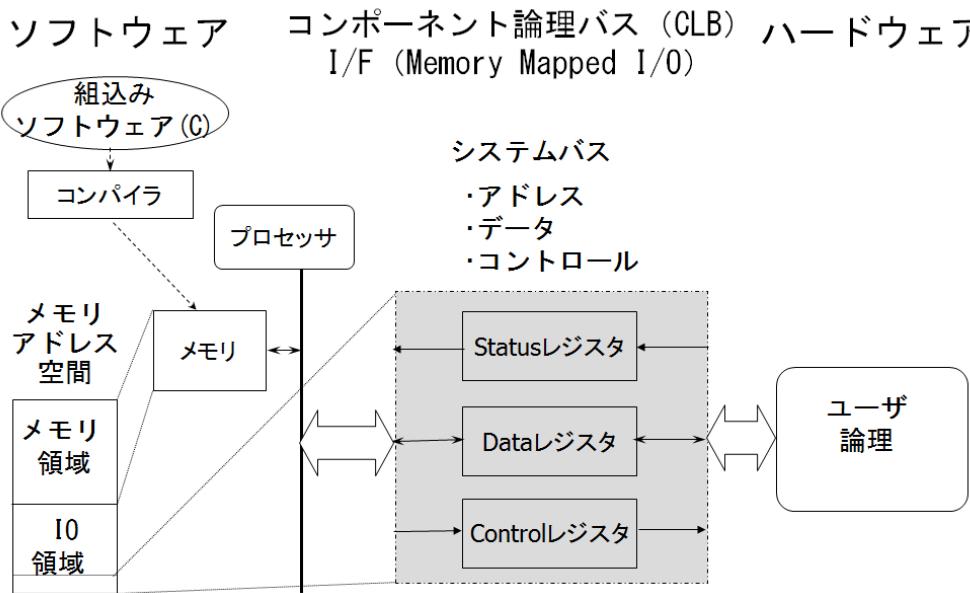

今回提案したメモリマップド IO 方式に統一したインターフェースについてコンポーネント論理バスアーキテクチャと定義した（図 3.6）。コンポーネント論理バスでは、システムバス上のメモリアドレス空間に割り付けられた Control レジスタ、Data レジスタ、および Status レジスタを介して、プロ

セッサ上で実行されるソフトウェアとワイヤードロジックで実行されるハードウェアの間で情報のやり取りを行う。

システムバスは、アドレス信号、データ信号、およびコントロール信号から構成される。アドレス信号で、Control レジスタ、Data レジスタ、および Status レジスタを選択し、コントロール信号で、ソフトウェアからハードウェア側に書き込むのか、ハードウェア側からソフトウェア側に読み込むのかを指定する。データ信号を使って書き込むデータや読み込むデータを送受する。

ソフトウェアとハードウェアの間のデータ交換は、次のように行われる。ソフトウェアが、Data レジスタにデータを書き込んだあと、Control レジスタに起動の指示を書き込むことにより、ハードウェアを起動し、データを転送する。

ハードウェアにおける処理が完了すると、処理データを Data レジスタに書き込んだあと、処理の結果の状態を Status レジスタに書き込む。ソフトウェアにハードウェアの処理の終了を通知する方法には、割り込み方式とポーリング方式があるが、今回の研究ではポーリング方式を採用している。なお、Control レジスタ、Data レジスタ、Status レジスタの構成やビット数などは、ハードウェア側で実現する処理内容に依存する。

今回の提案は、このコンポーネント論理バスアーキテクチャを実装レベルだけではなく、設計の上流の協調シミュレーションの階層にも適用することで、トップダウンで検証を繰り返し効率よく行うことを狙ったものである。すなわち、協調シミュレーションから協調エミュレーションまで、異なる検証ステージでのモデルの置換やハードウェアとソフトウェア間のモデルの組み合わせにおいて、わずかな変更で移行できることが可能になることが期待できる。なお、協調エミュレーションでは、コンポーネント論理バスアーキテクチャをそのまま実装することで実現できるが、協調シミュレーションの階層においては、模擬的に実現することが必要になる。協調シミュレーションにおけるコンポーネント論理バスのインターフェースの実現方式として、図 3.7 に示すように共有メモリ方式、信号イベ

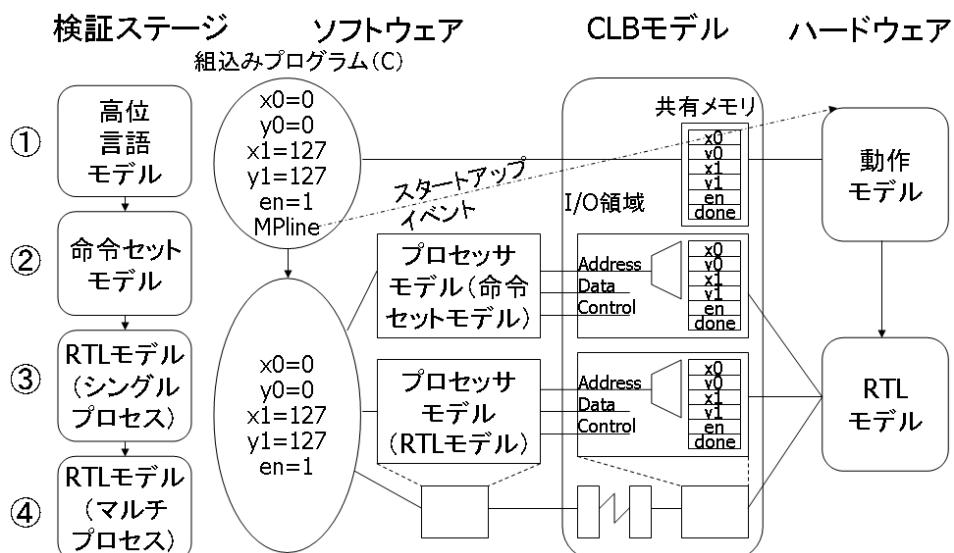

図 3.6 コンポーネント論理バス (CLB) アーキテクチャの構成

ント方式およびプロセス間通信方式の3つの方式を考える。

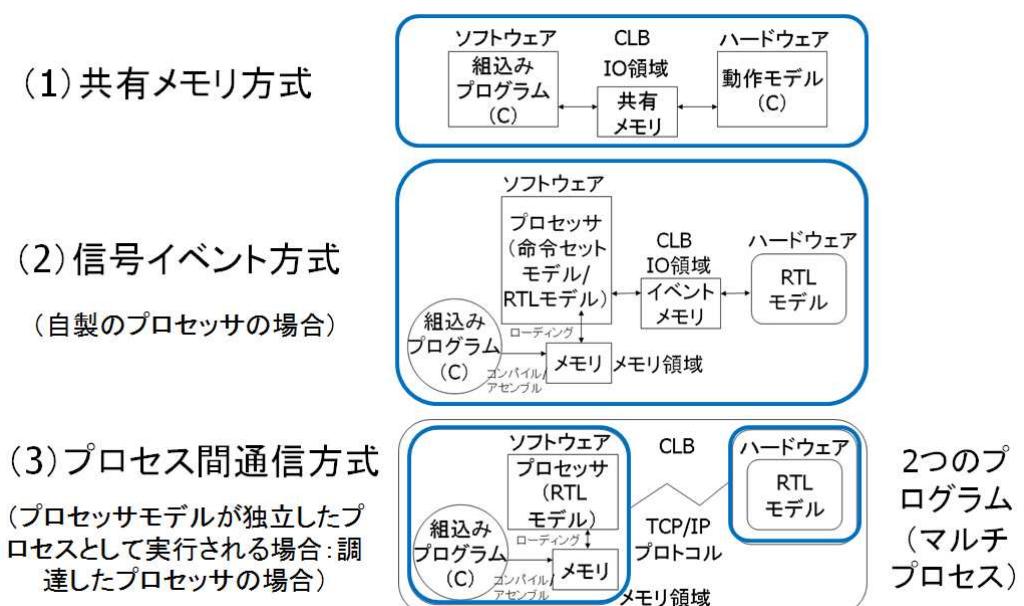

### (1) 共有メモリ方式

高位言語レベルの検証ステージでは、図3.7(1)に示すように共通メモリを用いて実現する。I/O領域は、メモリアドレス空間の一部として割り当てられ、ソフトウェアとハードウェアがこの空間をアクセスすることでデータが交換される。

ソフトウェアは、共通メモリのIO領域に割り当てられたDataレジスタにデータを書き込む。一連の書き込み操作が完了すると、起動イベントをControlレジスタに書き込み、ハードウェアに制御を渡す。ハードウェアは制御が渡されると、共通メモリ空間に割り当てられたハードウェアのレジスタから、必要なデータを読み込み、コントロールレジスタで指定された処理を行う。処理が終了すると、処理結果や状態をIO領域に割り当てられたDataレジスタとStatusレジスタにそれぞれ書き込む。ソフトウェアは、ハードウェアから制御が戻ってくると、共通メモリ空間に割り当てられているDataレジスタやStatusレジスタを読み取り、ハードウェアの処理結果や状態を取得する。

### (2) シングルプロセスでの信号イベント方式

プロセッサのモデル（命令セットモデル/RTLモデル）とハードウェアのRTLモデルを1つのプログラム（シングルプロセス）でシミュレーションできる場合には、図3.7(2)に示すように1つのプログラム（シングルプロセス）での信号イベント方式で実現する。

ソフトウェアは機械語の書き込み（Store）命令により、必要なデータをイベントメモリのIO領域に割り当てられたDataレジスタに書き込む。すべての必要なデータを書き込んだ後に、ハードウェアを起動する信号（信号イベント）をControlレジスタに書き込む。ハードウェアは、起動信号の信号イベントを受け取った後、IO領域のDataレジスタの内容を読み込み、Controlレジスタで指定さ

図3.7 協調シミュレーションにおけるインタフェースの実現方式

れた処理を行う。ハードウェアは、処理を終了すると、処理結果や状態を IO 領域に割り当てられた Data レジスタと Status レジスタにそれぞれ書き込む。Status レジスタには、終了の信号イベントが含まれている。ソフトウェアは Status レジスタの終了フラグにより、ハードウェアの処理が終わったことを検知する。

### (3) マルチプロセスでのプロセス間通信方式

プロセッサのモデル（命令セットモデル/RTL モデル）とハードウェアの RTL モデルがそれぞれ異なるプログラム（マルチプロセス）でシミュレーションされる場合には、図 3.7(3)に示すようにプロセス間通信方式で実現する。プロセッサのモデルが他部門で開発されており、ハードウェアのモデルのシミュレータと同じプログラム（シングルプロセス）で実行できない場合に適用される方法である。

プロセッサのモデルとハードウェアの RTL モデルの間の IO 領域を通したデータ通信は、ソケットインターフェースやリモートプロシージャコールなどを用いて実現される。

## 3.5 マルチメディア系組込みシステムによる適用評価

本節では、提案したトップダウン協調検証手法を評価するために、2 件のマルチメディア系組込みシステムを対象に適用した。1 件目では、比較的簡単な線描画システムを対象に、ハードウェアとソフトウェアによる協調シミュレーションの検証ステージに適用して評価を行った。2 件目では、より複雑な映像圧縮処理システムを対象に、システムレベルシミュレーションから、ハードウェアとソフトウェアによる協調シミュレーション、さらに、設計の下流の実機に近い形で実動作と人間の感性による評価が可能になる協調エミュレーションの検証ステージまで適用して評価を行った。

最初に、対象となる組込みシステムを設計・検証するために使用した協調設計・検証ツールとプロセッサのモデリングについて説明する。続いて、線描画システムによる適用評価について述べ、最後に画像圧縮伸張システムによる適用評価について述べる。

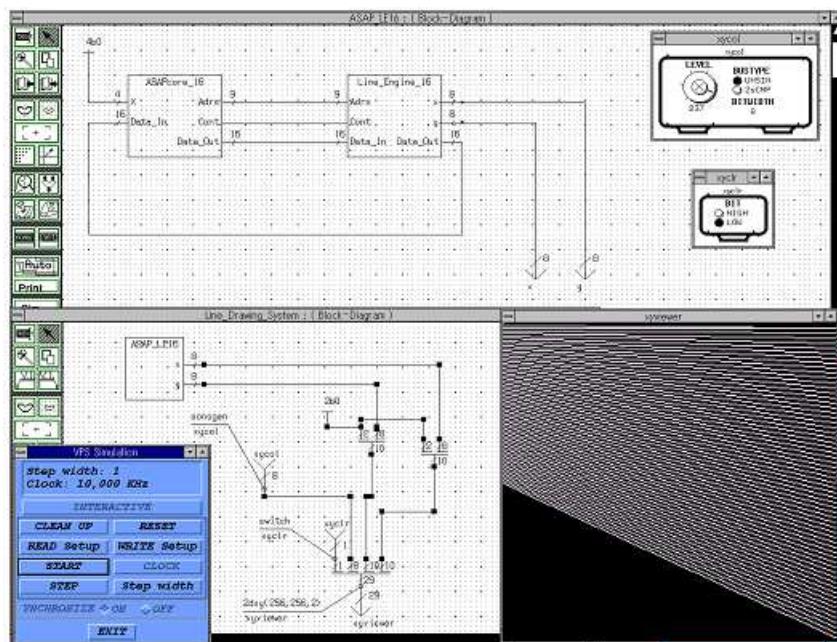

### 3.5.1 協調設計・検証ツール

本提案を実現するのにふさわしいツールとして、ハードウェアとソフトウェアの協調設計・協調シミュレーションでは米国 HP 社で開発された Tsutsuji を、ハードウェアとソフトウェアの協調エミュレーションでは米国 Aptix 社のシステム MP4 を採用した。

#### (1) Tsutsuji の概要

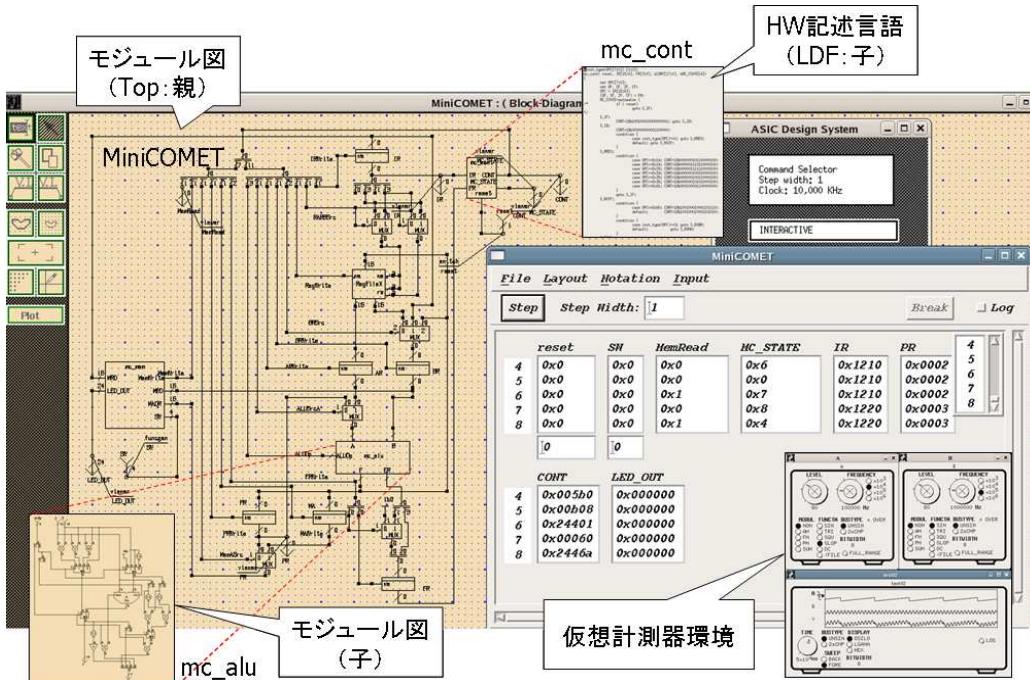

Tsutsuji は、米国 HP（ヒューレットパッカード）社の研究所で 1993 年に開発され、その後 1996 年に図研から Vps（Virtual Prototyping System）として販売された [Cul93][ZUK96] [田中 11]。

Tsutsuji は、高位言語（C）や RTL など多様な設計記述形式をサポートし、高速な論理合成機能とビジュアルな仮想計測器環境を持った高速なシミュレーション機能を備えており、

協調シミュレーション環境を構築するのに最適であった。

Tsutsuji の実行画面の例を図 3.8 に示す。モジュール図は回路図表記(信号線はベクタ表記)で階層的に表現できる。ブロックの中は HW 記述言語 (LDF) でも記述が可能である。また、ステップ実行の画面では、1 ステップ毎にレジスタの値がどのように変化していくかを観察することができる。さらに、仮想計測器環境では、仮想的なつまみで値を設定したり、仮想的なディスプレイに波形を表示したりすることができる。

図 3.8 Tsutsuji の実行画面例

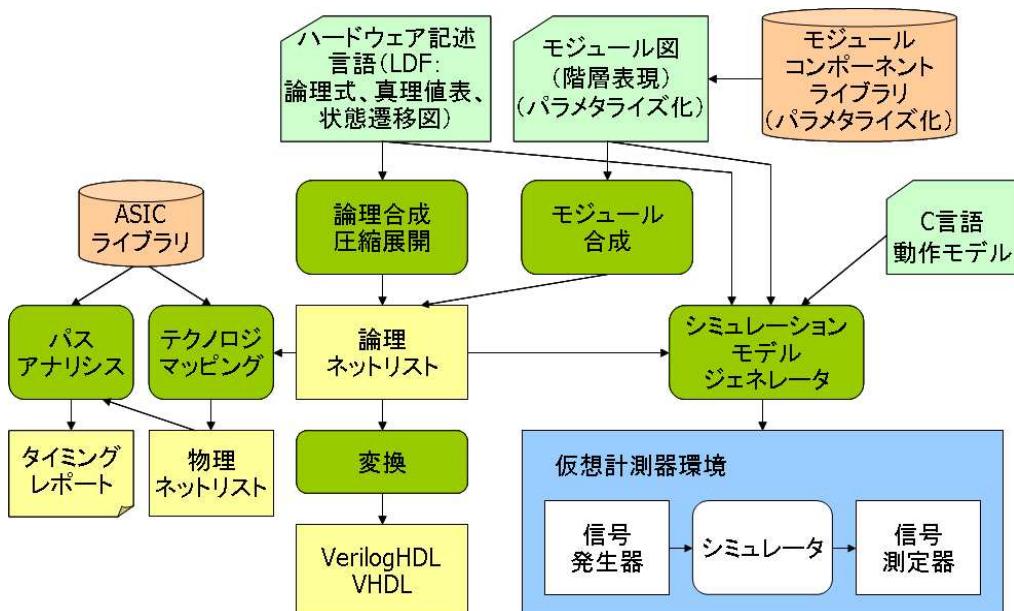

図 3.9 Tsutsuji の開発環境

Tsutsuji の開発環境を図 3.9 に示す。設計対象を階層記述できるモジュール図とハードウェア記述言語（LDF）で記述し、C 言語動作モデルと組み合わせて、シミュレーションモデルを生成し、仮想計測器環境のもとで高速なシミュレーションを行うことができる。また、論理合成・圧縮展開機能やモジュール合成によってゲートレベルの回路を生成し、ネットリスト変換により既存の Verilog や VHDL に接続することができる。さらに、ASIC ライブドライバを参照し、パス解析によりタイミングレポートを作成することができる。

## (2) 協調エミュレーションツール：システムエミュレータ（MP4）の概要

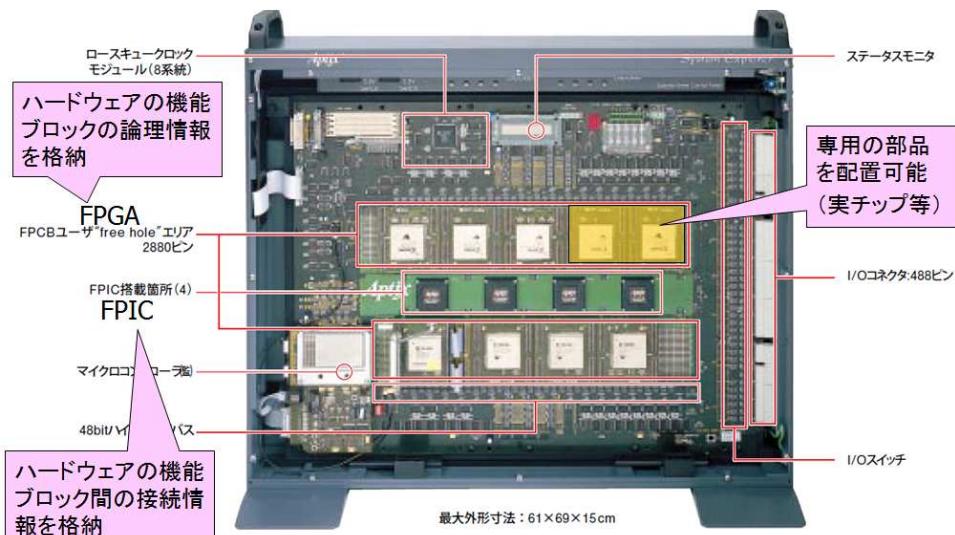

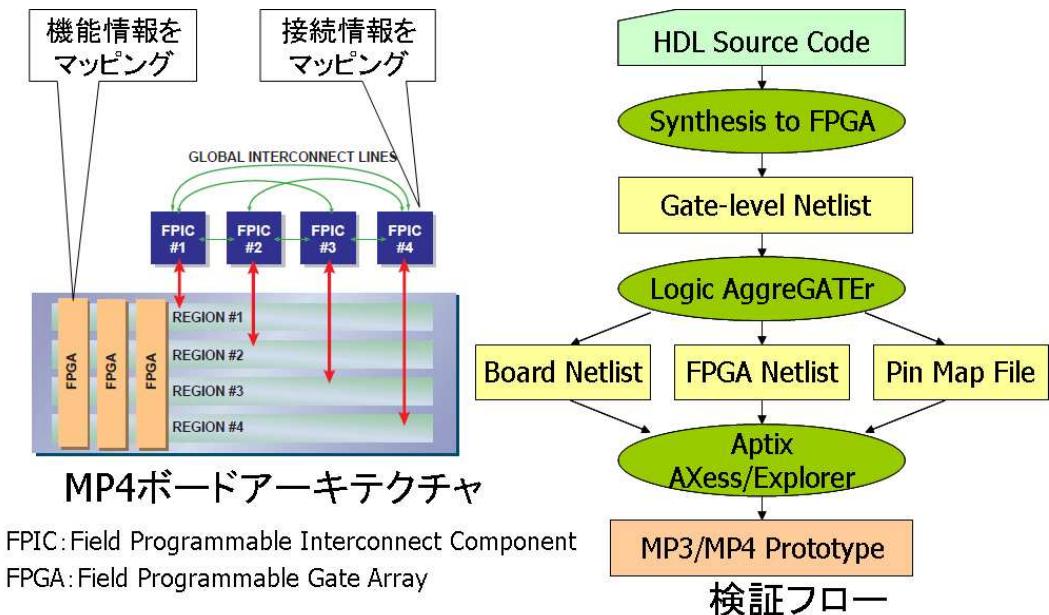

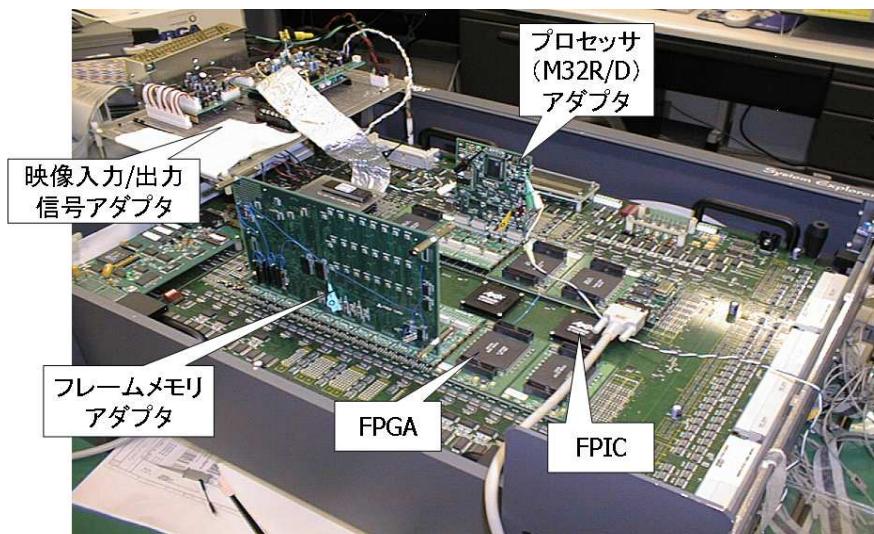

米国 Aptix 社（国研が販売）のシステムエミュレータの構成を図 3.10 に、プロセッサ M32R/D の実チップを搭載したアダプタボードの例を図 3.11 に、開発環境を図 3.12 に示す。1990 年代後半において協調エミュレーション環境を構築するのに最適なシステムであった。

図 3.10 のシステムエミュレータ MP4 には、論理情報をプログラム可能な FPGA (Field Programmable Gate Array) と接続機能をプログラム可能な FPIC (Field Programmable Interconnect Component) が搭載されている。図 3.11 に示すようなプロセッサ等の実チップやインターフェース回路を搭載したアダプタを開発し、MP4 に搭載することができる。図 3.12 の HDL 記述された設計データとピン割り付けデータから、FPGA と FPIC の書き込みデータを作成し、ダウンロードすることで、システムエミュレーションを実現する。

図 3.10 Aptix 社システムエミュレータ MP4 の構成

図 3.11 システムエミュレータのアダプタ（自製）の例

図 3.12 システムエミュレータの開発環境

### 3.5.2 プロセッサのモデリング

協調検証シミュレーションの命令セットモデルの検証ステージ以降では、使用するプロセッサの検証モデルが必要になる。検証モデルは、検証ステージに適切なものを使用する必要があり、如何にしてそれらを入手するかが課題である。今回の提案では、トップダウン協調検証手法の各検証ステージにおいて、プロセッサの検証モデルの位置づけを明確にして、検証モデルの入手性を考慮して協調シミュレーションと協調エミュレーションに取り組んだ。

#### (1) 協調シミュレーションの検証ステージ

協調シミュレーションの段階におけるプロセッサのモデリングについて表 3.2 に示す。

高位言語モデルでは、プロセッサは意識せず、ハードウェアとソフトウェアの C 言語モデル同士を協調シミュレーション環境で実行することになる。高速な実行が期待できる。

命令セットモデルでは、プロセッサの命令セットを C 言語モデルで表現する。ASAP のような自社製のプロセッサであれば、C 言語による命令セットモデルの入手性は問題ない。調達プロセッサを利用する場合には調達先からの C 言語による命令セットモデルの入手性に依存する。本研究では、同じ企業であったことから入手することができた。三菱電機製の 16 ビットマイコン M16C を使ったプロセッサの命令セットシミュレータの例が報告されている[Gho95]。

RTL モデルでは、自製のプロセッサの場合は問題ないが、調達の場合は同一企業内でも入手が困難な場合が多い。

表 3.2 協調シミュレーションにおけるプロセッサのモデリング

| 検証ステージ        | プロセッサのモデリング | モデルの入手性                             |             |

|---------------|-------------|-------------------------------------|-------------|

|               |             | 自製                                  | 調達          |

| (2)協調シミュレーション | ①高位言語モデル    | プロセッサは意識しない。ホスト上でCモデル同士で検証          | プロセッサは意識しない |

|               | ②命令セットモデル   | 命令セットをCモデルで表現。なお、命令セットのクロック数を評価可能   | 可 比較的容易     |

|               | ③RTLモデル     | RTLレベルのHDLで表現。クロックレベルの正確なタイミングを評価可能 | 可 困難        |

ASAP: Application Specific Adaptable Processor

M16C: 三菱電機製16ビットマイコン

M32R/D: 三菱電機製DRAM内蔵32ビットプロセッサ(命令セットシミュレータは別プロセスとして提供)

例えば ASAP M16C, M32R/D

## (2) 協調エミュレーションの検証ステージ

協調エミュレーション環境は以下のようにして構築される。

- ・プロセッサのモデルは、HDL 記述されたものがある場合は、HDL 記述のモデルを論理合成し FPGA にマッピングしたものが使われる。HDL 記述したものがない場合には実チップが使われる。

- ・アプリケーションを記述した C プログラムは、ターゲットとなるプロセッサの機械語にコンパイルされ、バイナリーデータが書き換え可能メモリに格納される。

- ・ハードウェアのモデルは HDL 記述したものを論理合成し FPGA にマッピングされる。

- ・部品間の接続情報は、プログラマブルなスイッチアレイ素子にマッピングされる。

- ・アナログ映像信号を A/D 変換によりデジタル信号に変換する入力信号アダプタや、デジタル信号を D/A 変換により外部のディスプレイに表示する出力信号アダプタにより、リアルな共通テストベンチを提供する。

協調エミュレーションにおけるプロセッサのモデリングについて表 3.3 に示す。

実チップモデルでは、プロセッサの本物のチップをそのまま利用する。チップをエミュ

表 3.3 協調エミュレーションにおけるプロセッサのモデリング

| 検証ステージ        | プロセッサのモデリング     | モデルの入手性                         |        |

|---------------|-----------------|---------------------------------|--------|

|               |                 | 自製                              | 調達     |

| (3)協調エミュレーション | 実チップモデル/FPGAモデル | 実際のチップを使ったモデル                   | 製造後可 可 |

|               |                 | HDLで表現されたモデルから論理合成して作成したFPGAモデル | 可 困難   |

例えば ASAP M16C/M32R

レータに搭載するアダプタの開発が必要である。

FPGA モデルでは、HDL 記述されたプロセッサのモデルを論理合成して FPGA にマッピングすることで実現できる。自製のプロセッサの場合は問題ないが、調達したプロセッサの場合は一般に HDL モデルの入手が困難なので実現は難しい。

### 3.5.3 線描画システムによる評価

1 つ目の事例では自製したプロセッサを使った線描画システムを対象に、協調シミュレーションにおけるトップダウン協調検証手法についての評価を行った。協調シミュレーションにおける 3 つの検証ステージ（高位言語モデル、命令セットモデル、RTL モデル）での実現方法と効率よく検証できるかの評価が中心である[Seo97][YaM98]。

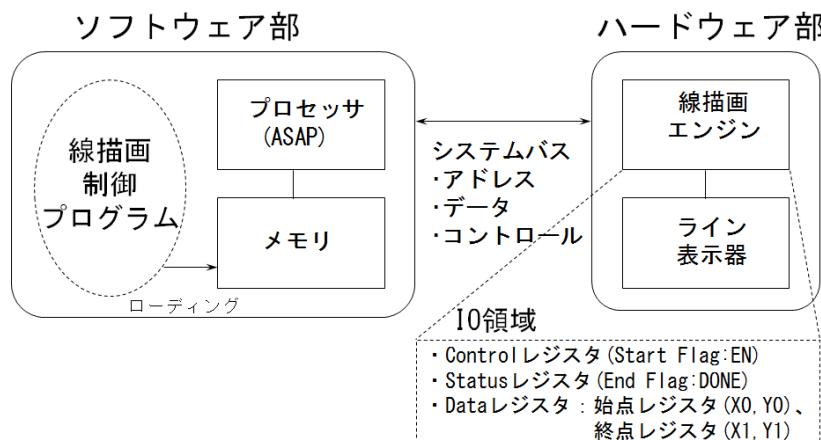

#### (1) 線描画システムの構成

線描画システムの構成を図 3.13 に示す。ソフトウェア部は、プロセッサとメモリで構成されている。メモリにロードされた線描画制御プログラムが、プロセッサ上で実行され一連の線の描画が行われる。ハードウェア部は、与えられた 2 点間の直線を高速に描画する線描画エンジンとライン表示器で構成されている。

この評価で使用するプロセッサとして、トップダウン協調設計システムを構築するときに開発した自製の 16 ビットの ASAP (Application Specific Adaptable Processor : アプリケーション志向適応型プロセッサ) を使用した[Sha96]。ASAP は、アプリケーションプログラムで必要とする CPU のビット幅とレジスタファイルの数をパラメータとして入力し、開発したプロセッサ高位合成ツール[Sha96]によって生成されるプロセッサである。今回の実験では、合成された命令セットモデルと RTL モデルを使用している。参考までに、16 ビット ASAP の規模は 5.3K ゲートで、線描画エンジン部のハードウェア規模は 1.5K ゲートである。

図 3.13において、始点の XY 座標は始点レジスタ ( $X_0, Y_0$ ) にセットされ、終点の XY 座標は終点レジスタ ( $X_1, Y_1$ ) にセットされる。その後、スタートフラグである EN がセットされると、線

図 3.13 線描画システムの構成

描画エンジンが起動される。線描画エンジンが1本の線を描画し終えたとき、DONE フラグがセットされる。

## (2) 適用結果と評価

提案したトップダウン協調検証フローに従い、プロセッサに依存しない高位言語モデル、プロセッサに依存する命令セットモデル、さらに RTL モデルを作成し、各々の評価を行なった。

プロセッサの命令セットモデル/RTL モデルと線描画エンジンの RTL モデルは同じシミュレーション環境で実行できることから、シングルプロセスでのシミュレーション環境を適用した。また、マルチプロセス環境でどの程度の性能が得られるかを評価するために、プロセッサの RTL モデルと線描画エンジンの RTL モデルとの間のコンポーネント論理バスインターフェースをプロセス間通信で実現する場合についても評価を行なった。

図 3.14 に線描画システムのコンポーネント論理バスの構成例を示す。

図 3.14 の組込みプログラム例に示すように、ソフトウェア部における高位言語モデルは、スタートアップイベント（ハードウェア部のモデル呼び出し）を取り除くといったわずかな修正で、命令セットモデルに置き換えることができた。

命令セットモデルから RTL モデルへの移行では、モデルを修正すること無しにハードウェア部の RTL モデルと結合ができた。今回の提案方式を使うことにより、検証ステージ間の移行を効率よく行うことができた。

協調シミュレーションの性能を、下記の 4 ケースで計測した。

- ① 高位言語モデル : (a)共有メモリ方式

- ② 命令セットモデル : (b)信号イベント方式

- ③ RTL モデル（シングルプロセス）: (b)信号イベント方式

- ④ RTL モデル（マルチプロセス）: (c)プロセス間通信方式

図 3.14 線描画システムのコンポーネント論理バス (CLB) モデルの構成例

協調シミュレーションの実行結果を表3.4に示す。この表では、RTLモデル（シングルプロセス）でのシミュレーション時間を1の単位として他の時間を正規化している。

高位言語モデルでの協調シミュレーションでは、ソフトウェアのC言語モデルとハードウェアのC言語の動作モデルと一緒にホストマシンで直接コンパイルし実行した。

命令セットモデルでは、C言語で書かれたASAP命令セットシミュレータとハードウェア部のRTLモデルを高速にシミュレーションできるTsutsujiサイクルベースシミュレータ[Cul93]を統合して、シングルプロセス環境で協調シミュレーションを行った。ASAPとTsutsujiを使った命令セットモデルの協調シミュレーションの実行例を図3.15に示す。

表3.4 線描画システムにおける協調シミュレーションの実行結果

| 検証<br>ステージ        | モデリング                      |            |             |            | 協調検証<br>相対性能<br>(③ RTL<br>モデル=1) |  |

|-------------------|----------------------------|------------|-------------|------------|----------------------------------|--|

|                   | SW                         |            | インターフェース    | HW         |                                  |  |

|                   | AP                         | プロセッサ      |             |            |                                  |  |

| ①高位言語<br>モデル      | Cモデル                       |            | (a)共有メモリ方式  | Cモデル       | 30                               |  |

| ②命令セット<br>モデル     | 微修正の<br>Cモデル<br>→ターゲットの機械語 | 命令セットモデル   | (b)信号イベント方式 | RTL<br>モデル | 1.3                              |  |

| ③<br>④ RTL<br>モデル |                            | RTL<br>モデル |             |            | 1                                |  |

|                   |                            |            | (c)プロセス間通信  |            | 1/370                            |  |

AP: アプリケーションプログラム

図3.15 線描画システムの協調シミュレーション実行例

RTL モデル（シングルプロセス）では、ASAP の RTL モデルとハードウェアの RTL モデルを使って Tsutsuji のシングルプロセス環境でシミュレーションを行った。

RTL モデル（マルチプロセス）では、ASAP 命令セットシミュレータと Tsutsuji を使い、Tsutsuji は、TCP/IP に基づくプロセス間通信を使って ASAP 命令セットシミュレータと同期をとりながらマルチプロセス環境で実行した。

高位言語モデルでは、すべてのシミュレーションは C 言語を使ってホストマシン上で直接実行される。RTL モデル（シングルプロセス）の協調シミュレーションと比べ、30 倍高速に実行できた。

命令セットモデルと RTL モデル（シングルプロセス）での性能は、プロセッサの回路規模とハードウェア部の回路規模に依存する。この例では、命令セットモデルの協調シミュレーション速度は RTL モデルと比べ、1.3 倍高速になった。今回の評価においては、ハードウェアは同じ条件でかつプロセッサモデルも高速なサイクルベースシミュレータが使われているため、性能においてそれほど差異が出なかったと考えられる。

RTL モデル（シングルプロセス）と RTL モデル（マルチプロセス）の性能を比較すると、プロセス間通信のオーバーヘッドが大きく、自製のプロセッサを使う場合は、シングルプロセスで協調シミュレーションできる検証環境を構築することが重要である。

本事例では、協調シミュレーションの検証ステージにおいて、シングルプロセスの環境において高速なシミュレーションが可能であり、ハードウェアとソフトウェアのインターフェースとしてコンポーネント論理バスを適用することにより、上流の高位言語モデルから、命令セットモデル、さらに RTL モデルまで、効率よく繰り返し実行できることがわかった。

### 3.5.4 映像圧縮処理システムによる評価

2 つ目の事例として、マルチメディア系の典型的な例である映像圧縮処理システムを対象とした。この分野では、いろいろな変化に対応でき、かつ最新の規格を盛り込むため、従来すべて ASIC で対応してきたものを、プロセッサ上で実行される組込みソフトウェアと専用のカスタム回路の組み合わせにより実現する方法がいろいろ研究されている [Tho93] [Hol96]。コスト・性能・消費電力・柔軟性等の面からハードウェアとソフトウェアによるバランスのとれた組込みシステムを実現する必要があるが、規模が拡大し複雑になるほど、評価・検証・デバッグ環境として、ハードウェアとソフトウェアによるトップダウン協調検証が重要となる。

本事例では調達した 32 ビットプロセッサ（M32R/D）を使った映像圧縮処理システムを対象に、システムレベルシミュレーションから、協調シミュレーション、協調エミュレーションまで、提案したトップダウン協調検証手法を適用し評価を行なった。設計の上流から下流までの 4 つの検証ステージ（システムモデル、高位言語モデル、命令セットモデル、実チップモデル）において、実用レベルで効率よく繰り返し検証できるかの評価が中心である [Seo98][安田 99]。

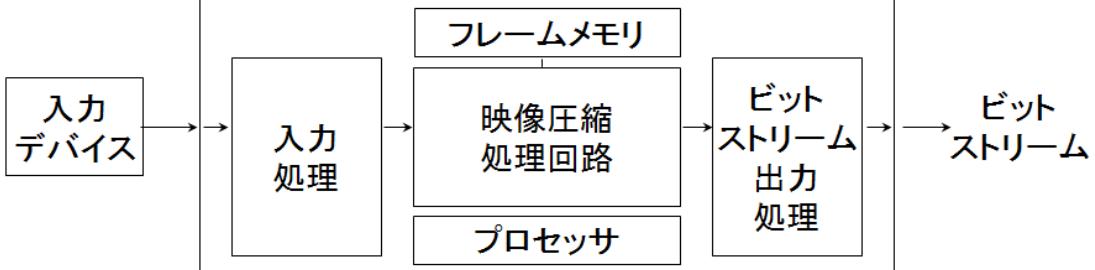

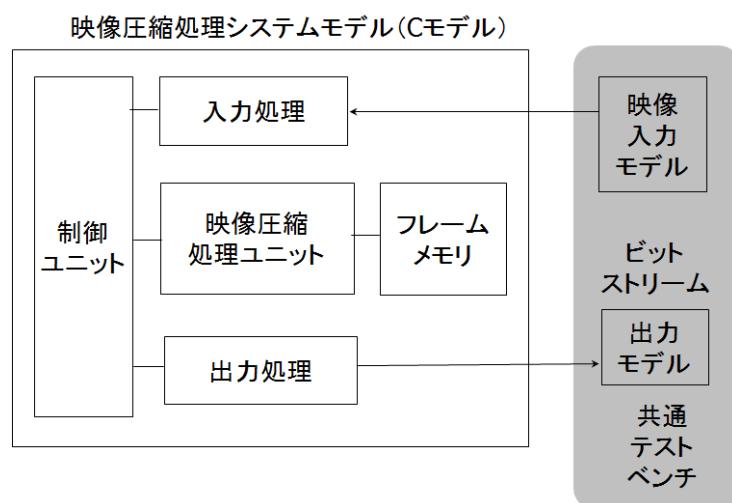

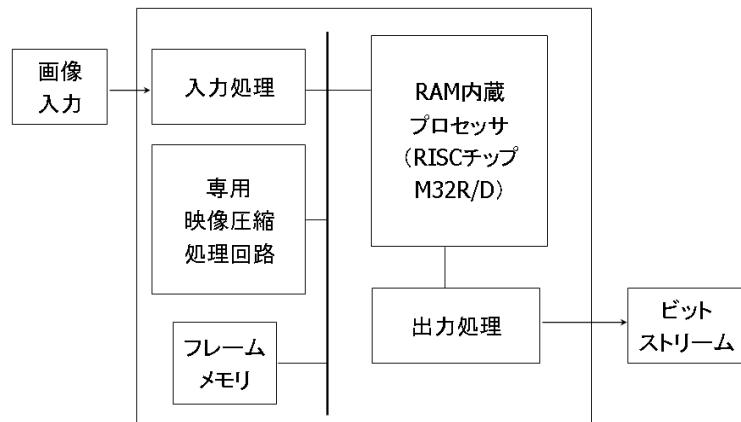

## (1) 映像圧縮処理システムの構成

映像圧縮処理システムの構成を図 3.16 に示す。主な機能ブロックは、システム全体を制御するプロセッサ(RISC)、映像データを圧縮処理する専用信号処理回路、入力デバイスからの映像信号を処理する入力処理回路、圧縮した映像データをビットストリームとして出力するビットストリーム出力処理回路、映像データを保持するフレームメモリ回路、プログラムを格納するプログラムメモリ回路（図には記載していない）等である。この中で、映像データを圧縮処理する専用信号処理回路については、製品目標に応じて、ハードウェアとソフトウェアによる組み合わせにより実現されることになる。また、圧縮伸張で新しいアルゴリズムを適用する場合には、アルゴリズムの妥当性を出来るだけ早い段階で実機に近い環境で人間の感性により確認する必要がある。

## (2) 検証ステージ

図 3.17 に提案したトップダウン協調検証手法において今回適用した検証ステージを示す。上流から①アルゴリズム評価のためのシステムレベルシミュレーション、②機能評価のためのハードウェアとソフトウェアによる高位言語モデル協調シミュレーション、③性能評価のためのハードウェアとソフトウェアによる命令セットモデル協調シミュレーション、及び、④実機に近い環境での評価のためのハードウェアとソフトウェアによる実チップモデル協調エミュレーションの 4 つの検証ステージを適用した。なお、RTL モデルとゲートモデルは、性能が遅くなることから対象としなかった。また、ハードウェアとソフトウェアのインターフェースにコンポーネント論理バスアーキテクチャを適用すると共に、外部入出力を模擬した共通テストベンチを開発して、各検証ステージ間で一貫した効率の良い協調検証環境の実現を図った。

- ① システムモデル：図 3.17 の①に示すように、対象アプリケーションを実現するためのアルゴリズムやアーキテクチャを評価するために、システム全体を C 言語によりモデル化を行い、システムレベルシミュレーションにより評価を行う。

- ② 高位言語モデル：図 3.17 の②に示すように、ハードウェアとソフトウェアのインタフ

図 3.16 映像圧縮処理システムの構成例.

図 3.17 トップダウン協調検証システムにおける検証ステージ

エースが確定し、高位言語（例えばC言語）で記述された組込みソフトウェアとハードウェア（Cモデル）による協調シミュレーションにより、分担機能の検証・評価を行う。組込みソフトウェアは、ターゲットとなるプロセッサとは独立に、検証を行うホストマシン上で直接実行することで高速な処理が可能となる。

**③ 命令セットモデル**：図3.17の③に示すように、高位言語で記述されたアプリケーションプログラムをターゲットとなるプロセッサの機械語にコンパイルし、プロセッサの命令セットモデルと、ハードウェアのRTLモデルによる協調シミュレーションにより、実行サイクルの算出による性能評価を含めてより詳細な検証を行う。プロセッサは社内調達のプロセッサ（M32R/D）を使い、キャッシュやパイプライン動作まで模擬できる命令セットシミュレータを使用する。

**④ 実チップモデル**：図3.17の④に示すように、マルチメディアの世界では、人間を対象にした映像・音声処理が中心となることから、感性による評価が重要になる。このため、実時間に近い環境での評価が必要であり、システムエミュレータによる協調エミュレーションが重要となる。今回の協調エミュレーションでは、ターゲットのプロセッサ（M32R/D）の RTL モデルが入手できなかったため、実チップモデルを利用する。

このように4つの検証ステージをトップダウンに実行し、各検証ステージで発見された不具合を前の設計フェーズにフィードバックすることにより、早期にシステム全体の品質の評価が可能となる。

### (3) 協調検証の実現方法

各検証ステージでの実現方法について述べる。

#### ① システムレベルシミュレーション

図 3.18 にシステムレベルシミュレーションの例を示す。

システム全体をC言語によりモデル化し、シミュレーションを行うホストマシンでコンパイルして実行することにより、高速なシミュレーション環境を実現できる。また、仮想計測器環境をサポートする共通テストベンチの構築により、実際の画像データを活用して検証できる環境を提供している。

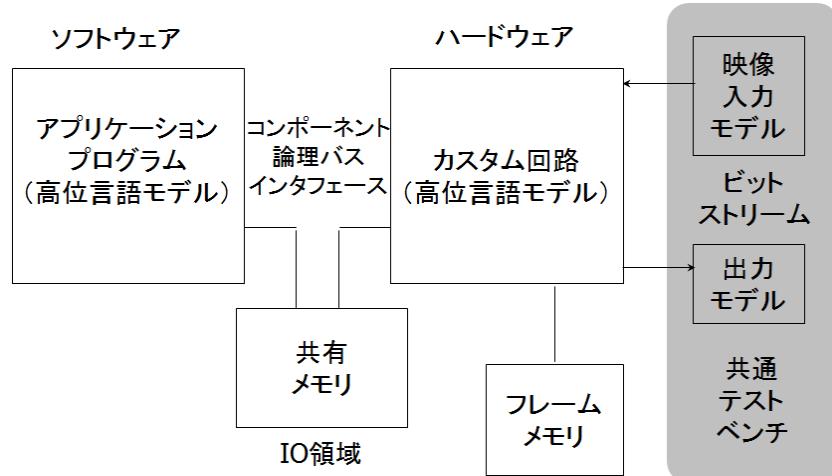

#### ② 高位言語モデルによる協調シミュレーション

図 3.19 に高位言語モデルによる協調シミュレーションの例を示す。

図 3.18 システムレベルシミュレーション.

図 3.19 高位言語モデルによる協調シミュレーション

アプリケーションを記述したCプログラム（高位言語モデル）を、ホストマシンの機械語にコンパイルして直接実行することにより、プロセッサに依存せずに高速にシミュレーションができる。カスタム回路部も、C言語で記述された高位言語モデルであり、同じようにコンパイルして、シングルプロセス上で高速にシミュレーションができる。コンポーネント論理バスアーキテクチャによるデータのやり取りは、カスタム回路部（専用映像圧縮回路）のレジスタやメモリを、メモリアドレス空間のIO領域に割り付けて行う。実現方法としては、IO領域を共有メモリに定義し、ここを双方でアクセスすることによりデータの送受を行う。システムモデルによるシミュレーションと同一の共通テストベンチを活用できる。

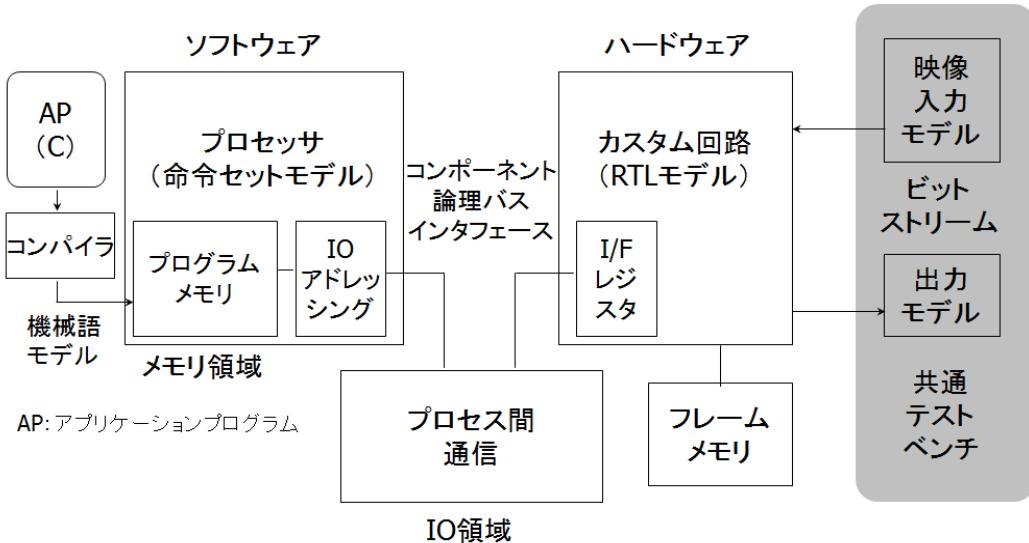

### ③ 命令セットモデルによる協調シミュレーション

図3.20に命令セットモデルによる協調シミュレーションの例を示す。

対象となるアプリケーションを記述したCプログラムをターゲットとなるプロセッサの機械語にコンパイルして、そのプロセッサの命令セットシミュレータによりインタプリティブに実行する。カスタム回路部のハードウェアはRTレベルで表現し、サイクルベースでシミュレーションを行う。両方のシミュレータがシングルプロセス上で実行できないので、コンポーネント論理バスインターフェースをプロセス間通信の仕組みで実現し、データの送受を行う。プロセッサの命令セットモデルをキャッシュやパイプライン動作まで模擬することにより、組込みソフトウェアの実行ステップを正確に把握でき、システムの性能を評価することが可能となる。システムモデルによるシミュレーションと同一の共通テストベンチが利用できる。

図3.20 命令セットモデルによる協調シミュレーション

図 3.21 実チップモデルによる協調エミュレーション

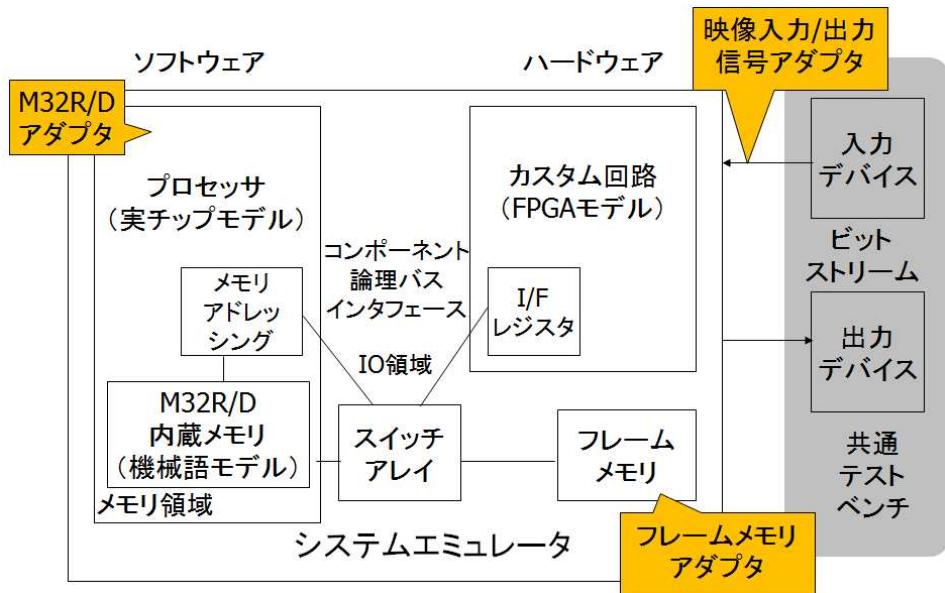

#### ④ 実チップモデルによる協調エミュレーション

図 3.21 に実チップモデルによる協調エミュレーションの例を示す。

協調エミュレーション環境を以下のように構築する。

- ・プロセッサのモデルである実チップを搭載する M32R/D アダプタを作成する。

- ・アプリケーションを記述した C プログラムはターゲットとなるプロセッサの機械語にコンパイルして、バイナリーデータを M32R/D 内蔵メモリに格納する。

- ・カスタム回路の RTL モデルを論理合成し、FPGA に分割してマッピングする。

- ・映像データを格納するフレームメモリアダプタを作成する

- ・部品間の接続情報は、プログラマブルスイッチアレイ素子にマッピングする。

- ・アナログ映像信号をデジタル信号に A/D 変換する映像入力信号アダプタや、デジタル信号を外部のディスプレイに表示するアナログ信号に D/A 変換する映像出力信号アダプタを作成し、リアルな共通テストベンチを実現する。

#### (4) 適用内容と評価手順

映像圧縮処理システムにトップダウン協調検証手法を適用し、その効果を確認した。図 3.22 に適用した映像圧縮処理システムのブロック図を示す。プロセッサの制御のもとに、アナログ映像信号入力をデジタル信号に変換し、一旦フレームメモリに格納し、映像圧縮処理回路により動き予測を行い映像データの圧縮を行う。その後、ソフトウェアにより、符号化による圧縮を行い、仕様で規定されたビットストリームの信号列に変換する。

この事例では、プロセッサとして DRAM 内蔵 RISC プロセッサ(M32R/D)を社内調達した。命令セットシミュレータは提供されたが、RTL モデルは入手できなかった。映像圧縮処理専用回路としてプロセッサの指示で動作を行う映像圧縮プロセッサを開発した。専用

図 3.22 映像圧縮処理システムのブロック図

回路の規模は 50k ゲートであった。映像処理用に専用のフレームメモリを使い、システム制御のソフトウェアは M32R/D 内蔵の RAM を使って実行した。

トップダウン協調検証手法で実施した評価の手順について、以下に説明する。

### ① システムレベルシミュレーション

映像圧縮のアルゴリズムをすべて C 言語で記述し、アルゴリズムによる映像圧縮率と映像品質及び演算量の評価を行った。

### ② 高位言語モデルによる協調シミュレーション

ソフトウェア部分もハードウェア部分も C 言語によりモデル化を行った。ハードウェア部を制御するレジスタやデータを格納するバッファ群を共有メモリ空間に割り付けることにより、ハードウェアとソフトウェア間のデータのやりとりを実現した。すべて、C プログラムで表現され、ホストマシンで直接実行できるために高速にシミュレーションを行うことができた。ハードウェアとソフトウェアによる機能的な分担の検証を行なった。

### ③ 命令セットモデルによる協調シミュレーション

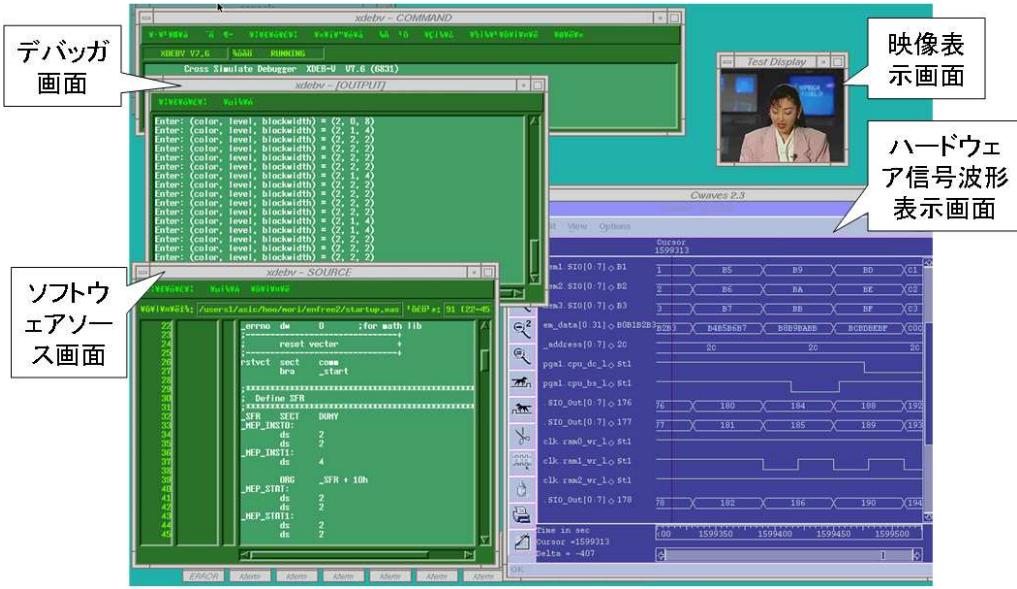

C 言語で記述された組込みソフトウェアを調達したプロセッサ M32R/D の機械語にコンパイルし、ターゲットとなるプロセッサのキャッシュやパイプライン動作の模擬を行う命令セットシミュレータを使ってインタプリティブに実行した。RT レベルでモデル化されたハードウェアはサイクルベースシミュレータで実行した。両方のシミュレータをシングルプロセスで実行できないため、プロセス間通信を使ってデータの送受を行なった。命令セットモデルによる協調シミュレーションの実施例(Tsutsuji を使用)を図 3.23 に示す。実行サイクルによる性能評価を中心に検証を行った。

図 3.23 映像圧縮処理システムの協調シミュレーション実行画面例

#### ④ 実チップモデルによる協調エミュレーション

システムエミュレータ MP4[Apt96]上に、作成したプロセッサの M32R/D アダプタ、フレームメモリアダプタ、および、映像入力/出力信号アダプタを搭載した。プログラムはプロセッサ M32R/D の内蔵メモリに格納した。映像圧縮処理回路の論理回路を 4 石の FPGA（最大 10k ゲート搭載可能）にマッピングし、これらの部品間の接続情報をプログラマブルスイッチアレイ(FPIC)にマッピングした。当初 1MHz で動作させ、最終的に 4MHz までチューニングを行い、実機に対して 1/5 の速度でエミュレーションを可能とした。実際の映像を入力しながら、動きを伴った映像圧縮処理の評価を可能とした。協調エミュレーションの実施例を図 3.24 に示す。

当初1MHz→チューニングして4MHzで動作

図 3.24 映像圧縮処理システムの協調エミュレーションの実行例

## (5) 適用結果と評価

映像圧縮処理システムに適用したトップダウン協調検証の実行結果と、繰り返し検証の効率化の評価について説明する。

### ① トップダウン協調検証の実行結果と評価

トップダウン協調検証の実行結果を表3.5に示す。表3.5では、実機での速度を1の単位として、それぞれのシミュレーション速度を相対的に示している。

- ・システムモデルでは、すべてホストマシン上で直接実行できることから、ホストマシンの性能に依存するが、実機の1/12.5という高性能で評価でき、アルゴリズムの評価を繰り返し行うのに有効であった。

- ・高位言語モデルでの協調シミュレーションは実機の1/125の性能で評価できたので、ハードウェアとソフトウェアによる分担機能の評価を繰り返し行うのには十分に効果があった。

- ・命令セットモデルでの協調シミュレーションでは、クロック単位のタイミングを考慮したサイクルベースの協調シミュレーションであったが、プロセス間通信のオーバーヘッドのため、性能は実機の1/250,000となった。繰り返し実行するには無理があるが、正確な性能評価をすることができた。

- ・実チップモデルによる協調エミュレーションは実機の1/10の性能で、人間の目視による動画の画質評価と詳細な性能評価として、大変有効であった。また、組込みソフトウェアのコンカレントなデバッグが可能となり、システム全体の開発期間短縮に貢献できた。

表3.5 映像圧縮処理システムのトップダウン協調検証の実行結果

| 検証<br>ステージ    | モデリング                          |              |             | 協調検証<br>相対性能<br>(実機=1)            |  |

|---------------|--------------------------------|--------------|-------------|-----------------------------------|--|

|               | SW                             |              | HW          |                                   |  |

|               | AP                             | プロセッサ        |             |                                   |  |

| ①システム<br>モデル  | Cモデル                           |              |             | 0.08<br>実機の<br>1/12.5             |  |

| ②高位言語<br>モデル  | Cモデル                           | 共有メモ<br>リ方式  | Cモ<br>デル    | 0.008<br>実機の<br>1/125             |  |

| ③命令セッ<br>トモデル | Cモ<br>デル→タ<br>ーゲッ<br>トの機<br>械語 | 命令セット<br>モデル | プロセス<br>間通信 | $4 \times 10^{-6}$<br>オーバ<br>ヘッド大 |  |

| ④実チップ<br>モデル  |                                | 実チップ<br>モデル  | RTL<br>モデル  | 0.1<br>実機の<br>1/10                |  |

| 実機            | 実チップ                           | メモリマッ<br>プ方式 | FPGA<br>モデル | ASIC<br>1(20MHz)                  |  |

AP: アプリケーションプログラム

## ②繰り返し検証の効率化の評価

繰り返し検証の効率化に関する定性的な評価を図 3.25 に示す。

繰り返し検証が実用レベルで効果を発揮するためには、検証時間そのものが実用に耐えられる必要がある。また、各検証ステージでの検証環境の準備が効率良く行なえること、各検証ステージでのモデリングが効率良く行なわれることが必要である。

### (a) 検証環境の準備時間

シミュレーション環境の統合により検証環境の準備時間が減少した。また、共通テストベンチの適用により、協調シミュレーション（高位言語モデル）以降の検証ステージで同じテストデータが使えることから準備作業の軽減につながった。

### (b) モデリングの時間

ハードウェアとソフトウェアのインターフェースとしてコンポーネント論理バスアーキテクチャを採用することにより、インターフェース部分のモジュール化が可能になり、協調シミュレーション（命令セットモデル）以降のモデリング時間を軽減できた。

## 3.6 考察

自製したプロセッサ（ASAP）を使用した線描画システムと、調達したプロセッサ（M32R/D）を使用したマルチメディア系の組込みシステムである映像圧縮処理システムを対象に、提案したトップダウン協調検証手法を適用した。今回提案したトップダウン協調検証手法適用による効果を図 3.26 に示す。

図 3.25 繰り返し検証の効率化

図 3.26 トップダウン協調検証手法の適用による効果

実機評価が必要な独創的な組込みシステム製品開発を行う場合には、以下の手順で効率よくタイムリーに評価・検証を行う必要がある。

- (1) 独創的なアルゴリズムなどを設計の上流でシステムレベルシミュレーションにより繰り返し評価・検証を行う。

- (2) ハードウェアとソフトウェアの組み合わせで実現したシステムの機能と性能について評価・検証を行う。

- (3) 実機に近い環境で、実動作による評価・検証や人間の感性による評価を行う。満足解が得られない場合は、前のステージに戻って設計を見直して、繰り返し評価・検証を行う。

本研究では、これらの課題を実現するために、従来各検証ステージ毎にバラバラであった検証環境を統合し、共通テストベンチを適用した。また、ハードウェアとソフトウェアとのインターフェースとしてコンポーネント論理バスアーキテクチャを採用し、協調シミュレーションから協調エミュレーションまでの各検証ステージに適用した。また、協調検証ではプロセッサのモデル化が重要になることから、自製の場合と調達の場合における各検証ステージでのモデルの実現方法を明確にした。

2 件の事例に適用した結果をまとめると、以下の効果を得ることができたと考えられる。

- (1) システムレベルシミュレーションでは、高速なシミュレーションにより、繰り返し効率よく評価・検証ができた。

- (2) (1)の評価・検証された機能をハードウェアとソフトウェアで分担し、インターフェースとしてコンポーネント論理バスアーキテクチャを採用し、これ以降の検証ステージに

すべて適用した。インターフェースの実装方法は、いろいろ存在したが、実装特有な変更部分は少なく、上位から下位のステージへの移行をそれぞれ容易に行うことができた。

- (3) 高位言語モデルの協調シミュレーションでは、インターフェースを共有メモリ方式で実装し、ハードウェアとソフトウェアとともに高位言語（C）でモデル化し、ホストマシンでコンパイルしてシングルプロセスで実行することで高速なシミュレーションを実現できた。共通テストベンチとの組み合わせで、繰り返し効率よく評価・検証することができた。

- (4) 命令セットモデルの協調シミュレーションでは、インターフェースをプロセス間通信でしか実現できなかったために、オーバーヘッドが大きかったが、ハードウェアは RTL モデルでソフトウェアは機械語モデル（プロセッサは命令セットモデル）により、大まかな性能評価をすることができた。頻繁な繰り返し実行は無理があるが、次の協調エミュレーションへの移行は、インターフェース部分の変更が少なく容易に移行することができた。

- (5) 協調エミュレーションでは、プロセッサを実チップモデルまたは FPGA モデルにマッピングし、残りのハードウェアを FPGA モデルにマッピングすることにより、実機に近い環境で繰り返し効率よく評価・検証することができた。

以上により、提案したトップダウン協調検証手法は、独創的な組込みシステム製品の開発を効率よく評価・検証することに貢献できると判断できる。

自製のプロセッサでは、プロセッサのモデルとハードウェア部のモデルをシングルプロセス上で実行することが可能で、協調シミュレーションを効果的に実現可能である。それに対して調達したプロセッサではモデルの入手が困難な場合が多く、命令セットモデルを入手できた場合でも、プロセッサの命令セットシミュレータとハードウェアモデルのシミュレータをマルチプロセスで動かす必要がある場合が多い。今回の事例では、コンポーネント論理バスでのデータ授受にプロセス間通信を使ったが、そのオーバーヘッドは非常に大きく実用上大きな課題である。協調シミュレーションではシングルプロセスで実行可能な環境を作り込むことが重要であり、同じシミュレータに組み込めるプロセッサの命令セットモデルや RTL モデルの入手が必須である。

### 3.7 まとめ

マルチメディア系や制御系のように実機評価が必要な組込みシステムの開発に対して、検証環境を統合し、共通テストベンチを適用し、ハードウェアとソフトウェアのインターフェースとしてコンポーネント論理バスアーキテクチャを採用したトップダウン協調検証システムを提案した。新しいアイデアのアルゴリズムをシステムレベルシミュレーションで評価・検証を行う検証ステージから、ハードウェアとソフトウェアに分割して協調シミュ

レーションにより機能と性能の評価・検証を行う検証ステージを経て、実機に近い環境で協調エミュレーションにより実機動作と人間の感性による評価・検証を行う検証ステージまで、繰り返し効率よく検証できることを示した。このようなトップダウン協調検証手法を取り入れるこれにより、新しい独創的な組込みシステムを、各検証ステージで不具合を取り除きながら、効率よく高品質に開発できると考える。

組込みシステムの大規模化・複雑化は今後も進むと予想される。設計の課題については、再利用可能な資産（IP）の活用とIPを統合しやすくするプラットフォームベース設計の適用、さらに抽象度の高い高位言語の採用と高位合成ツールの適用により改善されてきていく。それに対して、検証の課題はIPを含んだシステム全体をものづくりの前に動作させて評価・検証が必要となることから、規模の拡大に伴い難しさが増大する傾向にある。そのために、本研究で提案したような、ハードウェアとソフトウェア間のインターフェースを統一して、それぞれの機能をモデル化することにより、より効率のよい検証環境を実現することは有用なアプローチと考えられる。

特に、IoT時代が到来し、組込みシステムが通信ネットワークでクラウドに接続され、クラウド上のアプリケーションと連携してサービスを提供する大きな変革期を迎えており、如何に価値を創造するかが求められている。この価値を創造するためのアプローチとして「デザイン思考」が注目されており、その骨子はユーザの目線に立って「プロトタイピングによる迅速な繰り返し評価」であると言われている。今回提案した「トップダウン協調検証手法」は、効率良くシステムの評価検証を繰り返すという観点で、IoT時代でも有効な手法と考えられる。

## 第4章 複合領域での教育手法をベースとした組込みシステム技術者教育の提案と実践評価

### 4.1 はじめに

既に述べてきたように、1990年代後半から2000年代において組込みシステムはデジタル情報家電や通信機器、自動車関連機器を含めて基幹製品のかなりの部分を占めるようになってきた。このような組込みシステムは、ハードウェアとソフトウェアを組み合わせてそれぞれの分野に適した製品として実現されている。半導体技術やデジタル化の進展にともない、組込みシステムは、異なる技術を統合してシステム化が行われ、ますます大規模化・複雑化してきている。複数の技術を組み合わせて、応用分野に最適なシステムを実現することがますます重要になってきており、これらを実現できる技術者としてシステムアーキテクトが求められている。

本章では、1990年代後半から2000年代を念頭に、4.2節で組込みシステムに必要なスキルと組込みシステム技術教育の現状について説明し、4.3節で組込みシステム技術教育の問題点を論じる。次に、4.4節で組込みシステム技術者の教育手法を4つの視点から提案し、4.5節で提案に基づいて開発したカリキュラムの概要と実践評価した結果について論じる。4.6節で考察とまとめを行う。さらにIoT時代と言われる2017年の今の視点からの考察も行なう。

### 4.2 組込みシステムにおける必要なスキルと組込みシステム技術教育の現状

#### 4.2.1 組込みシステム製品開発で必要となるスキル

第2章の2.6節で説明したように、経産省・IPAでは、組込みソフトウェア開発力強化を狙いとして、SECを設立し、2005年に「組込み技術システム標準」ETSSを策定した。ETSSはスキル標準、キャリア標準、教育研修標準から構成されている。

スキル標準のフレームワークでは、必要とするスキル群を3つのスキルカテゴリ（技術要素、開発技術、管理技術）に分類し、スキル粒度として最上位の抽象的な第一階層からより詳細な第三階層まで階層的に展開し、最下層のスキルに対して必要なスキルレベル（初級、中級、上級、最上級）を設定している。

組込みスキル標準ETSSをベースに組込みシステム開発に必要となるスキル体系をまとめたものを図4.1に示す。図4.1の左側に、ETSSの3つのスキルカテゴリである技術要素、開発技術、管理技術を示す。図4.1の右側に、ETSSのスキル体系に対応した、本論文の取り組みの位置づけを示す。プロダクトはETSSの技術要素に、プロセスは開発技術に、プロジェクトは管理技術に対応させている。

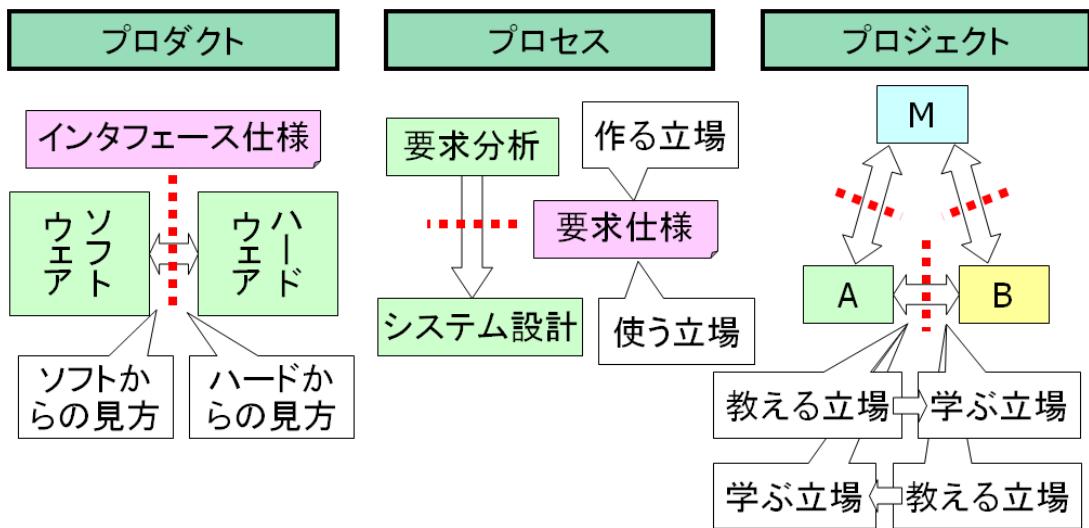

図 4.1 組込みシステム開発に必要なスキル体系と本論文での対応