## 科学技術計算を対象とした大規模再構成可能データ パスの性能評価

片岡, 広志

九州大学大学院システム情報科学府

本田, 宏明

財団法人九州先端科学技術研究所

Mehdipour, Farhad

Research Institute for Information Technology, Kyushu University

井上, 弘士

九州大学大学院システム情報科学研究院

他

<https://hdl.handle.net/2324/12509>

---

出版情報：電子情報通信学会技術研究報告, CPSY2008-35. 108 (273), pp.35-40, 2008-10-31. 電子情報

通信学会

バージョン：

権利関係：

# 科学技術計算を対象とした大規模再構成可能データパスの性能評価

片岡広志<sup>†</sup> 本田宏明<sup>††</sup> FarhadMehdipour<sup>†††</sup> 井上弘士<sup>††††</sup> 村上和彰<sup>††††</sup>

† 九州大学大学院システム情報科学府 〒 819-0395 福岡市西区元岡 744

†† 財団法人九州先端科学技術研究所 〒 814-0001 福岡市早良区百道浜 2-1-22 福岡 SRP センタービル 7F

††† 九州大学情報基盤研究開発センター 〒 812-8581 福岡市東区箱崎 6-10-1

†††† 九州大学大学院システム情報科学研究院 〒 819-0395 福岡市西区元岡 744

E-mail: †{kataoka,dahon}@c.csce.kyushu-u.ac.jp, ††farhad@cc.kyushu-u.ac.jp,

†††{inoue,murakami}@i.kyushu-u.ac.jp

あらまし 最近，要求メモリバンド幅を抑えつつも高性能な科学技術計算を可能とする，大規模再構成可能データパス (LSRDP) が提案された。本稿ではこの LSRDP について，種々のメモリバンド幅のもとでの性能評価を行った。対象アプリケーションは，1 次元の熱伝導方程式，2 次元の Poisson 方程式，2 電子積分計算の 3 種類である。その結果，熱伝導方程式，2 電子積分計算については，汎用プロセッサのみでの計算に比較しだいに性能向上を果たしたが，Poisson 方程式については逆に実行時間が増加した。これは，主記憶から LSRDP へのバースト転送利用のために LSRDP 計算にて行っている主記憶上の入出力データの並び替えステップが，実行時間の大半を占めてしまうからである。

**キーワード** 大規模再構成可能データパス，熱伝導方程式，Poisson 方程式，2 電子積分計算

## Performance Evaluation of a Large Scale Reconfigurable Data-Path Utilized for Scientific Application

Hiroshi KATAOKA<sup>†</sup>, Hiroaki HONDA<sup>††</sup>, Farhad MEHDIPOUR<sup>†††</sup>, Koji INOUE<sup>††††</sup>, and Kazuaki MURAKAMI<sup>††††</sup>

† Department of Informatics, Graduate School of Information Science and Electrical Engineering, Kyushu University Motoka, 744, Nishi-ku, Fukuoka 819-0395 Japan

†† Institute of Systems, Information Technologies and Nanotechnologies Fukuoka SRP Center Building 7F, 2-1-22, Momochihama, Sawara-ku, Fukuoka, 814-0001, Japan

††† Research Institute for Information Technology, Kyushu University Hakozaki, 6-10-1, Higashi-ku, Fukuoka, 812-8581, Japan

†††† Division of Informatics, Graduate School of Information Science and Electrical Engineering, Kyushu University Motoka, 744, Nishi-ku, Fukuoka 819-0395 Japan

E-mail: †{kataoka,dahon}@c.csce.kyushu-u.ac.jp, ††farhad@cc.kyushu-u.ac.jp,

†††{inoue,murakami}@i.kyushu-u.ac.jp

**Abstract** Recently, Large Scale Reconfigurable Data Path (LSRDP) processor has been proposed for the reduction of required memory bandwidth in a high performance scientific computing. In this paper, performance evaluations of LSRDP at various memory bandwidths have been demonstrated for 1-dimensional Heat and 2-dimensional Poisson partial differential equations, and for Electron Repulsion Integral (ERI) calculation as target benchmark applications. Executions times for Heat and ERI applications were decreased compared to original execution by the general purpose processor. On the other hand for Poisson application, execution times were increased, since data sorting steps, which are needed for burst transfer from main memory to LSRDP, consume great amount of execution time.

**Key words** Large Scale Reconfigurable Data Path processor, Heat equation, Poisson equation, Electron Repulsion Integral

## 1. はじめに

近年, 科学技術計算などの分野で, HPC ( High Performance Computing ) の要求が高まっている. そこで, 本研究室では科学技術計算に特化したアクセラレータとして大規模再構成可能データパス ( LSRDP : Large Scale Reconfigurable Data Path ) を提案している [1], [2] . LSRDP は, チップ上に多数の演算器を配置し, それらをプログラマブルなネットワークで接続した構成を探る. 演算器の出力を直接他の演算器の出力とすることが可能であり, 大量の中間結果が生じるような複雑な計算においても, 中間結果を主記憶に格納することなく実行できる.

しかしながら, 具体的なベンチマークとしてのアプリケーションを対象とした LSRDP の定量的な性能評価はいまだに行われていない.

本稿では, 2 階定数係数偏微分方程式と 2 電子積分計算をベンチマークとして用いた場合の LSRDP の定量的な性能評価を行う事を目的とする. 最初に LSRDP の構成と動作から, 汎用プロセッサ ( GPP: General Purpose Processor ) と LSRDP を合わせたシステムの性能を予測する性能モデル式を構築する. 次にその環境に従ってベンチマークを用いて性能評価を行う. 以下, 第 2 章では大規模再構成可能データパスについて説明する. 第 3 章で LSRDP の使用の際の性能モデル式を提案する. また, 第 4 章では今回使用するベンチマークについて概説し, 第 5 章で LSRDP の性能評価実験を行う. そして, 第 6 章でまとめと今後の課題について述べる.

## 2. 大規模再構成可能データパス

### 2.1 LSRDP アーキテクチャ

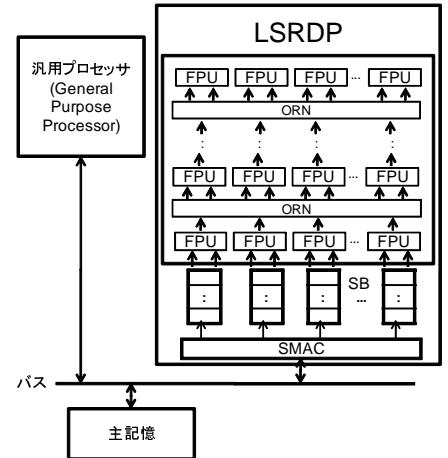

GPP と主記憶にバス経由で LSRDP を付加したシステムの概観を図 1 に示す. LSRDP は Floating Point Unit ( FPU ) を 2 次元アレイ状に配置した構成となっており, ORN は横に並んだ FPU アレイ ( 以後, 行と呼ぶ ) を接続するネットワークである. LSRDP は科学技術計算を対象とするため, 演算器は FPU で構成されている. また, ORN はデータフローを自由に変更できるクロスバスイッチ等で構成し, FPU の演算内容と ORN の接続情報を再構成可能としている. ORN を介して, ある FPU の出力を直接他の FPU の入力とすることが可能であるため, データ依存関係のある計算の中間結果をメモリに格納することなく計算可能である. LSRDP はデータ入力用の SB ( Streaming Buffer ) と, SB への入出力を制御するコントローラ ( SMAC : Streaming Memory Access Controller ) を持つ. SB は FIFO 動作のバッファであり, FPU と ORN で構成されるデータバスへ入力を供給し, 出力を受け取る. SMAC は主記憶と SB 間のデータ転送を制御し, データの転送はオフチップのバスを介して行う. LSRDP のアーキテクチャは FPU を 2 次元アレイ状に配置した構成となっているが, 各 FPU は加減算もしくは乗算のうちいずれか 1 つを持つ. また, ORN によるデータ転送には以下に示す制約が存在する.

- ORN は隣接行間のみデータ転送が可能である

図 1 大規模再構成可能データパス ( LSRDP ) を含むシステムの概観

- 非隣接行間では, それらの間に存在する FPU を利用してデータ転送を行う

- 同一行内のデータ転送は不可能である

- データ転送を行う方向はすべて一意である.

LSRDP への入力データの供給は SB により行われる. あらかじめ GPP により入力データを主記憶上に整列しておき, 主記憶のバーストアクセスの機能を利用してすることで, アドレス指定に必要な時間と演算資源の節約を図っている.

LSRDP を付加したシステムでアプリケーションを実行するには, ソースコードを LSRDP で実行する部分と GPP で実行する部分に分割し, それぞれコンパイルする必要がある. LSRDP 部分のコードは元のプログラムよりデータフローグラフ ( DFG : Data Flow Graph ) を何らかの方法で抽出し, マッピングツールを使用して LSRDP に対するマッピングデータへと変換する. なお, アプリケーション内で LSRDP で実行する部分はプログラマが決定するが, プログラマは GPP と LSRDP 上の実装に最適なアルゴリズムを探索する必要がある.

### 2.2 LSRDP の動作

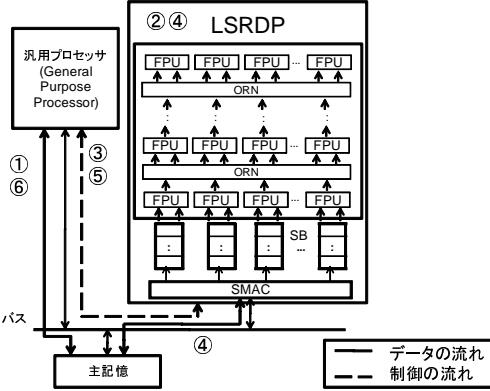

LSRDP は GPP に対するコプロセッサとして動作する. GPP と LSRDP がオーバーラップ実行しないとすると, その動作は以下のようになる ( 図 2 ).

- ( 1 ) GPP が LSRDP に入力するデータを主記憶中で整列

- ( 2 ) LSRDP を再構成

- ( 3 ) GPP が LSRDP に演算の開始を指示

- ( 4 ) LSRDP が演算を実行

- ( 5 ) LSRDP が演算の終了を GPP に報告

- ( 6 ) GPP が LSRDP の出力データを主記憶内で整列

上記 ( 4 ) の LSRDP での演算には, 入力データの読み込みと, 出力データの書き込みが含まれる. LSRDP は主記憶とバーストアクセスによりデータ転送を行うので, 演算を実行させる前後に 1, 6 において主記憶内のデータを整列する必要がある. また, LSRDP は 1 クロックサイクルごとにパイプライン処理を行う. このとき, 入力されるデータの集合が SB 上に存在する限り LSRDP はストールせずに演算を実行する. しかしながら, SB 上に入力されるデータの集合が存在しない場合は, SB

図 2 LSRDP を含むシステムの動作

に入力が準備されるまで演算をストールさせる。また、パイプライン処理の最後においてはすべての出力を吐き出させるために、あらかじめ出力を求めない空の入力を準備しておく。

### 2.3 LSRDP の利用による要求メモリバンド幅の抑制

一般的なアクセラレータは、大量の演算器を搭載し並列に動作させることで高い演算性能を実現している。したがって、演算実行時には演算器 1 つに対して 2 つのデータを入力として与える必要がある。更に演算器ごとに異なる入力データを与えていため、演算器の個数に比例して要求するメモリバンド幅が大きくなり、アクセラレータの高い演算性能を抑えてしまう要因となる。これに対し、データフロー型の計算方式を採用している LSRDP では、主記憶から入力を受け取る演算器の数は少数である。その他の演算器はアプリケーション中のデータ依存関係を利用し、他の演算器の出力結果を直接入力している。したがって、要求メモリバンド幅を抑えることが可能となる。

### 3. 性能モデリング

GPP と LSRDP がオーバーラップ実行しないとすると、アプリケーションの実行時間  $ET$  は、GPP で実行する部分の実行時間  $ET_{GPP}$ 、LSRDP で実行する部分の実行時間  $ET_{LSRDP}$ 、LSRDP を利用する際に発生するオーバーヘッド  $ET_{oh}$  の和で表される

$$ET = ET_{GPP} + ET_{LSRDP} + ET_{oh} \quad (1)$$

$ET_{LSRDP}$  を演算時間  $T_{cal}$ 、メモリアクセスによりストールした時間  $T_{st}$  の和で表す。

$$ET_{LSRDP} = T_{cal} + T_{st} \quad (2)$$

アプリケーションは GPP で実行する部分と、 $n$  回の LSRDP で実行される部分に分割されているとする。LSRDP は、FPU アレイ 1 行ごとのパイプライン処理を行う。1 クロックサイクルごとに 1 つのデータ集合を入力し、パイプライン段数分前の入力に対する演算結果を出力する。したがって、演算時間  $T_{cal}$  は、LSRDP での実行ごとに連続して入力するデータ集合数  $C_i$  と LSRDP の行数  $A$  の和から 1 を引いた値に比例し、LSRDP の動作周波数  $f_{LSRDP}$  に反比例する。

$$T_{cal} = \sum_i^n \frac{C_i + A - 1}{f_{LSRDP}} \quad (3)$$

LSRDP は連続する入出力の最初と最後のデータ転送のために、それぞれ LSRDP 間のレイテンシ  $Lat_{mem\_LSRDP}$  分ストールする必要がある。さらに、LSRDP が要求するメモリバンド幅  $BW_{req\_i}$  が主記憶のメモリバンド幅  $BW_{mem}$  より大きいとき、1 つの入力データ集合ごとにそれぞれのメモリバンド幅の比に比例した分ストールする。また、 $BW_{req\_i}$  が  $BW_{mem}$  より小さい場合は、入力データ集合ごとのストールは発生しない。

$$T_{st} = \sum_i^n \frac{2 \times Lat_{mem\_LSRDP}}{f_{LSRDP}} + \begin{cases} \left( \frac{BW_{req\_i}}{BW_{mem}} - 1 \right) \times \frac{C_i}{f_{LSRDP}} & : (BW_{req\_i} > BW_{mem}) \\ 0 & : (BW_{req\_i} \leq BW_{mem}) \end{cases} \quad (4)$$

LSRDP が要求するメモリバンド幅  $BW_{req\_i}$  を、1 クロックサイクルごとに入出力するデータサイズと LSRDP の動作周波数との積で定義する。

$$BW_{req\_i} = (input_i + output_i) \times f_{LSRDP} \quad (5)$$

$ET_{oh}$  は、LSRDP で実行する各部分ごとの再構成時間  $T_{rec\_i}$ 、GPP・LSRDP 間の通信時間  $T_{tra\_i}$ 、LSRDP に入出力するデータを整列する時間  $T_{sort\_i}$  の和とする。

$$ET_{oh} = \sum_{i=1}^n \{T_{rec\_i} + T_{tra\_i} + T_{sort\_i}\} \quad (6)$$

### 4. ベンチマーク

LSRDP の性能評価を行うベンチマークとして、本稿では 2 階の定数係数偏微分方程式のうち 1 次元の熱伝導方程式ならびに 2 次元の Poisson 方程式を、さらに量子化学分野の 2 電子積分計算を選択し、3 種類のアプリケーションに対し次章以降の性能評価実験を行った。

#### 4.1 2 階の定数係数偏微分方程式

自然科学の問題で座標や時間など 2 個以上の独立変数に関する変化を数式で表現すると偏微分方程式になることが多く、その多くが 2 階偏微分方程式である。一般に、 $x, y$  の関数  $u(x, y)$  の 2 次元 2 階の偏微分方程式は

$$A \frac{\partial^2 u}{\partial^2 x} + B \frac{\partial^2 u}{\partial x \partial y} + C \frac{\partial^2 u}{\partial^2 y} + a \frac{\partial u}{\partial x} + b \frac{\partial u}{\partial y} + cu = f(x, y) \quad (7)$$

と書き表される。ここで  $A \sim c$  は定数または独立変数  $x, y$  や従属変数  $u$  の関数である。この偏微分方程式は判別式  $B^2 - 4AC$  の値により、正值では双曲型、ゼロ値では放物型、負値では橢円型に分類され、それぞれ物理的には振動方程式、熱伝導や拡散方程式、Poisson 方程式に対応する [3], [4]。

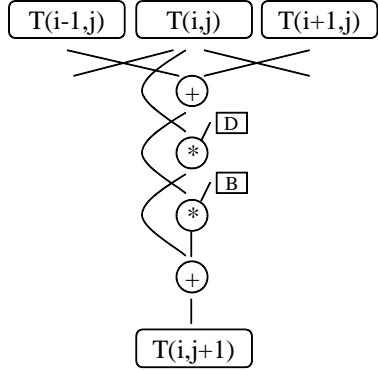

図 3 热差分方程式の最小単位のデーターフローグラフ

#### 4.2 热伝導方程式プログラム

式(7)より, 方程式の中に時間  $t$  を含む拡散方程式や热伝導方程式は標準化の座標変換の後に以下の放物型方程式として得られる.

$$\frac{\partial T(x, t)}{\partial t} = A \frac{\partial^2 T(x, t)}{\partial x^2} \quad (8)$$

更にこの方程式に対し陽解法を適用することで以下の差分方程式が得られる.

$$\begin{aligned} T(x_i, t_{j+1}) \\ = T(x_i, t_j) + A[T(x_{i-1}, t_j) + T(x_{i+1}, t_j) - 2T(x_i, t_j)]/h^2 \\ = D \times T(x_i, t_j) + B \times [T(x_{i-1}, t_j) + T(x_{i+1}, t_j)] \end{aligned} \quad (9)$$

ここで  $h$  は差分方程式を解く際のメッシュ間隔,  $D, B$  については計算の定数である. 対応する DFG は図 3 となっており, 入力 3, 出力 1, 演算数 4 の構成を持つ. この DFG は熱差分方程式の最小単位である.

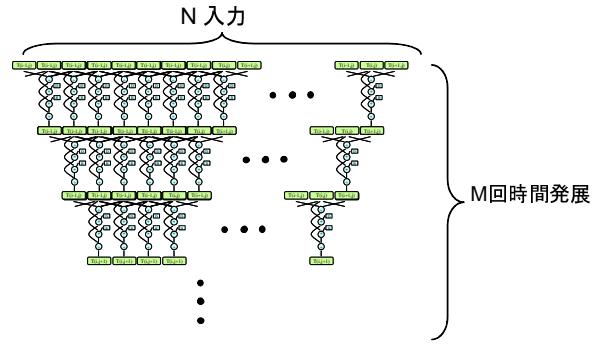

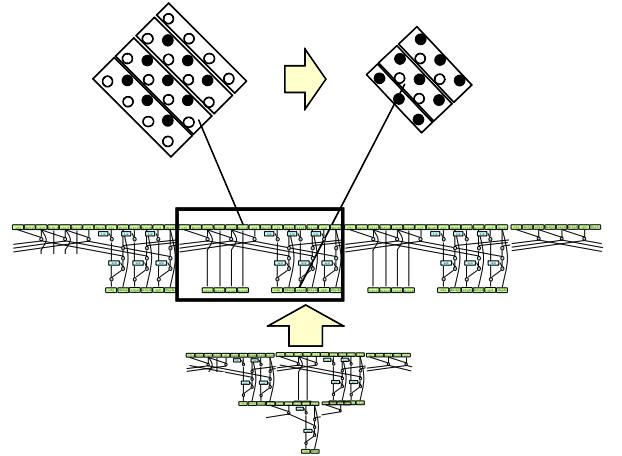

上記の差分方程式は, 時間発展した 1 点  $(x_i, t_{j+1})$  の求値に際し現在の 3 点  $(x_{i-1}, t_j), (x_i, t_j), (x_{i+1}, t_j)$  をもとに計算している. 対象となる計算がメッシュ点にして長さ  $x_{i-N/2} \sim x_{i+N/2}$ , の一次元の領域に対し,  $t_j \sim t_{j+M}$  の時間発展には, 式(9)を  $N \times M$  回繰り返し適用する必要がある. ここで, 式(9)の差分式を空間方向と時間方向に接続する事を考えてみる. これは図 4 の様に DFG を接続することに対応しており, 横方向に  $N$  個, 縦方向に  $M$  個接続することで, 入力が  $N$  個, 出力が  $N/2^M$  個, 演算数  $4 * (N + N/2^M) * M/2$  個の巨大な DFG を作成することが可能である. その結果, この DFG を LSRDP に実装することにより, LSRDP ローカルクロック毎に大量の演算についてパイプライン実行が可能となる.

#### 4.3 Poisson 方程式プログラム

式(7)より, 座標変換後の 2 次元の標準型の Poisson 方程式は以下となる.

$$\frac{\partial u(x, y)}{\partial x} + \frac{\partial u(x, y)}{\partial y} = f(x, y) \quad (10)$$

この方程式に対し逐次緩和法を適用することで以下の繰返し型差分方程式が得られる.

$$u^{(n+1)}(x_i, y_j)$$

図 4 データフローグラフの接続

図 5 Red/Black Gauss-Seidel 法を利用した Poisson 方程式のデータフローグラフ作成

$$\begin{aligned} &= (1 - \omega)u^{(n)}(x_i, y_j) \\ &+ \frac{\omega}{4}[u^{(n)}(x_{i-1}, y_j) + u^{(n)}(x_{i+1}, y_j) \\ &+ u^{(n)}(x_i, y_{j-1}) + u^{(n)}(x_i, y_{j+1}) - h^2 f(x_i, y_j)] \end{aligned} \quad (11)$$

ここで  $h$  は差分方程式を解く際の  $x, y$  方向のメッシュ間隔であり今回は等間隔としている.  $\omega$  は繰り返し計算のための収束用パラメータである.

この差分方程式の求値には, Red/Black Gauss-Seidel 法アルゴリズムを用いる(図 5). これは式(11)の  $n+1$  回目の繰り返しにおけるメッシュ点  $(i, j)$  の値  $u^{(n+1)}$  が, 繰り返し  $n$  回目の自身を含めた周囲のメッシュ点  $(i, j), (i+1, j), (i-1, j), (i, j+1), (i, j-1)$  を基に計算される事を利用している. 図の左側の  $4 \times 4$  の白丸の内側のメッシュ点から  $3 \times 3 + 2 \times 2 + 1$  個ある右側の  $3 \times 3$  の黒丸の内側のメッシュ点の値を求める際は, 式(11)接続することにより, 図の様に入力 7 点, 出力 5 点の DFG を生成し, この DFG を 4 つ束ねることで目的となる DFG を求める. 更にこの DFG は中心の 1 点が求まるまで多段に接続する事が可能である.

#### 4.4 2 電子積分計算プログラム

本実験の 3 つ目のアプリケーションとして, 2 電子積分計算を用いる. 2 電子積分計算は分子軌道法計算における 1 处理であり, 巨大な分子を対象とする際には分子軌道法の全実行時間の 95%を占めている重要な部分である. 2 電子積分計算のアル

```

for (I=0; I<Nshell; I++)

for (J=0; J<I; J++)

for (K=0; K<J; K++) 1個の2電子積分の計算

for (L=0; L<K; L++) (縮約ループに対応)

for (line=0; line<NlineSB; line++)

初期積分計算

漸化計算

end

部分Fock 行列の計算

end

end

end

```

図 6 2 電子積分計算プログラムの構成

```

for (I=0; I<Nshell; I++)

for (J=0; J<I; J++)

for (K=0; K<J; K++)

for (L=0; L<K; L++)

LSRDP の再構成(I,J,K,L の組に依存)

for (line=0; line<NlineSB; line++)

初期積分計算

主記憶上で入力データの準備・整列

end

GPPからLSRDPに動作の開始を指示

NlineSB の数だけLSRDPを動作させる

・1クロック毎に主記憶からデータを

読みだしつつ計算(漸化計算+部分Fock 行列の計算)

LSRDP がGPPに動作の終了を報告

for (line=0; line<NlineSB; line++)

主記憶上で出力データの取り扱い

end

end

end

end

end

```

図 7 LSRDP を利用して 2 電子積分計算を実装する場合の疑似コード

ゴリズムはいくつか知られているが、本稿は、その中でも高精度かつ高速な小原のアルゴリズム [5] を採用する。その疑似コードを図 6 に示す。全体は、外側 4 重ループ  $I, J, K, L$  の中にあって 1 つの 2 電子積分計算と部分フォック行列の計算を行う構造となっている。1 つの 2 電子積分計算では更に縮約ループと言われるループ構造が存在しており、ループボディとして初期積分計算と漸化計算の計算が実行される。初期積分計算には浮動小数点除算や開平逆数、指数関数演算、誤差関数演算等の複雑な演算が存在しており、漸化計算や部分フォック行列計算では多数の積と和の演算のみから構成される。次章での説明の通り、LSRDP での演算を加減算と乗算に限定した今回の性能評価では、2 電子積分計算のうち、漸化計算ならびに部分フォック計算を LSRDP 上に実装し、複雑な演算を内包する初期積分計算ならびにループの制御部分は GPP 側での処理とする。

LSRDP を使用するシステムに実装する擬似コードを示したのが図 7 である。初期積分計算は GPP にて行うが、その出力は縮約ループの繰り返し分 ( $NlineSB$ ) だけ主記憶上にて整列し保存される。その後 GPP より LSRDP へと計算開始信号が送られることで初期積分計算の際に保存された  $NlineSB$  分のデータを主記憶から LSRDP へとバースト転送を行いながら、漸化計算+部分フォック行列計算を LSRDP 上にて実行する。出力は入力と同様に主記憶上に整理された形で保存する。この整理されたデータを再び主記憶上の適切な変数へと書き戻すのが最後のループ計算である。

表 1 シミュレータのパラメータ

|           |                                     |                             |

|-----------|-------------------------------------|-----------------------------|

| 命令発行方式    | アウトオブオーダ方式                          |                             |

| 動作周波数     | 3.2GHz                              |                             |

| 命令発行幅     | 4 命令/cc                             |                             |

| 命令デコード幅   | 4 命令/cc                             |                             |

| キャッシュ構成   | L1 データキャッシュ                         | 16KB(64B/エントリ, 2ウェイ, 2cc)   |

|           | L1 命令キャッシュ                          | 16KB(64B/エントリ, 1ウェイ, 1cc)   |

|           | L2 キャッシュ                            | 512KB(64B/エントリ, 4ウェイ, 16cc) |

| 主記憶レイテンシ  | First chunk 300cc : inter chunk 4cc |                             |

| L2-主記憶間バス | バス幅                                 | 8, 16, 32, 64               |

| FPU       | FPALU 4                             | : FP Multiplier/dividers 1  |

表 2 システムのパラメータ

|                 |                       |

|-----------------|-----------------------|

| 動作周波数           | 200MHz                |

| 主記憶・LSRDP間レイテンシ | 19cc                  |

| GPP・LSRDP間レイテンシ | 19cc                  |

| メモリバンド幅         | 12.8 ~ 102.4GByte/sec |

| 再構成時間           | 1cc                   |

## 5. 性能評価

### 5.1 実験方法

LSRDP の性能を示すために、ベンチマークを用いた定量的評価を行う。ベンチマークとして、熱伝導方程式ならびに Poisson 方程式、2 電子積分計算を選択した。4 節で述べたが、偏微分方程式の 2 つのアプリケーションでは DFG のサイズを自由に選択可能である。そこで、S, M, L と 3 種類の LSRDP サイズを規定し、その中でマッピング可能な DFG を取り扱うこととした。サイズは S, M, L それぞれについて  $26 \times 11$ ,  $26 \times 20$ ,  $70 \times 32$  である。この分類によると、2 電子積分計算の DFG は L に属する。熱伝導方程式については、M と L に対応する DFG を、Poisson 方程式については、S, M, L に対応する DFG について性能評価を行った。

本稿において、実行時間をシステムの性能指標とする。GPP の実行時間はクロックサイクルレベルのシミュレータである SimpleScalar によって計測し、LSRDP の実行時間を 3 節で示したモデル式より算出する。その環境下において、GPP 単体によって実行されるプログラムと、GPP+LSRDP によって実行されるプログラムの全実行時間をそれぞれ評価する。

実験における GPP のパラメータを表 1 に、LSRDP を含むシステム全体のパラメータを表 2 に示す。熱伝導方程式と Poisson 方程式では 1 種の DFG しか用いず、実行中の再構成は行われない。2 電子積分計算については問題を解くために 6 種の DFG が必要であり、適宜再構成を行いつつプログラムを実行する。

### 5.2 結果

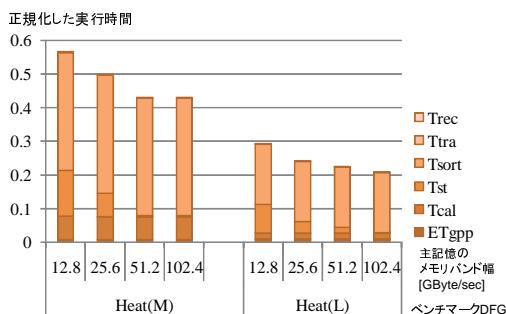

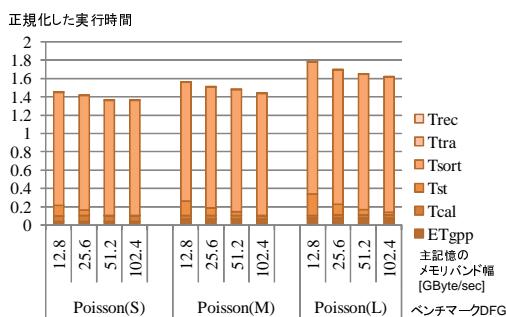

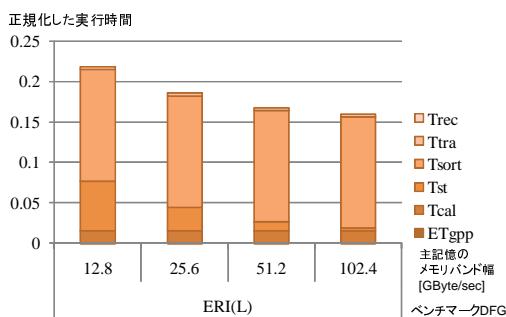

実行結果を図 8 ~ 10 に示す。それぞれのグラフは、プログラムを GPP 単体で実行した場合の実行時間を 1 として正規化されている。

熱伝導方程式と 2 電子積分計算について実行時間が最大 ~ 22%, ~ 16% と大きく減少し、性能向上を果たしているが、Poisson 方程式についてはいずれも GPP での計算より実行時間が増加しており、LSRDP の使用により性能が低下している。この原因として、図 5 から、2 次元メッシュのすべての点につ

図 8 热伝導方程式計算の結果

図 9 Poisson 方程式の計算の結果

図 10 2 電子積分計算の結果

いて S, M, L それぞれに対し, 入力を 18, 38, 66 点分準備する必要があり, そのため, 重なりのある大量のデータの並び替えを行っているためである. グラフから, 並び替えを除いた部分はおよそ 20% 以下である. そのため, もしもデータの並べ替え時間について実行時間の削減が可能であれば, 大幅な性能改善が見込まれる.

また, 全ての結果において, 12.8 ~ 51.2GB/sec. の間ではメモリバンド幅を増加させるに従って性能が向上している. 一方, 51.2 から 102.4 GB/sec. に変化させる際には, Heat (M) と Poisson (S) ではほとんど変化していない. 内訳からストール時間の割合がゼロとなっており, 両計算にて 51.2GB/sec. にてバンド幅が足りている事を示している. 実行時間の大部分が主記憶上でのデータの並び替え時間に費やされており, メモリバンド幅を増加させるに従い, 割合が増加する. これはメモリバンド幅のストール時間に与える影響の相対比が小さくなっているためである.

Poisson 方程式の計算については, 使用している LSRDP の

サイズが S から L へと大きくなるに従い, 性能が低下している. LSRDP のサイズが大きくなるに従い演算性能自身は増加しているが, 入力数との関係: 入力数 / 演算量を求める 3 通りのサイズの DFG について, それぞれ, 0.35, 0.42, 0.55 となり, S, M, L の順番で 1 演算あたりの入力数が増加している. そのため, 並び替えに要する時間の増加が原因と考えられる.

## 6. おわりに

本稿では大規模再構成可能データパス (LSRDP) について, 種々のメモリバンド幅のもとで, 1 次元の熱伝導方程式, 2 次元の Poisson 方程式, 2 電子積分計算のアプリケーションについての性能評価を行った. その結果, 热伝導方程式, 2 電子積分計算については, 実行時間について GPP のみでの計算と比較して, 最大 ~ 22%, ~ 16% と大きく減少した. 一方で Poisson 方程式については逆に実行時間が増加した. これは, 主記憶から LSRDP へのバースト転送利用のために LSRDP 計算にて行っている主記憶上の入出力データの並び替えステップが, 実行時間の大半を占めてしまうからである. 今後は 2 階の定数係数偏微分方程式のうち, 振動方程式についても性能評価を行い, Poisson 方程式のデータ並び替えに要する時間がなるべく少ないアルゴリズムを考案する必要がある.

## 謝 詞

下記 CREST プロジェクトにおいてご討論頂いております, 名古屋大学大学院情報科学研究科, 高木直史教授, 高木一義准教授, 同じく工学研究科, 藤巻朗教授, 赤池宏之助教, 横浜国立大学工学部, 吉川信行教授に感謝いたします. また日頃からご討論頂いております九州大学安浦・村上・松永・井上研究室ならびにシステム LSI 研究センターの諸氏に感謝します. 本研究の一部は, 科学技術振興事業団 (JST) の戦略的創造研究推進事業 (CREST) 「単一磁束量子回路による再構成可能な低電力高性能プロセッサ」の支援によります. 本研究は主に, 九州大学情報基盤研究開発センターの研究用計算機システムを利用しました.

## 文 献

- [1] 島崎慶太, 長野孝昭, 本田宏明, ファルハド メディマー, 井上弘士, 村上和彰, “大規模再構成可能データパスにおけるオンチップ・ネットワーク・アーキテクチャの検討”, 情報処理学会研究報告, 2007-ARC-173, pp.115-120, 2007年6月.

- [2] N.Takagi, K.Murakami, A.Fujimaki, N.Yoshikawa, K.Inoue, and H.Honda: “Proposal of a Desk-Side Supercomputer with Reconfigurable Data-Paths Using Rapid Single-Flux-Quantum Circuits”, IEICE Trans. Electron., E91-C, pp.350-355 (2008).

- [3] 杉江日出澄, 岡崎明彦, 足達義則, 尾崎正弘, “FORTRAN77 による数値計算法”, 培風館, 1986.

- [4] R.H. Landau, and M.J.P. Mejia: “計算物理学 応用編”, 朝倉書店, 2001.

- [5] S. Obara, and A. Saika: “Efficient recursive computation of molecular integrals over Cartesian Gaussian Functions”, J. Chem. Phys., Vol.84, pp.3963, (1986).