# FeliCa IC チップ開発への実行可能な形式仕様記述の実践に基づく設計・構成法の提案

中津川, 泰正 Graduate School of Information Science and Electrical Engineering, Kyushu University

https://doi.org/10.15017/21763

出版情報:九州大学, 2011, 博士(工学), 課程博士

バージョン: 権利関係:

## FeliCa IC チップ開発への 実行可能な形式仕様記述の 実践に基づく設計・構成法の提案

中津川 泰正

平成 24 年 2 月

九州大学大学院システム情報科学府 情報工学専攻

## 論文梗概

組織的に開発を進める必要があるソフトウェア開発現場において、上流工程の文書を中心に多くの問題を抱えており、品質の高いシステムを組織的に効率よく開発することができる手法として、フォーマルメソッドが注目されている。フォーマルメソッドの利用に関して、3 段階の適用レベルが示されることがあるが、そのうち、本論文では、形式仕様記述を行うレベル 0 の段階を扱う. レベル 0 の段階とは、証明までは行わないが、数学的な記法を用いて厳密な仕様を記述する段階である. 筆者らは FeliCa IC チップ開発を通してレベル 0 における形式仕様記述手法の適用の効果を得ることができた. しかしながら、Parnas は 2010年に発表した論文の中で、フォーマルメソッドが実践的手法として広く利用されるような「当然の技術」として、開発現場に浸透していない点を指摘した. 本論文では、「当然の技術」として産業界に浸透するための課題を分析し、形式仕様記述手法を適用する際に必要不可欠となる形式仕様記述手法の設計・構成法を提案する.

形式仕様記述手法が広く利用されるためには、形式仕様記述手法の専門家ではない人が、形式仕様記述を読み、理解し、活用していく必要がある。つまり、そのような形式仕様記述を書くための技術と、活用するための技術が必要である。本論文では、以下の3つの提案を行う。1つ目は、理解容易性に優れた形式仕様を記述するための、形式仕様記述の設計・構成法の提案である。2つ目は、従来からある既に開発現場に浸透しているレビューやテスト手法といった検証技術を主体として、その中で形式仕様記述手法を活用していく方法の提案である。3つ目は、筆者らが使用してきた形式仕様記述手法では取扱いが難しかった、動的な振る舞いに関する検証方法の提案である。

1つ目の、理解容易性に優れた仕様を記述するためには、Hayes と Jones が指 摘した「実行可能性の影響」と Jackson が指摘した「実装の影響」を考慮する 必要がある. まず, 「実行可能性の影響」とは, 仕様アニメーションとして知ら れている方法により記述した仕様を動作させる場合、この「動かすこと」を仕様 記述の目的に含めてしまうことにより、仕様の理解容易性に影響を与えるとい 「実装の影響」とは次のような課題である.一般に、 うものである. 次に、 決すべき問題」を定義した仕様と、「問題の解決方法」を定義した設計を分ける ことで、仕様策定者と設計者が分業して組織的に開発を行うことができると言 われている. しかし, 実際には, この 2 つを分けることは容易ではないため, 仕 様書に「問題の解決方法」を含めてしまうことで、設計者を過剰に制約してしま うという課題である. 「実行可能性の影響」も「実装の影響」も、仕様の記述が 複雑になり、過剰に設計を制約してしまうことが課題である。これらの課題を解 決するために、「実行可能性の影響」に対しては、仕様伝達部と非伝達部からな る仕様記述スタイルを提案する. 「実装の影響」に対しては、仕様と設計におい て定義するデータ構造に着目した形式仕様記述の設計・構成法を提案する.

2つ目の提案として、形式仕様記述手法の専門家ではない、様々なレビューの目的を持った読者にとって、読みやすい仕様について分析を行い、レビューの目的とテストの目的を考慮した仕様記述フレームワークを提案する。構造が簡潔な点とテストとの親和性の点で、ディシジョンテーブルの構造を用いる方法と、仕様の概要と詳細を区別して記述する方法を提案する。また、実際に、形式仕様記述から体系的にテスト項目を作成し、テスト項目とテストスクリプトの網羅性を機械的に検証する方法を提案する。

3つ目は、形式仕様記述手法では取扱いが容易でない動的な振る舞いに関する 課題に対して、同時並行に動作する動的な振る舞いをモデル検査を用いて検証 する方法を提案する.

本論文では、これらの形式仕様を記述するための方法と活用するための方法 を提案することによって、形式仕様記述手法が、産業界において適用可能で有効 な手法であることを開発実践を通して示した.

## 目 次

| 第1章 | 序論    |                      | 1  |

|-----|-------|----------------------|----|

| 1.1 | ソフト   | ウェア開発の現状             | 1  |

|     | 1.1.1 | 本研究が想定する開発プロセス       | 2  |

|     | 1.1.2 | ソフトウェア開発の現状          | 3  |

| 1.2 | フォー   | -マルメソッドの適用における課題     | 4  |

|     | 1.2.1 | フォーマルメソッドの概要         | 4  |

|     | 1.2.2 | フォーマルメソッドの現状         | 6  |

|     | 1.2.3 | フォーマルメソッドの設計・構成法の課題  | 7  |

| 1.3 | 形式仕   | C樣記述手法 VDM           | 9  |

|     | 1.3.1 | 形式仕様記述手法 VDM の概要     | 10 |

|     | 1.3.2 | 統合開発環境 VDMTools      | 10 |

|     | 1.3.3 | VDM++ による実行可能仕様      | 11 |

| 1.4 | モデル   | /検査                  | 13 |

| 1.5 | 本研究   | 台の基となるフォーマルメソッドの適用事例 | 14 |

|     | 1.5.1 | FeliCa IC チップの特徴     | 15 |

|     | 1.5.2 | 開発プロジェクトの概要          | 16 |

|     | 1.5.3 | 形式仕様記述手法の適用対象と規模     | 17 |

|     | 1.5.4 | 適用における効果             | 18 |

|     | 1.5.5 | 適用における課題             | 20 |

| 1.6 | 本論文の構成                               | 22 |

|-----|--------------------------------------|----|

| 第2章 | 本研究において扱うフォーマルメソッドの適用における課題          | 25 |

| 2.1 | 実行可能仕様における仕様と設計の分離に関する課題             | 27 |

|     | 2.1.1 「伝えること」と「動かすこと」を目的とした実行可能仕様の課題 | 27 |

|     | 2.1.2 仕様と設計の分離に関する課題                 | 28 |

| 2.2 | レビューとテストの用途として形式仕様記述を利用する場合の課題       | 29 |

|     | 2.2.1 レビューとテストにおける一般的な課題             | 29 |

|     | 2.2.2 レビューの用途から見た仕様記述の理解容易性に関する課題    | 30 |

|     | 2.2.3 仕様に基づくテストの用途から見た課題             | 3  |

| 2.3 | 形式仕様記述手法では取扱いが容易でない動的な振る舞いに関する課題.    | 33 |

| 第3章 | 関連研究                                 | 35 |

| 3.1 | フォーマルメソッドの産業界への適用事例                  | 35 |

|     | 3.1.1 CICS                           | 36 |

|     | 3.1.2 CDIS                           | 36 |

|     | 3.1.3 パリの地下鉄とシャルル・ド・ゴール国際空港のシャトル     | 3  |

|     | 3.1.4 本適用事例との比較                      | 3  |

| 3.2 | 実行可能仕様における「実行可能性の影響」                 | 38 |

| 3.3 | 仕様と設計の分離に関する「実装の影響」の研究               | 40 |

|     | 3.3.1 「要求と仕様とプログラム」と「適用領域」           | 41 |

|     | 3.3.2 「実装の影響」                        | 42 |

|     | 3.3.3 本提案手法との比較                      | 43 |

| 第4章 | 仕様と設計を分離する実行可能仕様の設計・構成法の提案           | 45 |

| 4.1 | 「実行可能性の影響」を解決する仕様記述スタイルの提案と考察        | 47 |

|     | 4.1.1 操作的な記述と宣言的な記述から見た実行可能仕様の課題     | 48 |

|     | 4.1.2 「実行可能性の影響」を解決する仕様記述スタイルの提案     | 50 |

|     | 4.1.3 陰関数定義に関する考察                       |

|-----|-----------------------------------------|

|     | 4.1.4 陽関数定義に関する考察                       |

|     | 4.1.5 拡張陽関数定義に関する考察 5                   |

| 4.2 | データ構造の隠蔽による仕様と設計の分離方法の提案 5              |

| 4.3 | 本提案手法を用いた具体的な記述例による評価6                  |

|     | 4.3.1 「実行可能性の影響」を解決する仕様記述スタイルの評価 6.     |

|     | 4.3.2 仕様と設計の分離に関する課題を解決する形式仕様記述の評価 7    |

| 4.4 | 本提案手法の FeliCa IC チップ開発への適用の結果と考察 7      |

| 4.5 | 仕様と設計を分離する実行可能仕様のまとめ                    |

| 第5章 | レビューとテストの用途を考慮した仕様記述フレームワークの提案 79       |

| 5.1 | ラベル付き条件による仕様記述フレームワークの提案                |

|     | 5.1.1 ディシジョンテーブルの構成を用いた仕様記述フレームワーク 8    |

|     | 5.1.2 仕様記述フレームワークの基本型                   |

|     | 5.1.3 仕様記述フレームワークの拡張型 9                 |

|     | 5.1.4 レビューの用途から見た仕様の理解容易性の評価と考察 9       |

| 5.2 | 仕様に基づくテストへの形式仕様記述の活用方法の提案10             |

|     | 5.2.1 本研究において定めた品質目標                    |

|     | 5.2.2 ディシジョンテーブルを用いたテスト設計手順 10.         |

|     | 5.2.3 ログ出力によるテスト項目とテストスクリプトの網羅性の検証方法 10 |

| 5.3 | レビューとテストの用途を考慮した仕様記述フレームワークのまとめ 10      |

| 第6章 | 動的な振る舞いに関するモデル検査の適用 111                 |

| 6.1 | 導入目的と段階的導入 11                           |

|     | 6.1.1 導入目的                              |

|     | 6.1.2 段階的導入 11                          |

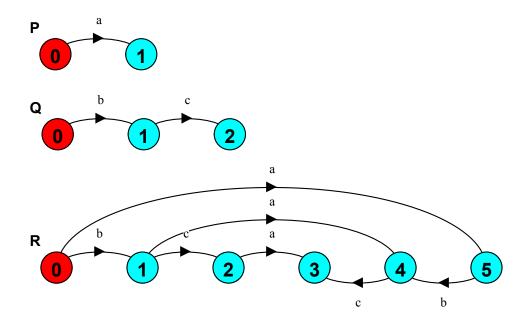

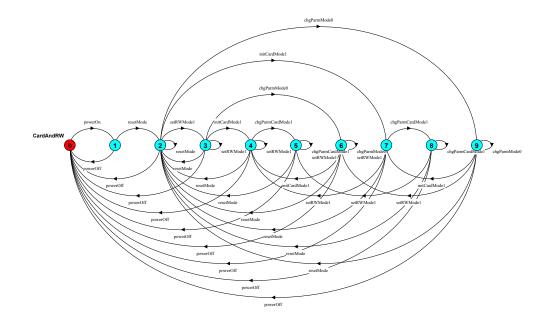

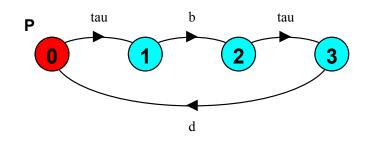

| 6.2 | モデル検査ツール LTSA の概要                       |

| 6.3 | ステップ 1 とステップ 2 の検証範囲11                  |

| 6.4  | ステッ   | プ 1 の実施内容と結果・考察                  | 119 |

|------|-------|----------------------------------|-----|

|      | 6.4.1 | 仕様モデルの作成                         | 119 |

|      | 6.4.2 | 仕様モデルの検査                         | 120 |

|      | 6.4.3 | プロパティの作成と検査                      | 121 |

|      | 6.4.4 | シナリオの検査                          | 122 |

|      | 6.4.5 | ステップ1の結果・考察..................... | 123 |

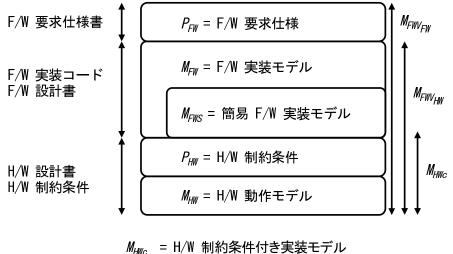

| 6.5  | ステッ   | プ 2 の実施内容と結果・考察                  | 124 |

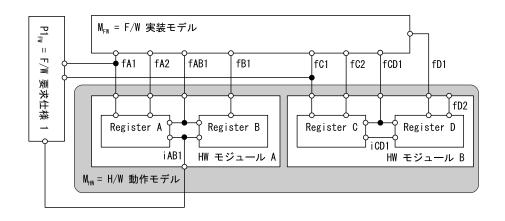

|      | 6.5.1 | H/W 実装モデルの作成と検査                  | 126 |

|      | 6.5.2 | H/W 制約条件のプロパティの作成と検査             | 126 |

|      | 6.5.3 | F/W 実装モデルの作成と検査                  | 127 |

|      | 6.5.4 | F/W 要求仕様のプロパティ作成と検査              | 130 |

|      | 6.5.5 | ステップ 2 の結果・考察                    | 131 |

| 6.6  | 動的な   | 振る舞いに関するモデル検査の適用のまとめ             | 132 |

|      | 6.6.1 | ステップ 1                           | 132 |

|      | 6.6.2 | ステップ 2                           | 133 |

|      | 6.6.3 | まとめ                              | 133 |

| 第7章  | 結論    |                                  | 135 |

|      |       |                                  |     |

| 謝辞   |       |                                  | 143 |

| 参考文献 | 武     |                                  | 145 |

| 索引   |       |                                  | 152 |

## 第1章

## 序論

本章では、まずソフトウェア開発の現状を述べ、フォーマルメソッドの適用における課題を考察する. 次に、本研究において扱うフォーマルメソッドとして、形式仕様記述手法 VDM とモデル検査の概要を述べる. 最後に、本研究の基となる筆者らのフォーマルメソッドの適用事例を紹介し、本研究において扱う課題の概要を述べる.

これらの課題を本章に続く2章と3章において詳細に議論する.4章以降では、それぞれの課題に対する解決方法を提案していく.

#### 1.1 ソフトウェア開発の現状

ソフトウェアは, 社会基盤となる情報システムや日常生活に必要不可欠な様々な製品に組み込まれて利用されることが多いため, ソフトウェアの信頼性や安全性をいかに確保するかということが, 社会的に重要な課題となっている. また, 開発対象が大規模, 複雑化していく中で, 品質の高いソフトウェアを効率的に開発するために, 開発現場ではソフトウェア開発工程全体をいくつかの工程に分け, 専門性を持った人たちからなるチームが各工程を担当することで, 分業して組織的に開発を進める必要がある.

工程は、開発現場ごとに様々ではあるが、要求分析、仕様策定、設計検討、実装、テスト、 運用・保守に分かれていることが多い。一般に開発工程全体をソフトウェアライフサイ クルと呼び、開発の進め方を開発プロセスと呼ぶ。本節では、まず本研究において想定す る開発プロセスについて述べた後に、ソフトウェア開発における現状について述べる.

#### 1.1.1 本研究が想定する開発プロセス

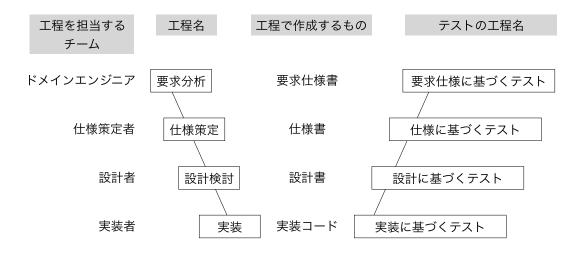

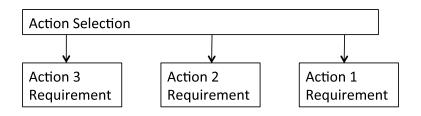

図1.1 に本研究において前提とする開発プロセスを示す. 図は, ソフトウェア開発のライフサイクルを模式的に表す上で一般に用いられている「V字型モデル」に準じたものである. ウォータフォール型のライフサイクルモデル [Roy70] を拡張した「V字型モデル」は, 左側に要求分析と仕様策定と設計検討と実装の流れを示し, 右側にはテストの流れを示している. 左側と右側の高さが同じ箇所は, 開発の詳細さの段階が同じであることを表している. 図1.1 は次のような記載となっている. 左側に, 各工程名と各工程を担当するチームの名称を示し, 中央には, 左側の各工程で作成するものを記載し, 右側に左側に対応するテストの工程名を示した.

以下では、図1.1の各工程ごとに、本論文において用いる用語を定義する。本論文では、要求分析を行うチームをドメインエンジニアと呼び、要求分析で決定する事柄を要求あるいは要求仕様、作成する文書を要求仕様書と呼ぶことにする。仕様策定を行うチームを仕様策定者、仕様策定で決定する内容を仕様、作成する文書を仕様書と呼ぶことにする。設計検討を行うチームを設計者、この工程で決定する事柄を設計、作成する文書を設計書と呼び、実装を行うチームを実装者、この工程で作成するソースコードを実装コードと呼ぶことにする。テストを行うチームを評価者またはテスト実施者と呼ぶこととする。テストの工程では、図1.1に示すように、対応する工程に基づくテストを実施する。図1.1の右側の上から、要求仕様書を基に実装コードが要求仕様を満たしていることを確認するテストを、要求仕様に基づくテストと呼び、仕様書を基に実装コードが仕様を満たしていることを確認するテストを、設計に基づくテスト、設計書を基に実装コードが設計を満たしていることを確認するテストを、設計に基づくテスト、実装者が行うテストを実装に基づくテストと呼ぶこととする。要求仕様と仕様と設計に基づくテストは、テストの基になる文書が存在するが、実装に基づくテストは、実装者の意図を基準として実装コードのテストを行う。図1.1には示していないが、運用・保守を行うチームを運用者あるいは運

図1.1 本論文において前提とする「V字型モデル」に準じた開発プロセス

用・保守者と呼ぶことにする.

#### 1.1.2 ソフトウェア開発の現状

多くの開発現場では、工程間で文書を受け渡すことで開発を進めている。文書の厳密性や一貫性、簡潔性、理解容易性などの品質が、開発効率および最終製品の品質に大きく影響を与えることが知られている。特に、開発工程の前段階である要求分析および仕様策定工程において品質の高い仕様書を作成することで、その後の設計や実装、テスト、運用・保守を正確かつ組織的に行うことができるため、開発効率を高めることができる。

しかし、開発現場では上流工程の文書の品質を中心に多くの問題を抱えている. 以下に、上流工程の文書の品質に起因する、起こりうる具体的な問題について述べる.

テストの工程においては、次のような問題が考えられる. 曖昧な仕様に起因する手戻りが発生した場合、信頼性を高めるためのテスト工数およびテスト期間が見積もりを大幅に超える. そのため、スケジュールが遅延する. また、テストの入力となる仕様が曖昧である場合、テストの観点がもれてしまうので、十分なテストが行えない. そのため、市場において品質の問題を起こすことが考えられる.

設計と実装の工程においては、次のような問題が考えられる。本来は、仕様策定工程で 決めるべきことが決定されておらず、また、仕様書における記述が曖昧であるために、仕 様策定工程から設計工程に移っているにもかかわらず、仕様を決定するための議論が多くなって開発効率が悪い.また、明確に定義した仕様がないので、詳細な仕様について仕様策定者と設計者が口頭で話し合った結果、十分な意思疎通が行えないまま、仕様とは異なる振る舞いをする製品が出荷されてしまう.そのため、市場において品質の問題を起こすことが考えられる.

運用・保守の工程においては、次のような問題が考えられる。曖昧な仕様を基に実装を行い、実装中に明らかになった仕様を仕様書に反映していないため、正確な仕様書がない。そのため、運用・保守工程において、顧客からの質問に対して実装者しか回答を行えない状況となってしまう。この実装者が異動した場合、ソースコードの保守および顧客のサポートが難しくなることが考えられる。

これらの問題を解決するために、上流工程において、仕様を厳密に記述し検証するための数多くの開発手法が提案されている。フォーマルメソッド (formal methods) は、計算機科学における数学を基盤としたソフトウェアおよびハードウェアシステムの仕様記述、開発、検証を行う技術の総称である。早期に仕様の検証を行うことで後工程における手戻りを減らし、厳密な仕様を基に設計およびテスト、運用・保守を行うことで、上流工程から下流工程において体系的な品質確保の枠組みを構築し、品質の高いシステムを組織的に効率よく開発することができる。

#### 1.2 フォーマルメソッドの適用における課題

本節では、フォーマルメソッドの概要について述べ、産業界への適用における課題を分析する.

#### 1.2.1 フォーマルメソッドの概要

近年、 品質の高いシステムを効率よく開発する手法として、 フォーマルメソッドに対する関心が高まっている  $[CWA^{+}96, BH06, + 6]$ .

例えば、情報システムや製品のセキュリティ機能について第三者が評価・認証を行う

| _       |                      |

|---------|----------------------|

| 評価保証レベル | 説明                   |

| EAL1    | 機能的なテストの保証           |

| EAL2    | 構造的なテストの保証           |

| EAL3    | 系統的なテストおよび確認の保証      |

| EAL4    | 系統的な設計, テスト, レビューの保証 |

| EAL5    | 準形式的な設計およびテストの保証     |

| EAL6    | 準形式的な設計の検証およびテストの保証  |

| EAL7    | 形式的な設計の検証およびテストの保証   |

表 1.1 ISO/IEC 15408 [ISO09c] において定められた評価保証レベル

ために国際的な評価基準を定めた ISO/IEC 15408<sup>[ISO09a, ISO09b, ISO09c]</sup> において, 7 段階の評価保証レベル EAL (Evaluation Assurance Level) が定められており, 最高レベルであるレベル 7 を取得するためには設計が形式的に検証されていなければならない. **表 1.1** にそれぞれの評価保証レベルを示す. レベル 1 からレベル 4 では, 形式的な設計は求められていない. レベル 5 においては準形式的な設計, レベル 6 においては準形式的な設計の検証が求められる. ISO/IEC 15408 は情報システムやセキュリティ製品の政府調達基準として利用されている. また, 電気・電子関連の国際安全規格として 2000 年に制定された IEC 61508<sup>[IEC10]</sup> においてもフォーマルメソッドの適用を推奨している.

フォーマルメソッドという用語は技術の総称として用いられ指し示す技術領域は広い. 一般的にフォーマルメソッドは、計算機科学における数学を基盤としたソフトウェアおよびハードウェアシステムの仕様記述、開発、検証を行う技術の総称として用いられている. つまり、数学を基盤とした記述言語により開発対象の特性を仕様として記述し、定理証明や機械的な検査により記述の正しさを検証する手法である. あるいは、開発対象の特性である仕様の記述から段階的に証明を行いながら詳細化を行いプログラムを導出する手法である.

フォーマルメソッドには多種多様な理論や手法, ツールが提供されており, その利用に関して近年では以下の3段階の適用レベルが示されている [荒木 08, Wik].

#### レベル 0:形式仕様記述

数学的な記法を用いて厳密な仕様を記述する. この仕様記述を基にしてプログラム

を開発する. 証明や分析までは行わない.

レベル1:形式的開発および検証

プログラムの性質を証明したり、詳細化により仕様からプログラムを作成する.

レベル 2:機械支援による証明

定理証明器や証明支援器を用いてプログラムの性質を証明する.

本研究において述べるフォーマルメソッドの適用レベルは、レベル 0 の形式仕様記述の段階である. レベル 0 の段階であってもフォーマルメソッドの適用による効果を得ることができる. フォーマルメソッドの適用により、完全に正しいシステムを作ることはできないが、フォーマルメソッドを適用しなければ見つけることが難しい矛盾、曖昧さ、不完全さが明らかになり、またシステムに対する理解を深めることができる.

#### 1.2.2 フォーマルメソッドの現状

フォーマルメソッドは 1970 年代後半から 1980 年代にかけて研究が始められ歴史のある技術である. また, 数多くのフォーマルメソッドの有効性を示す適用事例や適用における知見が発表されており [HK91, BH95, CWA+96, Hal96, Abr06, BH06], 産業界において十分に適用可能な技術である. しかしながら, 2010 年に David L. Parnas は, フォーマルメソッドが実践的手法として開発現場において広く利用されるような「当然の技術」として使われていない点を指摘し, フォーマルメソッドの問題点を示した [Par10]. Parnas は広く適用が進んでいない理由を次のように述べている.

産業界への実践的なフォーマルメソッドの適用は、フォーマルメソッドの利用が共通のプラクティスではないことを確認するような例外的な事例のままである. … 逆説的に、フォーマルメソッドの成功事例に関する報告は、標準的な手順として、フォーマルメソッドの産業界への適用に失敗していることを明らかにしている. もし、これらの手法の利用がありふれた手順であれば、手法の利用に関する論文は発表されることはないからである.

つまり、フォーマルメソッドの産業界への適用に関する論文が、現在もなお取り上げられていることが、ありふれた「当然の技術」として、フォーマルメソッドが産業界に浸透していない現状を表していると述べている。Parnas は 研究者の立場から、フォーマルメソッドの現状を指摘し、「当然の技術」としてフォーマルメソッドが用いられるために必要な研究の指針を与えた。

#### 1.2.3 フォーマルメソッドの設計・構成法の課題

前述のとおり、本研究において述べるフォーマルメソッドの適用レベルは、レベル 0 の形式仕様記述の段階である。このレベル 0 の段階においても、産業界ではありふれた「当然の技術」として用いられていない。自然言語を用いた仕様記述には、正確性や簡潔性などの側面において様々な問題があることが 20 年以上前から知られている。Bertrand Meyer は 1985 年に仕様記述に自然言語を用いることによる欠陥と、自然言語の代わりに数学的なフォーマルな表現を用いた場合の利点を明らかにした [Mey85]。開発現場では多くの問題を抱えているにもかかわらず、フォーマルメソッドが産業界に浸透しないのはなぜなのであろう。

以下では、フォーマルメソッドの適用者の立場から、フォーマルメソッドが「当然の技術」として産業界に浸透するための課題を分析する.

課題を分析するために、レベル 0 の適用レベルを レベル 0-a とレベル 0-b の 2 つの 段階に分けて考える. レベル 0-a は、形式仕様の記述者が、厳密に仕様を記述するという 適用のレベルである. これにより、形式仕様の記述者の開発対象に対する理解が深まり、記述の不十分さや、曖昧さに起因する不具合を早期に見つけることができる. レベル 0-b は、形式仕様の記述者以外である、ドメインエンジニアや設計者、実装者、評価者が、形式 仕様記述を参照し、形式仕様記述に基づいて設計と実装とテストを行う適用のレベルである. これにより、それぞれの開発工程において品質を確保し、開発効率を高めることができる.

レベル 0-a からレベル 0-b になることで, 形式仕様記述を活用する工程が, 仕様策定工

程から開発工程全体に広がる. そのため、形式仕様を記述する上で必要な技術も異なると考える. レベル 0-a において、開発プロジェクトの中で形式仕様記述を活用する人は、形式仕様の記述者のみの限られた人である. その人たちが形式仕様記述手法を習得し、その人たちの中で理解される形式仕様記述を作成すればよい. 一方で、レベル 0-b において、形式仕様記述を活用する人は、開発プロジェクトのほぼ全ての工程の人たちとなる. ドメインエンジニア、設計者、実装者、評価者が、形式仕様記述を読み、理解し、活用していく必要がある. これらの人たちが、既に形式仕様記述手法を習得していることは希であり、数日の研修によって形式仕様記述手法を学ぶことになる. 形式仕様記述手法の専門家ではない人に、形式仕様記述をありふれた「当然の技術」として活用してもらう必要がある. そのために、形式仕様記述を読みやすいと感じ、自然言語よりも形式仕様記述言語を用いていることにメリットを感じることが大切である. つまり、レベル 0-b の適用段階において、そのような形式仕様を記述するための技術と、活用するための技術が必要となる. この課題を解決することで、形式仕様記述手法が、ありふれた「当然の技術」として開発プロジェクトにおいて広く活用されるようになり、さらには、産業界においても広く活用されることにつながると考える.

本研究では、前述のレベル 0-b の段階に到達するために必要な、形式仕様を記述するための技術と活用するための技術を研究課題として設定した。記述するための技術として、様々な役割を担った開発者にとって、理解容易性に優れた仕様を記述する技術が必要である。ここでいう様々な役割を担った開発者とは、ドメインエンジニア、設計者、実装者、評価者である。活用するための技術としては、従来からある既に開発現場に浸透しているレビューやテスト手法といった検証技術を主体として、その中で形式仕様記述手法を活用していく技術が必要である。

また、本研究では、前述の形式仕様を記述するための技術として、形式仕様記述の設計・構成法に着目した。ソフトウェア開発において、構成法 (construction) とは設計・実装・デバッグ・開発者テストなどを中心とする活動である。これらの活動を省略してソフトウェアを完成させることは難しい。形式仕様記述手法の適用においても同様に、設計・構成法に関する技術が必要不可欠である。

筆者は、フォーマルメソッドの導入を検討している段階において、フォーマルメソッド が我々の課題を解決できることは分かった.しかし、手法を試みる段階において適用技術 の設計・構成法に関する知識が不足していたため、「何から着手すべきであるか」という ことが分からなかった.そのため、 初めは設計・構成法の技術を身につけるためにフォー マルメソッドの有識者から学びながら「分からなくても、とにかく手を動かしてみる」と いう方法を取った. 有識者から学びながら手法の適用を進めることは. フォーマルメソッ ドに限らず新しい技術の習得において必要なことが多い. 新しい技術の習得・適用には、 良き指導者を見つけるとよい [BH95, HO09]. 良き指導者を見つけることで, 筆者は実際に適 用するときの設計・構成法に関する知識不足の課題を解決した. 設計・構成法は, 具体的 な詳細設計や実装の技術であるため、抽象化および一般化することが難しいものが多い. そのため、新しい技術を適用するために、開発現場ごとに良き指導者を見つけることで、 設計・構成法の課題を解決している.

本論文の目的は, FeliCa IC チップ開発への適用経験を通して得られた課題と具体的な 設計・構成法を提示し、フォーマルメソッドが産業界の問題を解決する「当然の技術」た る所以を示すことである. 本研究の基となる FeliCa IC チップ開発の概要について, 1.5 節で述べる.フォーマルメソッドとして、 形式仕様記述手法とモデル検査 <sup>[CGP99]</sup> を用い た. FeliCa IC チップ開発の仕様策定工程において形式仕様記述手法を用い, 仕様策定後 の設計工程においてモデル検査を用いた. モデル検査を用いることで. 形式仕様記述手法 では取扱いが容易でない動的な振る舞いを検証した. 本節に続く 1.3 節では形式仕様記 述手法について述べ. 1.4 節ではモデル検査について述べる.

#### 形式仕様記述手法 VDM 1.3

本節では、 筆者らが FeliCa IC チップ開発において用いた、 形式仕様記述手法の概要 を述べる. 仕様策定工程において, モデル指向型の形式仕様記述手法 VDM (Vienna Development Method) [BJ78, Jon90] を用いた. まず, 形式仕様記述手法 VDM について概 観した後に, VDM の統合開発環境である VDMTools について述べる. 最後に, 実行可能 仕様について議論する.

#### 1.3.1 形式仕様記述手法 VDM の概要

形式仕様記述手法とは、仕様を数学あるいは論理学で使われるような形式化(formalization)による抽象化を行う形式的な仕様化の技法である。形式化の方法により、モデル指向型と性質指向型に分類される。性質指向型とは仕様化の対象となるシステムの外から見た性質を公理的な方法で定義するものである。性質指向型の手法としては Larch [GHJ+93] や OBJ [Gog79] などの抽象データ型の代数仕様による意味定義の方法がよく知られている。一方、モデル指向型は、状態機械の仕様をその状態を構成するデータ構造と、それに対する操作の入出力仕様で定める方法である。モデル指向型の手法としては VDM(Vienna Development Method)[BJ78, Jon90]、Z 記法 [Abr96]、B メソッド [Abr96] が有名である。VDM には VDM-SL [ISO96] と、VDM-SL の言語仕様をオブジェクト指向に拡張した VDM++ [FLM+05] がある。VDM-SL は、1970 年代に IBM ウィーン研究所でプログラミング言語 PL/I コンパイラの正しさを検証するプロジェクトで用いられた技術を、一般の仕様記述向けに拡張したものである。1975 年から 1990 年代前半にかけて開発され、1996 年に ISO 標準となった [ISO96]。VDM-SL にオブジェクト指向と同時並行処理記述を付加した VDM++は、1990 年代前半にヨーロッパにおける ESPRIT 計画 の Afrodite プロジェクトの中で、産業界への適用を狙って開発された。

VDM-SL と VDM++ は, Floyd-Hoare 論理 [Flo67, Hoa69] における事前条件 (precondition) と事後条件 (postcondition) および不変条件 (invariant) によって仕様を記述する枠 組みを提供する.

#### 1.3.2 統合開発環境 VDMTools

VDM-SL と VDM++ には, 統合開発環境 VDMTools [SCS, 佐原+07] が SCSK 株式会社から提供されている. VDMTools は以下の機能を提供する.

• 仕様の構文検査 (syntax check)・型検査 (type check)

- 実行可能仕様のアニメーションを行うための評価実行とデバッグ支援

- 実行可能仕様のコードカバレッジ計測

- ソースコードの清書:コードカバレッジ情報を含んだ自然言語によるドキュメン トと VDM-SL, VDM++ のソースコードを混合させた文書を生成する

- 実行可能仕様から Java, C++ コードの生成

- 証明課題生成

- UML リンク: クラス図とソースコード、ソースコードとクラス図の双方向変換

- CORBA API : 実行可能仕様を CORBA サーバとして, C や Java のクライアント から呼び出して実行する

仕様の構文検査や型の検査により. 機械的な検証を行いながら仕様を記述することが できる. 実行可能仕様と仕様アニメーションについて, 次の1.3.3 節において説明する.

#### VDM++ による実行可能仕様 1.3.3

形式仕様記述言語は意味定義が厳密に決まっているため、言語処理系を構築し、仕様ア ニメーションにより検証を行うことができる. 仕様アニメーションとは. 記述した仕様を 言語処理系の上で実行することである. プログラムの実行と区別して, 仕様アニメーショ ンと呼ぶことが多い. 本論文では、仕様アニメーションよる実行可能な仕様を実行可能仕 様と呼び、形式仕様記述言語を用いて記述した仕様記述を形式仕様記述と呼ぶこととす る. VDMTools における. 実行可能仕様の記述例と実行可能ではない仕様の記述例を示 す. 次の (1) の記述は実行可能であり, (2) の記述は実行可能ではない.

- (1)  $\{x \mid x \text{ in set } \{5,6,7\} \& x > 5 \}$

- (2)  $\{x \mid x : nat \}$ & x > 5 }

- (1) は {5, 6, 7} に含まれる x のうち 5 より大きい数値の集合を表す式であり, 実行する ことができる. VDMTools の評価実行環境を用いて次のように実行する.

> print {x | x in set {5,6,7} & x > 5 }

{ 6,7 }

行頭の「>」は VDMTools がコマンド入力待ちであることを表す. 「 print 」は式を評価して結果を出力するという VDMTools の命令である. 評価した結果, {6, 7} を得る. 一方, (2) の記述は 5 より大きい自然数 (nat) の集合を表す式であり, 無限の値の集合は, VDMTools の評価実行環境の制約により実行することができない.

- 一般に記述した仕様を実行するためには次の2つの方法がある.

- 仕様記述を実行可能コードに変換して動作させる

- 仕様記述を解釈して動作させるインタープリタを構築する

仕様アニメーションによる検証の際に、いずれの方法を選択するかは、形式仕様記述言語ごとに提供されている統合開発環境が、実現するための機能を備えているか否かによる. VDMTools は C++ コード生成機能とインタープリタ機能の両方を備えており、前述の2つの方法を選択することができる.

インタープリタ機能を使用した場合、VDM++ コードを逐次解釈しながら実行する. C++ コード生成機能を使用した場合、VDM++ コードを最終的にマシン語に変換し、バイナリコードを実行する. あらかじめマシン語に変換する C++ コード生成機能を用いた方が、インタープリタ機能を使用した場合よりも、実行速度が速い. そのため、仕様アニメーションによる検証において、実行速度が課題となる場合、C++ コード生成機能を用いることを検討する必要がある. また、C++ コード生成機能により生成したコードを製品の実装コードとして使用できる場合、C++ コード生成機能を使用する利点がある.

しかし、C++ コード生成機能を使用する場合、インタープリタ機能を用いる場合よりも、仕様記述に用いることができる VDM++ の言語仕様 [SCS10] の制約が厳しくなる. 例えば、関数の引数に関数型を指定する高階関数を VDM++ は定義することができるが、C++ コード生成機能はこの高階関数には対応していない.

我々は、VDM++ コードの評価実行環境として VDMTools のインタープリタ機能を使用した。理由は、以下の 3 点である。(1) 仕様記述に高階関数を使用しており、C++

コード生成機能の言語仕様の制約を満たしていなかった. (2) インタープリタ機能を用いても実行速度は大きな課題とはならなかった. (3) FeliCa IC チップのファームウェア実装コードは,セキュリティ実装を行う必要があり, C++ コード生成機能を利用することができたとしても,出力した C++ コードをそのままファームウェア実装コードとして用いることはできなかった.

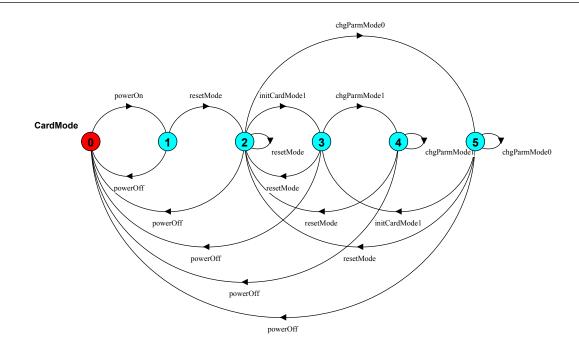

#### 1.4 モデル検査

本節では、筆者らが FeliCa IC チップ開発において用いた、フォーマルメソッドの1つであるモデル検査の概要を述べる. 仕様策定後の設計工程において、形式仕様記述手法では取扱いが容易でない動的な振る舞いについて、モデル検査を用いて検証を行った.

モデル検査とは、システムの仕様を表現したモデルがシステムに要求される性質を満たすかどうかを自動的に検証する手法である。特に並行性を含むシステムを対象に、モデルをラベル付き遷移システム(labelled transition system)で記述し、性質を時相論理(temporal logic)で表すものをモデル検査と呼ぶことが多い<sup>[CGP99]</sup>. 以下ではラベル付き遷移システムと時相論理について述べる。

ラベル付き遷移システムとは、記述対象の振る舞いを状態および状態間の遷移で構成されるグラフで表す。一般にこのグラフは状態遷移図と呼ばれ、遷移に動作(action)のラベルを付けたものである。時相論理とは、動作の進行順序に関する性質を表現する論理体系である。時相論理式で表現する主な性質として、安全性(safety)と活性(liveness)がある。安全性は、望ましくない事象がどのような遷移経路をたどっても決して起こらないという性質である。安全性の例としては、次の遷移が存在しないデッドロック(deadlock)や、リソースの排他アクセス違反などがある。

安全性を時相論理式で表すと次のようになる.

$AG \neg P$

ここで, A は「どのような遷移経路をたどっても」を意味する限量子であり, G は「いつでも」を意味する時相演算子, P は望ましくない性質を表す述語である.

活性は、望ましいことがいつか必ず起こるという性質である。望ましいことは、記述対象によって異なり、通常は仕様に記述される。例えば、本論文で述べる FeliCa IC チップにおいては、いつかは、処理を受け付けることができる受信待ちに戻ることといった性質である。

活性を時相論理式で表すと次のようになる.

#### AFQ

ここで、Fは「いつかは」を表す時相演算子であり、Qは望ましい性質を表す述語である。 モデル検査の技術は、ラベル付き遷移システムで表現したモデルを、網羅的に探索し、 時相論理式で記述した性質を満たしていることを自動的に調べる技術である。これにより、設計レビューやテストにより見つけることが難しい不具合を見つけることができる。 しかし、網羅的に全状態空間の探索を行い検証が終了するためには、ラベル付き状態システムとして記述する検査対象の状態数が有限である必要がある。また、コンピュータの性能向上や、アルゴリズムの工夫とともに、扱える状態数が実用的なものになってきてはいるが、状態数が、検証ツールを動かしているコンピュータのメモリに収まり、検証ツールが現実的な時間で計算を終えるように、検査対象を抽象化し、適切な規模の状態数としなければならない。

本論文では、FeliCa IC チップ開発の設計工程において、ハードウェア設計とソフトウェア設計をラベル付き遷移システムで表現することで、設計上の矛盾が起きないことをモデル検査を用いて検証した適用事例 [中津川+06] について述べる。特に、モデル検査の段階的な導入の方法と、検査対象の状態数の削減方法について述べる。

#### 1.5 本研究の基となるフォーマルメソッドの適用事例

本節では、本研究の基となる筆者らの FeliCa IC チップ開発への形式仕様記述手法の適用事例を紹介する。まず、FeliCa IC チップの特徴について述べ、形式仕様記述手法の適用に至る背景を説明する。次に適用における効果を統計データから論じ、最後に適用により得られた課題を述べる。3章以降では、これらの課題について議論を進め、課題に対

する解決策を提案する.

形式仕様記述言語 VDM++ により実行可能仕様を記述し、記述した仕様を仕様アニメーションにより動作検証を行った. 下流工程では仕様に基づくテストに形式仕様記述を活用した. 仕様記述の構文検査、型検査、仕様アニメーションには VDMTools を用いた.

#### 1.5.1 FeliCa IC チップの特徴

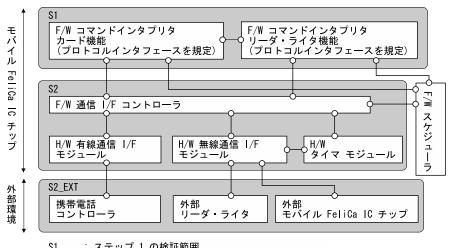

FeliCaとはソニー株式会社が開発した非接触ICカードの技術方式である「<sup>松尾の7</sup>」. FeliCa IC チップは非接触ICカードや、「おサイフケータイ」として知られる携帯電話に組み込まれており、電子マネーや公共交通機関の乗車券・定期券、クレジットカード、ドアの鍵、身分証などのサービスに応用されている。1つのICチップに複数のアプリケーションの搭載が可能なため、複数の事業者が1つのICチップを共用できる。本研究では、これらの電子マネーや乗車券、クレジットカードなどの用途としての機能を、FeliCaICチップのカード機能と呼ぶこととする。 FeliCaICチップのカード機能は、ファイルシステム機能は、セキュリティ機能、コマンド機能の3つの機能からなる。ファイルシステム機能は、複数のサービス事業者がICチップとの相互認証に使用する各事業者の鍵データや、電子マネーの残高などのユーザデータを保持・管理する機能である。セキュリティ機能は、リーダ・ライタと相互認証および暗号通信を行う機能である。コマンド機能は、リーダ・ライタと同日記証にを解釈する機能である。リーダ・ライタとは、店舗のレジ端末にあるような読み書きを行う装置である。

特に「おサイフケータイ」として知られる携帯電話に搭載された FeliCa IC チップをモバイル FeliCa IC チップと呼ぶ [杉山+07]. モバイル FeliCa IC チップには, 前述のカード機能に加え, リーダ・ライタ機能が搭載されている. リーダ・ライタ機能により, 店舗のレジ端末にあるような読み書き装置として, モバイル FeliCa IC チップを使用することができる. また, モバイル FeliCa IC チップは, リーダ・ライタからモバイル FeliCa IC チップにアクセスすることができる無線通信インタフェース機能と, 携帯端末側からモバイル FeliCa IC チップにアクセスすることができる有線通信インタフェース機能を備

えている. 本論文では、モバイル FeliCa IC チップを含めて FeliCa IC チップと呼ぶ. 以下に、FeliCa IC チップ開発の特徴と形式仕様記述手法の適用に至る背景を示す.

- FeliCa IC チップは広く社会基盤の一部として利用され、製品開発における品質確保が重要な課題である.

- FeliCa IC チップは同一の仕様を複数のハードウェアプラットフォームに実装して おり、製品間の相互接続性を確保するためには、仕様の厳密性が求められる.

- FeliCa IC チップは様々な耐タンパ機能を搭載しており、セキュリティ製品として 全ての入力に対して正常系、準正常系の振る舞いを厳密に定義する必要がある.

これらの背景から、仕様を簡潔かつ厳密に記述することができる形式仕様記述手法に 着目した.

#### 1.5.2 開発プロジェクトの概要

筆者らは、次に示す 2 つの製品開発プロジェクトにおいて形式仕様記述手法を適用した. 1 つ目は、モバイル FeliCa IC チップ開発プロジェクトである. これは、フェリカネットワークス株式会社にて、2004 年から 2007 年の期間で行った開発プロジェクトである. この開発プロジェクトに形式仕様記述手法を用いた [栗田+06、KCN08、KN09、栗田+09]. 2 つ目は、カード開発プロジェクトである. これは、ソニー株式会社にて、2007 年中頃から約 4 年間の期間で行った開発プロジェクトである. いずれの開発プロジェクトにおいても、上流工程の仕様記述に形式仕様記述言語 VDM++ を用い、記述した実行可能仕様を用いて仕様アニメーションにより動作検証を行い、下流工程では仕様に基づくテストに形式仕様記述を活用した.

本研究では、1度目のモバイル FeliCa IC チップ開発における形式仕様記述手法の適用を第 1 世代の適用と呼び、2 度目のカード開発における適用を第 2 世代の適用と呼ぶこととする。第 1 世代の適用を通して、仕様記述手法を用いることにより得られる効果に対して確信を持ち、また適用における課題が明確になった。第 2 世代では、第 1 世代において得られた課題を考察し、課題を解決する形式仕様を記述することができた。

|            | 有効行数 (行) |        |  |

|------------|----------|--------|--|

| モジュール名     | 第1世代     | 第2世代   |  |

| コマンド機能     | 26,370   | 11,460 |  |

| ファイルシステム機能 | 5,097    | 1,716  |  |

| セキュリティ機能   | 821      | 1,548  |  |

| 記述フレームワーク  | 3,011    | 425    |  |

| 汎用ライブラリ    | 1,305    | 648    |  |

| 合計         | 36,604   | 15,797 |  |

表 1.2 第 1 世代と第 2 世代の形式仕様記述の規模

本章では、第1世代の適用を通して得られた成果と課題について述べる. 以降の章において、第2世代の適用を通して得られた、第1世代の課題に対する解決方法を提案する [中津川+09, 中津川+10, NKA10]. また、第1世代において、仕様策定工程に形式仕様記述手法を用いたが、形式仕様記述手法では取扱いが容易でない動的な振る舞いに関して、設計工程においてモデル検査を適用した. この動的な振る舞いに関するモデル検査による設計検証についても、本章以降の章において述べる [中津川+06].

#### 1.5.3 形式仕様記述手法の適用対象と規模

形式仕様記述手法の適用対象は FeliCa IC チップの仕様書である. 第 1 世代と第 2 世代の形式仕様記述の規模を 表 1.2 に示す. 第 1 世代の対象製品は, リーダ・ライタ機能などの機能を搭載しているモバイル FeliCa IC チップであり, 第 2 世代の対象製品は,カード機能のみを搭載している FeliCa IC チップである. 形式仕様記述の有効行数は,第 1 世代が約 37K であり第 2 世代は約 16K である. ここでいう有効行数とは,総行数からコメント行と空行を除いた行数である. 第 2 世代に比べ第 1 世代の方が製品に搭載されている機能が多いため仕様の規模が大きくなっている. 共にコマンド機能が約 7 割を占め,主要な仕様記述モジュールとなっている.

| 不具合発見工程                    | 不具合件数 (件) |

|----------------------------|-----------|

| 自然言語で仕様記述する過程で見つけた不具合      | 93        |

| 形式仕様記述言語で仕様を記述する過程で見つけた不具合 | 162       |

| 仕様アニメーションを実施して見つけた不具合      | 116       |

| ドメインエンジニアと形式仕様記述者の         |           |

| コミュニケーションにより見つけた不具合        | 69        |

| 合計                         | 440       |

表 1.3 摘出工程別の仕様不具合件数

#### 1.5.4 適用における効果

第1世代の形式仕様記述手法の適用により様々な効果が明らかになった。ここでは、本 論文の背景となる2つの効果について述べる。

1 つは、形式仕様記述手法を適用しなければ摘出が困難な不具合を早期に摘出し、後工程における手戻りを減らし、開発スケジュールの遅延、コストの超過を防ぐことができた点である。実行可能仕様を動かして仕様アニメーションによる検証を行うことで、上流工程において早期に仕様不具合を見つけることができた。上流工程における不具合を後工程で修正した場合の修正コストは、上流工程で修正した場合の数 10 倍から数 100 倍と言われている [Lef97、SBB+02]。そのため、早期に不具合を摘出することは、後工程における手戻りを減らし、品質の高いソフトウェアを開発する上で重要な活動である。

表 1.3 に上流工程において摘出した仕様の不具合件数を示す. 形式仕様記述言語で仕様を記述する過程で見つけた不具合 162 件, 仕様アニメーションを実施して見つけた不具合 116 件は形式仕様記述手法を導入しなければ見つけることが難しい不具合であり,後工程において手戻りとなる可能性があった. 形式仕様記述手法を導入することにより,設計・テストが開始する前の上流工程において多くの不具合を見つけることができた. これらの経験から,第 2 世代においても実行可能仕様を用いる方針とした.

2つ目の適用における効果は、仕様策定、設計、実装、テストと作業分担を行い複数人で

開発するプロジェクトにおいて、厳密な仕様をコミュニケーションツールとして用いる ことができた点である.

仕様策定工程において、自然言語と形式仕様記述言語をそれぞれ用いて、FeliCa IC チップの仕様書を作成した。これら2つの仕様書は、それぞれで個別に完結した仕様書となっている。自然言語で記述した仕様を入力として、形式仕様記述言語を用いてより詳細な仕様を記述した。形式仕様記述言語を用いることで、曖昧な仕様を見つけることができた。これにより、自然言語の曖昧な記述を修正することができた。

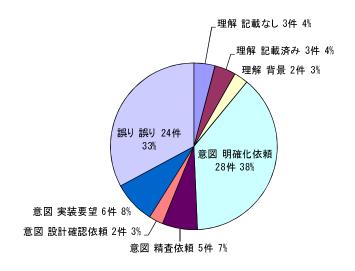

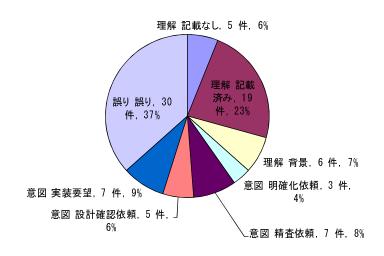

コミュニケーションの 1 つの側面として、これらの自然言語の仕様書と形式仕様記述言 語の仕様書への質問内容を分析した. 質問内容の分析は, 両者の質問を分類し, 傾向を比 較することにより行った. 図1.2 に自然言語の仕様書に対する質問の分類結果を、図1.3 に形式仕様記述言語の仕様書に対する質問の分類結果を示す. 質問の分類方法を以下に 示す. まず質問を「理解」, 「意図」, 「誤り」の 3 つに分類した. 質問者が「理解した い」という考えを持った質問を「理解」とし、理解はしているが「理解以外の意図」を 持った質問を「意図」とし、単純に誤りを指摘した質問を「誤り」と分類した。さらに 「理解」を「記載済み」,「記載なし」,「背景」に分類し,「意図」を「明確化依頼」, 「精査依頼」, 「設計確認依頼」, 「実装要望」に分類した. 「理解」の「記載済み」と 「記載なし」は質問に関する回答が仕様書に記載済みか、 記載なしかにより分類し、 「な ぜこのような仕様になっているか」という質問を「背景」と分類した. 「意図」に分類 した質問について、仕様は明確ではあるが記載内容を明確にして欲しいという「明確化 依頼」、仕様の間違いではないが統一性がないなどの仕様を精査して欲しいという「精 査依頼」, 設計者からの設計が仕様を満たしていることを確認して欲しいという「設計 確認依頼」, 設計・実装情報を仕様にも反映して欲しいという「実装要望」に分類した. 図1.2、図1.3を比較すると、コミュニケーションの傾向が分かる. 自然言語の仕様書に 対しては, 「明確化依頼」が占める割合が最も多く, 形式仕様記述言語を用いた仕様書に

対しては、「明確化依頼」が占める割合が最も多く、形式仕様記述言語を用いた仕様書に対しては、「記載済み」の内容に関する「理解」に分類した質問の割合が多かった。自然言語と形式仕様記述言語で書かれた仕様は同じ「理解」に分類される質問が多いが、コミュニケーションの質が異なる。占める割合が最も多い自然言語の仕様書に対する「明

図 1.2 自然言語の仕様書に対する質問の分析

確化依頼」の質問は、「書かれていない」、「明確になっていない」ことを「記載してもらう」、「明確にしてもらう」ための質問である.一方、形式仕様記述言語の仕様書に対しては、「記載済み」の内容、背景に関する質問が占める割合が多いことから、読み手が仕様をより深く理解するための質問であることが分かる.また、形式仕様記述の場合、コミュニケーションにより理解したことが既に「記載済み」の内容として厳密に定義されているということは、開発者に安心感を与える効果があった.

#### 1.5.5 適用における課題

形式仕様記述言語 VDM++ により実行可能仕様を記述し、仕様アニメーションにより動作検証を行った。下流工程では仕様に基づくテストに形式仕様記述を活用した。これらの形式仕様記述言語を用いた開発において次の3つの課題が明らかになった。本節ではこれらの課題について考察する。

- (1) 「伝えること」と「動かすこと」を目的とした実行可能仕様の課題

- (2) 仕様と設計の分離に関する課題

- (3) レビューとテストの用途として形式仕様記述を利用する場合の課題

図1.3 形式仕様記述言語の仕様書に対する質問の分析

(1) と (2) は、形式仕様記述の読みやすさに関する課題である。図 1.3 の「記載済み」の内容に対する質問の占める割合が多い点から、読みやすい仕様を書くことが課題であることが分かる。

まず、(1)の課題について述べる.上流工程において記述した形式仕様を、仕様アニメーションにより動作検証を行った.そのため、仕様として「伝えること」を目的とした記述と「動かすこと」を目的とした記述が混在したため、仕様の読みやすさが課題となったと考えた.したがって、1つ目の課題として、「伝えること」と「動かすこと」を目的とした実行可能仕様について考察することとした.詳細は、2.1.1節で述べる.

次に (2) の課題について述べる. 仕様と設計の境界が曖昧であったため, 仕様の読みやすさが課題となったと考えた. これは, 第1世代の開発中において, 仕様策定者と設計者の間で議論になったことである. 議論の内容は, 形式仕様記述から仕様として規定している範囲と, 形式仕様記述には記述してはあるが, 設計者が自由に規定できる範囲を, 設計者が読み取ることが難しいということであった. したがって, 2 つ目の課題として仕様と設計の分離に関する課題について考察することとした. 詳細は, 2.1.2 節で述べる.

最後に(3)の課題について述べる. 第1世代では, 仕様に基づくテストにおいて, 製品に対して実行したテストスクリプトを VDM++ のソースコードに変換することにより, 形式仕様記述に対しても実行することができるようにした. これにより, 製品に対して実

行したテストスクリプトの形式仕様記述に対する網羅性を確認した. テスト設計, テスト項目作成においては, 形式仕様記述を参照するにとどまった. 第2世代では, 第1世代よりも広く形式仕様記述を使うことを目標とした. そこで, 仕様に基づくテストとレビューに着目し, 形式仕様記述の利用方法をあらかじめ考慮して, 形式仕様記述フレームワークを設計していく方針とした. したがって, レビューとテストの用途として形式仕様記述を利用する場合の課題について考察した. 詳細は, 2.2節で述べる.

このように、第1世代の適用において、前記の3つの課題が明らかになり、第2世代において解決すべき目標を設定することができた.

#### 1.6 本論文の構成

本論文の構成は、以下のとおりである.まず 2 章では、フォーマルメソッドを適用す る上で課題となった, 本研究において扱う次の 3 つの課題を分析する. 1 つ目の課題は, 1.5.5 節において述べた (1) と (2) の課題に関連する実行可能仕様における仕様と設計の 分離に関する課題である. 2 つ目の課題は, 1.5.5 節において述べた (3) の課題に関連す る、レビューとテストの用途として、形式仕様記述を利用する場合の課題である. 3つ目 の課題は、形式仕様記述手法では取扱いが容易でない動的な振る舞いに関する課題であ る. 次に, 3 章では, 関連研究として, 産業界へのフォーマルメソッドの適用事例につい て概観し、筆者らのフォーマルメソッドの適用事例について考察する. また、1 つ目の課 題である、実行可能仕様における仕様と設計の分離に関する関連研究から、本研究で扱う 課題をさらに考察する.続いて, 4 章から 6 章では, 2 章において述べた 3 つの課題につ いて、本研究において得られた成果を述べる. 4章では、1つ目の課題である実行可能仕 様における仕様と設計の分離に関する課題を解決する、実行可能仕様の設計・構成法を 提案する. 5 章では, 2 つ目の課題であるレビューとテストの用途に, 形式仕様記述手法 を活用する場合の課題を解決する,仕様記述フレームワークの設計・構成法を提案する. また、仕様に基づいたテストへの、形式仕様記述の活用方法を提案することで、本論文で 提案する仕様記述フレームワークがテストの用途を考慮していることを示す. 6 章にお

23

いては、形式仕様記述手法では取扱いが容易でない動的な振る舞いに関して、モデル検査を用いた設計検証の適用事例について述べる。7章では、それまでの議論をまとめ、今後の展望を示す。

## 第2章

## 本研究において扱うフォーマルメソッド の適用における課題

1章では、組織的に開発を進める必要があるソフトウェア開発現場において、上流工程の文書を中心に多くの問題を抱えており、品質の高いシステムを組織的に効率よく開発することができる手法として、フォーマルメソッドが注目されていることを述べた。フォーマルメソッドの3段階の適用レベルにおいて、本研究が扱うのは、形式仕様記述を行うレベル0である。レベル0は、証明までは行わないが、数学的な記法を用いて厳密な仕様を記述し、プログラムを開発していく段階である。このレベル0の段階において、筆者らはモバイル FeliCa IC チップ開発を通して適用の効果を得ることができた。しかし、産業界は多くの問題を抱えているにもかかわらず、フォーマルメソッドが、ありふれた「当然の技術」として産業界に浸透していないという Parnas の指摘を紹介し、「当然の技術」として浸透するための課題を分析した。分析において、適用レベルをレベル0からレベル0-a とレベル0-b の2 つに分けた。レベル0-a は、形式仕様の記述者が、形式仕様記述手法を用いて仕様を厳密に記述し、早期に仕様の曖昧さに起因する不具合を見つけることができるという段階とした。レベル0-b は、形式仕様の記述者以外である、ドメインエンジニアや設計者、実装者、評価者が、形式仕様記述を参照し、形式仕様記述に基づいて設計と実装とテストを行う適用の段階とした。開発プロジェクトの中で形式仕様記述を活

用する人は、レベル 0-a においては、形式仕様の記述者のみの限られた人であるが、レベル 0-b においては、ドメインエンジニア、設計者、実装者、評価者といったほぼ全ての工程の人たちとなる。これらの人たちが形式仕様記述手法をあらかじめ習得していることは希であり、形式仕様記述手法の専門家ではない人が、形式仕様記述を読み、理解し、活用していく必要がある。つまり、形式仕様記述手法の専門家ではない人が、読みやすいと感じ、形式仕様記述手法を利用することにメリットを感じるような、形式仕様を記述するための技術と、活用するための技術が必要である。この課題を解決することで、形式仕様記述手法がありふれた「当然の技術」として、開発プロジェクトにおいて広く活用されるようになり、さらには、産業界においても広く活用されることにつながると考える。

本研究では、前述のレベル 0-b の段階に到達するために必要な、形式仕様を記述するための技術と、活用するための技術を研究課題として設定した。記述するための技術として、ドメインエンジニア、設計者、実装者、評価者といった様々な役割を担った開発者にとって、理解容易性に優れた仕様を記述する技術が必要である。活用するための技術としては、従来からある既に開発現場に浸透しているレビューやテスト手法といった検証技術を主体として、その中で形式仕様記述手法を活用していく技術が必要である。本章では、これらの課題を具体化する。本研究において扱う課題は次の3つである。

- (1) 実行可能仕様における仕様と設計の分離に関する課題

- (2) レビューとテストの用途として、形式仕様記述を利用する場合の課題

- (3) 形式仕様記述手法では取扱いが容易でない動的な振る舞いに関する課題

- (1), (2) は, レベル 0-b の適用段階において, 形式仕様を記述するための課題と, 活用するための課題である. (3) は, レベル 0-b の議論とは別の, 仕様策定後の設計工程における課題である. 以降の節において, それぞれについて議論する.

#### 2.1 実行可能仕様における仕様と設計の分離に関する課題

#### 2.1.1 「伝えること」と「動かすこと」を目的とした実行可能仕様の課題

レベル 0-b の段階において, 形式仕様記述の読者は, 形式仕様記述手法の専門家ではない, ドメインエンジニア, 設計者, 実装者, 評価者といったほぼ全ての工程の人たちとなる. 開発工程の上流工程である仕様策定工程において, 品質の高い仕様書を作成することで, その後の設計, 実装, テスト, 運用, 保守を正確かつ組織的に行うことができるため, 開発効率を高めることができる.

仕様書には何を作るべきかという「解決すべき問題」を定義することで、仕様策定工程以降の設計、実装、テスト、運用・保守工程では、仕様書を参照し、各工程において実施すべきことを決める。設計工程では仕様書を参照して「問題の解決方法」を検討し、設計書を作成する。つまり、仕様書の役割は、何を作るべきかという「解決すべき問題」を各工程に明確に「伝えること」である。

形式仕様記述言語を用いて仕様を厳密かつ簡潔に記述することにより、仕様書の理解容易性を高めることが期待できる。また、形式仕様記述言語を用いて記述した場合、記述の意味が厳密に定義されているため、言語処理系を構築し、仕様アニメーションにより仕様を「動かすこと」で検証を行うことができる。実行可能仕様を記述することにより、上流工程において仕様を検証し、早期に不具合を摘出し、後工程における手戻りを減らすことができる。また、仕様アニメーションによる検証は、開発現場に既に浸透している検証手法であるテストの技術を流用することができるため、証明などと比べると導入が容易である。

しかし,実行可能仕様には,注意すべき問題があることが知られている. 仕様書の役割は,何を作るべきかという「解決すべき問題」を各工程に明確に「伝えること」である. 実行可能仕様により,この「伝えること」を目的とした記述と,仕様アニメーションにより「動かすこと」を目的にした記述が混在することになる. 2 つの記述が混在することにより,本来は「解決すべき問題」を規定する仕様に,「問題の解決方法」としての記述が多く含まれてしまう. これにより,設計者を過剰に制約し,実装の選択肢を狭めてしま

う可能性がある。また、「問題の解決方法」の記述が多く含まれることにより、仕様の記述が複雑になってしまう傾向がある。

理解容易性に優れた仕様を記述するためには、「伝えること」を目的とした記述を明確にする必要がある。そのため、これを妨げる「動かすこと」を目的とした記述が課題となる。一方、従来からある既に開発現場に浸透しているテスト手法を用いて、仕様アニメーションにより実行可能仕様を活用するためには、「動かすこと」を目的とした記述が必要である。これらの課題を解決するために、本研究では「伝えること」を目的とした記述と、「動かすこと」を目的とした記述を明確に分離する方法を提案する。3.2節において、関連する Ian J. Hayes と Cliff B. Jones の「実行可能性の影響」に関する研究 [HJ89] から課題をさらに考察する。4.1 節において提案方法の詳細を述べる。

#### 2.1.2 仕様と設計の分離に関する課題

一般に、仕様策定工程では、何を作るべきかという「解決すべき問題」を検討し、設計工程では、「問題の解決方法」を検討することで、仕様策定者と設計者が分業して組織的に開発を行うことができると言われている。この「解決すべき問題」と「問題の解決方法」の対比を、「何を(What)」と「どのように(How)」の対比として捉えることで、ソフトウェア開発では「What と How を分けて考えるとよい」と言われている。これは、仕様策定工程では What を検討することに集中し、設計工程では How に集中するということである。本論文では、この「解決すべき問題」である What と「問題の解決方法」である How を分けて考えることを、仕様と設計の分離と呼ぶこととする。

仕様と設計を分離することは、ソフトウェア開発において広く言われていることではあるが、実際に、仕様策定者が仕様と設計を分離して仕様を検討し、仕様書に「解決すべき問題」のみを簡潔に記述することは容易ではない。仕様と設計の境界が曖昧な仕様書が設計者に渡された場合、設計者は、仕様が規定する範囲と設計が規定すべき範囲を仕様書から読み取ることができない。仕様書内の実現手段を含んだ記述について、設計の自由度がどこまであるのかを設計者は仕様策定者に尋ねなければならない。仕様策定工程

において、この仕様と設計の分離について十分に議論されていることは少ないため、仕様 策定者は設計者の質問に答えられない、あるいは、仕様と設計の分離に関する議論が仕様 書の広範囲に渡るため、個別に答えることが難しい場合が多い。この場合、結局のところ、 仕様と設計の分離に関する検討は、仕様の読み手である設計者任せとなることが多いた め、仕様策定者が意図した仕様とは異なる製品が設計されてしまう場合や、設計者が仕様 の制約を過剰に解釈し複雑な設計となる場合がある。その結果、開発効率が低下してしま う問題や、製品のパフォーマンスに影響を与えてしまう問題、不具合や市場トラブルの問 題を引き起こす可能性がある。

以上のことから、仕様策定工程において、仕様が規定する範囲と設計が規定する範囲を設計者が容易に読み取ることができ、理解容易性に優れた形式仕様を記述する必要がある。本研究では、開発対象の内部データ構造に着目することで、仕様と設計を分離する方法を提案する。3.3 節において、関連する Michael Jackson の「実装の影響」に関する研究 [Jac95] から課題をさらに考察し、4.2 節において解決方法を提案する.

# 2.2 レビューとテストの用途として形式仕様記述を利用する場合の課題

#### 2.2.1 レビューとテストにおける一般的な課題

現在, ソフトウェア開発においてレビューとテストが産業界において「当然の技術」として広く用いられている. しかし, レビューとテストには様々な課題があることが知られている. 主な課題を以下に示す.

- 一般にテストは設計と実装の後に行われるため、テストにより仕様の不具合が見つかった場合の手戻りが、上流工程で不具合を見つけた場合と比較して大きくなる.

仕様に関する不具合が下流工程で実施するテストにより見つかることで、手戻りが発生することが課題である.

- ソフトウェア開発において正しさは相対的であり [Mey00], ソフトウェアが正しいこ

とを確認するには基準が必要である. 仕様は、テストとレビューにおいて正しさの 基準となる.そのため、 仕様が曖昧であると、 レビューとテストにより不具合を見 つけることが難しくなることが課題である.

レビューは品質確保の主要な手段であり、ソフトウェア開発において品質確保に効 果があることが知られている [MDL87, MST11]. しかし, 繰り返し機械的に実施できな いため、変更が入った場合のレビューの運用と、レビューによる検証の網羅性が課 題となる.

これらの課題に対して. 形式仕様記述手法を適用することにより. 以下の効果を期待す ることができる.

- 上流工程で形式仕様記述言語を用いて仕様を記述することにより、テストによる検 証手段を仕様アニメーションにより用いて, 早期に不具合を見つけることができる.

- 形式仕様記述言語を用いて厳密に仕様を記述することにより,正しさの基準として の仕様を明確に定義することで、テスト工程を担当する評価者に正しさの記述を明 確に伝えることができる.

- 形式仕様記述言語を用いて仕様を記述することにより、仕様の構文検査、型検査、単 体テストなどの機械的な検証手段を用いることができる.

これらの広く知られた形式仕様記述手法の効果は、FeliCa IC チップ開発の第1世代の 適用において経験することができた、以降の各節において述べる課題は、上記のテストと レビューにおける一般的な課題とは異なる. 以降で述べる課題は. 第 1 世代の形式仕様 記述手法の適用において明らかになったことにより、第2世代において取り組んできた ものである.

#### 2.2.2 レビューの用途から見た仕様記述の理解容易性に関する課題

開発プロジェクトにおいて、 ドメインエンジニア・仕様策定者・設計者・実装者・評 価者など、様々な役割を担った読者が仕様書を参照する。また、仕様を読む目的によって、 これらの読者が必要とする仕様の詳細度は異なる. 仕様が要求を満たしていることをドメインエンジニアがレビューする場合に必要となる仕様の詳細度と, 設計者と実装者が, 仕様と実装コードをレビューする場合の詳細度は異なる. ドメインエンジニアが必要とする仕様の詳細度と比べ, 設計者と実装者の方が, より細かい詳細度の仕様が必要となることが多い. 評価者が, 仕様とテスト項目表をレビューする場合も, ドメインエンジニアよりも細かい仕様の詳細度を必要とすることが多い.

様々なレビューの目的を持った仕様書の読者にとって、読みやすい仕様書とは、次の3つの課題を解決したものであると考える.

- 概要と詳細を階層化して明確に区別して記述してあり、概要のみを読むことで、仕様の全体像を理解することができる仕様記述.

- 概要から詳細へと即座にたどることができる仕様記述.

- 形式仕様記述手法の専門家ではない開発者であっても, 仕様を読み進めることができるように、特に概要の記述は簡潔な構造を持つ仕様記述.

このような仕様であれば、ドメインエンジニアが要求を満たしていることを確認するために、まず仕様の概要を読み進め、必要に応じて概要から詳細を読むことができる。実装者と設計者と評価者は、概要を把握した上で、概要と詳細な条件式を往き来しながら、仕様を読み進めることができる。

本研究では、レビューの用途を考慮した、前述の3つの課題を解決する仕様記述フレームワークの設計・構成法を提案する. 提案手法の詳細を5.1 節において述べる.

#### 2.2.3 仕様に基づくテストの用途から見た課題

本節では、形式仕様記述を仕様に基づくテストの工程において、形式仕様記述手法を活用するための課題について考察する.

一般に、要求から考えた利用シーケンスをテストスクリプトとして記述し、仕様アニメーションによりテストスクリプトを形式仕様に対して実行することで、要求通りに仕

様が記述されていることを確認することができる。これにより、テストスクリプトとして記述した要求を、仕様が満たしていることを確認することができる。本研究において述べる仕様に基づくテストとは、前述の仕様が要求を満たしていることを確認することではなく、開発対象の実装が、仕様を満たしていることを確認するテストである。一般に、実装が仕様を満たしていることを確認するために、仕様書を基にテスト項目とテストスクリプトを作成し、開発対象の実装に対してテストスクリプトを実行する。本研究では、この方法を形式仕様記述に応用する。まず、形式仕様記述を基にテスト項目とテストスクリプトを作成する。次に、作成したスクリプトを形式仕様記述に対して仕様アニメーションにより実行して、テストの実行ログを得る。最後に、形式仕様記述に対して生様アニメーションにより実行して、テストの実行ログをとしまり、開発対象の実装が、仕様を満たしていることを確認する。ここで述べたテストの実行ログとは、開発対象への入力データや開発対象の出力データ、デバッグのために開発対象から出力した内部状態のデータなどである。

仕様に基づくテストの工程において、形式仕様記述手法を活用することで、メリットを 感じることができるように、本研究では次の 2 つの研究課題を設定した.

- まず、仕様に基づくテストにおいて前提とする品質目標を決める. その上で、品質目標を満たす体系的なテスト項目の作成方法を研究課題とした. これは、体系的にテスト項目を作成することができるような、形式仕様記述の設計を行わなければならないことでもある.

- テスト項目とテストスクリプトが品質目標を満たしていることを,形式仕様記述を 用いた機械的な処理により確認する方法を研究課題とした.

5章において、本研究において定めた仕様に基づくテストの品質目標と、体系的にテスト項目を作成するためのテスト設計および、そのための仕様記述フレームワークを提案する。そして、テスト項目とテストスクリプトが、品質目標を満たしていることを確認するための、ログ出力による機械的な検証方法を提案する。

## 2.3 形式仕様記述手法では取扱いが容易でない動的な振る 舞いに関する課題

形式仕様記述手法を用いることで、仕様策定工程において早期に仕様の検証を行うことができた.形式仕様記述手法の検証対象は、入力データに対する内部状態の遷移と出力するデータの仕様を記述した、静的な機能仕様である.形式仕様記述手法を用いることで、早期にこれらの機能仕様を検証することができた.しかし、同時並行に動作する動的な振る舞いについて、筆者らが用いてきた形式仕様記述手法では取扱いが容易ではなかった.

そこで、第1世代の FeliCa IC チップ開発における仕様策定後の設計工程において、同時並行に動作する動的な振る舞いに関する検証方法を検討する必要があった。検証方法としてモデル検査に着目した。本研究では、モデル検査の段階的な導入方法と、モデル検査を実施する上で課題となった、検査対象の状態数の削減方法について議論する。詳細を6章において述べる。

## 第3章

### 関連研究

本章では、関連研究として産業界へのフォーマルメソッドの適用事例について概観し、 筆者らのフォーマルメソッドの適用事例について考察する。また、2章において述べた本 研究で扱う3つの課題のうち、次の2つの課題に関する関連研究について述べる。1つ は、2.1.1節において述べた「伝えること」と「動かすこと」を目的とした実行可能仕様 の課題であり、2つ目は、2.1.2節において述べた仕様と設計の分離の課題である。これら の関連研究から、本研究において扱う課題を考察し、関連研究と本研究の提案手法を比較 する。

#### 3.1 フォーマルメソッドの産業界への適用事例

本節では、フォーマルメソッドの適用事例を紹介する.フォーマルメソッドの適用事例として、CICS [HK91]、CDIS [Hal96]、パリの地下鉄とシャルル・ド・ゴール国際空港のシャトル [Abr06] などが有名である.本節では、これらの事例について述べた後に、1.5 節で述べた筆者らの FeliCa IC チップ開発への形式仕様記述手法の適用事例と他の適応事例を比較する.

#### 3.1.1 CICS

1980 年代に英国 IBM ハーズレー研究所とオックスフォード大学は, IBM 社のオンライントランザクション管理システム CICS (Customer Information Control System) のシステム改版時に Z 記法を仕様記述と設計に用いた [HK91]. システムの改版では, 全体として 800K LOC (Line of Code) のうち, 268K LOC を新規作成もしくは変更した. このうち, Z 記法を用いて仕様策定と設計を行った範囲はおよそ 37K LOC である.

Z 記法を用いることにより、品質改善と開発コストの削減を達成することができたとしている. Z 記法を用いたコードと、用いなかったコードの開発ライフサイクルごとの不具合検出率を比較したところ、Z 記法を用いたコードの方が早期にバグを見つけることができた. 不具合を修正するのに費やした日数を基に開発コストを IBM が見積もったところ、Z 記法を用いた箇所は Z 記法を用いていない箇所と比較して開発コストを 9% 削減することができたとしている.

その後、CICS の成功によりオックスフォード大学と IBM 社は 1992 年に英国の賞「The Queen's Award for Technological Achievement 1992」を受賞した.

#### 3.1.2 CDIS

英国の Praxis 社は、ロンドン国際空港の航空管制システムの一部である CDIS (CCF Display Information System) の開発にフォーマルメソッドを用いた [Hal96]. CCF とは、中央管理機能 (Central Control Function) の略称である. CDIS は、航空機の発着、空港の気象条件や設備の状態、データ入力スタッフが提供するサポート情報を表示する装置であり、フォールトトレラントシステムである. 1992 年に Praxis 社から UK Civil Aviation Authority に納入された. CDIS の規模は 197K LOC であり、総工数は 15,500 人目であった.

機能要求の記述には VDM を用い,システム仕様の記述には VVSL<sup>[Mid89]</sup> を用いた. VVSL は VDM から言語仕様を拡張し,モジュール構造をより明確に記述できるようにした仕様記述言語である.システム仕様は,「フォーマルコア仕様」,「ユーザーインタ

フェース定義」、「同時並行仕様」の3つの記述からなる。「フォーマルコア仕様」は、CDISによって管理されているデータと、それぞれの操作に関する仕様である。それぞれの操作は、入力と出力、状態への影響を意味定義レベルで定義している。これらの操作は、「ユーザインタフェース定義」で記述している操作と結びついている。「ユーザインタフェース定義」は、ユーザと装置間におけるCDISの操作に必要なやりとり、必要なキー操作やマウス操作、スクリーンの表示に関して記述している。「同時並行仕様」は、CDISのユーザ入力装置や外部システムおよび故障と復旧を監視しているハードウェア装置などの同時並行に実行されているプロセスの仕様であり、CSP[Hoa78]と VVSLを用いて記述した。

全体の生産性は、同等規模の類似する開発プロジェクトと比較して同程度かもしくは良い結果となった。品質の面では、出荷後 20 ヶ月で 150 件の不具合が報告され、不具合密度は約 0.75 件/KLOC であった。これは、同程度のプロジェクトと比較するときわめて少なかった。

#### 3.1.3 パリの地下鉄とシャルル・ド・ゴール国際空港のシャトル

Jean-Raymond Abrial らはパリの地下鉄とシャルル・ド・ゴール国際空港のシャトルの開発にBメソッドを用いて自動運行制御システムを開発した [Abr06]. Bメソッドは, 抽象的な形式仕様を段階的に具体化して, 実行可能なプログラムを作成する段階的詳細化の開発法である. この適用事例において, 仕様から段階的詳細化により Ada プログラムを導き出している. 表 3.1 に概要を示す.

#### 3.1.4 本適用事例との比較

本研究において述べる筆者らのフォーマルメソッドの適用事例および、設計・構成法に関する提案は、Abrial らの B メソッド適用事例のように、抽象的な形式仕様を段階的に具体化して、実行可能なプログラムを作成する段階的詳細化による開発法とは異なる。産業界には、レビューやテストといった従来からある実践的な検証技術が既に浸透して

|           |        | シャルル・ド・ゴール |

|-----------|--------|------------|

| 項目        | パリの地下鉄 | 国際空港のシャトル  |

| Ada の行数   | 86,000 | 158,000    |

| 証明の数      | 27,800 | 43,610     |

| 対話的な証明の割合 | 8.1%   | 3.3%       |

| 対話的証明の工数  | 7.1 人月 | 4.6 人月     |

表 3.1 パリの地下鉄とシャルル・ド・ゴール国際空港の適用事例

J.R. Abrial 「Formal methods in industry 」 [Abr06] より引用

いる. 筆者らは、これらの実践的検証技術を主体として、その中にフォーマルメソッドを 組み合わせた検証手法を提案する. フォーマルメソッドを用いたソフトウェア開発の最 終的な目標は、要求、仕様、設計、実装と各ステップにおいて正しさを保証し、正しさを保 証しながら開発のステップを進めていく、Correctness by construction の考え方である. しかしながら、現状は誰もがすぐに Correctness by construction の考え方に従って開発 を行える環境ではない. 各々の開発現場においては、既に蓄積してきたレビューやテスト 手法などの検証技術があり、その検証技術を主体としてフォーマルメソッドを用いた開 発法を議論することで、開発現場の多くの課題を解決することができると考える. 本研 究では、従来からある検証技術の中にフォーマルメソッドを適用した事例について述べ、 適用に必要な設計・構成法の提案を行う.

#### 3.2 実行可能仕様における「実行可能性の影響」

2章において、本研究において扱う課題について考察した。本節では、これらの課題のうち、2.1.1節において述べた、「伝えること」と「動かすこと」を目的とした実行可能 仕様の課題について述べる。この、仕様の実行可能性が仕様記述に与える影響に関する関連研究から、課題を考察し、関連研究と本研究において提案する手法とを比較する。

実行可能仕様には、何を作るべきかという「解決すべき問題」を各工程に明確に「伝

えること」と、仕様ア二メーションにより「動かすこと」を目的にした記述が混在することになり、課題があることが知られている. Hayes と Jones は、1990 年に発表した「Specifications are not (necessarily) executable」[HJ89] の中で次の 2 つの課題を述べた.

- 仕様は、「解決すべき問題」 What を規定したものである。実行可能仕様により、 「問題の解決方法」 How を多く含んだ記述となり、概して要求されていることより も多くのことを規定することになる。それにより、実装の選択肢を狭めてしまう。

- どのように結果を計算するかというアルゴリズムに関する詳細な記述により、複雑な記述になる傾向がある.

Hayes と Jones はこれらの課題を解決するために、次のような提案をした。実行可能仕様は、形式仕様記述手法ではなく、ラピッドプロトタイピングとして分類した方がよく、「動かすこと」を目的としたプロトタイプとしての用途と、「伝えること」を目的とした用途は分けるべきだと主張した。また、Hayes と Jones は、仕様を動かすことは考えずに、開発対象に求められている性質(property)を記述することに集中し、仕様の検証には証明を使うべきだと述べている。

本研究では、証明ではなく、レビューやテストといった従来からある実践的な検証技術を、形式仕様記述手法と組み合わせて用いた。テストの検証技術を用いて、実行可能仕様を仕様アニメーションにより検証した。Hayes と Jones が指摘した、「動かすこと」を目的とした記述と「伝えること」を目的とした記述が混在する問題について、2 つの記述を分離する手法を提案する。詳細は 4.1 節で議論する。

また、Hayes と Jones は、簡潔性と正確性の側面に着目し、How を表現した記述が What の記述に与える影響について述べた。本研究では、Hayes と Jones が指摘したこの側面に加え、開発工程全体で形式仕様を活用するために必要な、レビューの用途を考慮した仕様記述を研究課題とした。ドメインエンジニアや仕様策定者、設計者、実装者、評価者といった様々な役割を担った読者が、形式仕様記述をレビューに用いる点に着目した。2.2.2 節において、理解容易性に関して優れた仕様記述について次のように考察した。

• 概要と詳細を階層化して明確に区別して記述してあり、概要のみを読むことで、仕

様の全体像を理解することができる仕様記述.

- 概要から詳細へと即座にたどることができる仕様記述.

- 形式仕様記述手法の専門家ではない開発者であっても, 仕様を読み進めることができるように, 特に概要の記述は簡潔な構造を持つ仕様記述.

本研究では、この課題を解決する形式仕様記述の設計・構成法を提案する. 詳細は、5.1 節において議論する.

#### 3.3 仕様と設計の分離に関する「実装の影響」の研究

2章において、本研究において扱う課題について考察した。本節では、これらの課題の うち、2.1.2 節において述べた、仕様と設計の分離に関する関連研究について述べる。こ の関連研究から本研究において提案する手法を考察する。

Michael Jackson は 1995 年に発表した「Software Requirements & Specifications」の「実装の影響」という章において、仕様と設計の分離について考察をしている [Jac95]. また、Pamela Zave と Jackson が 1997 年に発表した「Four dark corners of requirements engineering」の中でも同様に仕様と設計の分離について述べている [ZJ97]. 仕様は「実装の影響」を受けるべきではないという理由は、3.2 節と同様に What と How を分けることで、いかに作るかということに惑わされることなく、何を作るのかに集中することができるためである。その結果、仕様を簡潔に記述し、設計者に設計の自由度を持たせることができる。

以下では、「Software Requirements & Specifications」を基に、まず Jackson が示した要求と仕様、プログラムを区別する考え方と、適用領域の考え方について述べる。次に、これらの概念を使って Jackson が述べた「実装の影響」について考察する。最後に、Jackson の主張する方法と、本研究において提案する手法とを比較する。

図3.1 要求と仕様とプログラム

Jackson 「Software Requirements & Specifications」 [Jac95] より引用

#### 3.3.1 「要求と仕様とプログラム」と「適用領域」

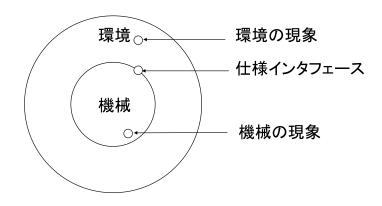

Jackson は次のような要求と仕様とプログラムを区別する考え方を示した. 図3.1 に Jackson が用いた図を引用する. この図が表していることは,要求はシステムの外にある 環境の現象について述べたものであり,機械と表記しているプログラムはシステム内の 現象について述べたものであり,仕様はシステムの内と外の境界上にある現象について 述べたものであることということである. Jackson はシステムの内側のことを機械と呼び,環境と機械の境界上を仕様インタフェース呼んでいる. つまり,環境と機械の間で共有された事象や状態からなるインタフェースを仕様と定義した.

さらに Jackson は,要求や仕様をより正確に議論する上で,環境という言葉の代わりに適用領域という用語を用いている. その理由を次のように述べている [Jac95].

環境という言葉の代わりに適用領域という用語を使うのには理由がある. 少なくとも私にとって、環境という言葉は機械を取り巻く単なる物理的な世界をイメージさせる. これに対して適用領域には実際には手にふれることのできないさまざまな対象 (図形描画のためのイメージや、給与支払システムのための表や合意事項そして従業員規定、ワードプロセッサのためのフォント、航空管制システムのための安全航行規定、コンパイラのための原始コード) などが含まれる. こういったものは機械を取り巻いていないし、逆に機械の中

に取り込まれていると考えたほうがよい場合が多い.

#### 3.3.2 「実装の影響」

Jackson は、要求・仕様・プログラムを区別する考え方と適用領域の考え方から「実装の影響」について次のように考察している.

仕様は、機械の外的な振る舞い、すなわち連続した外部操作に対する反応を記述したものである。図書館の管理システムにおける外部操作の例として StartNewLibrary や AcquireBook (b), LendBook (b), RetrunBook (b) などがある。外部操作に対する反応を記述するためには、図書館の管理システムはどの本が貸出中であり、どの本が図書館のなかに残っているのかを知っていなければならない。内部状態として、本のレコードを配列を用いて管理するのか、ハッシュを用いて管理するのかを考えなければならない。Jackson は、機械の内部状態を用いて外部操作を規定している限りは、仕様は「実装の影響」を受けると主張する。Jaskson はその理由を「システムが何かを覚えておくという考えかたそのものが、実装固有の考えだからである」と述べている。

仕様が「実装の影響」を受けないために、Jackson は次の提案をした。その提案は、「もし仕様のなかでなんらかの状態を記述しなければならないとすると、それは、機械の状態ではなく、すべて [適用領域] の状態でなければならない。」[Jac95] というものである。Jackson が用いた具体例を次に示す [Jac95].

例えば PublishedOn (b,d) が、本 b が日付 d に出版されたときに観察される 現象だとしよう。そして EalierDate (d,e) が日付 d が日付 e よりも早いこと を表す領域の現象であるとする。このとき本 b が本 e より順序が早いという ことを表す EalierInBookSequence (b,c) は、次のように観察可能な領域の現象だけを用いて定義すれば実装の影響をのがれることができる。

$EalierInBookSequence(b, c) \triangleq$

$\exists d, e \bullet PublishedOn(b, d) \land PublishedOn(c, e) \land EalierDate(d, e)$

#### 3.3.3 本提案手法との比較

確かに、Jackson の提案する方法を用いることで、「実装の影響」を回避することができる。しかし、本研究では、仕様策定工程において、機械の内部状態のデータ構造をある程度、限定することができる場合を前提とし、開発効率の観点から Jackson の提案する手法とは別の方法を提案する。その理由を以下において論じる。

Jackson が述べた適用領域の現象のみを用いて仕様を記述することで、機械の内部状態を考慮する必要はなくなるが、何らかのデータ構造を定義する必要がある。例えば、前述の図書館の管理システムにおいて、lendOut (lib, b, d) が、図書館 lib から本 b が日付 d に貸し出されたときに観測される現象だとする。lendOut 関数は、前述の PublishedOn 関数と同様に TRUE または FALSE を戻り値とする。TRUE を返す場合は、図書館 lib の本 b の貸出日と日付 d が一致する場合であり、一致しない場合は FALSE を返す。この関数の仕様を記述するためには、図書館 lib の本 d の貸出日を管理するデータ構造が必要となる。つまり、仕様策定者は、仕様を記述するために、適用領域の現象から見た上記の貸出日を管理するようなデータ構造を定義する必要がある。Jackson の主張は、仕様策定工程で定義した適用領域のデータ構造は、機械のデータ構造ではないから、「実装の影響」を受けないということである。そのため、適用領域から見たデータ構造の定義と、機械の内部状態に関するデータ構造の定義の間に、関連を持たせることは難しい。

仕様策定工程において、機械の内部状態のデータ構造をある程度は限定できる場合、仕様策定と設計と実装とテストの開発効率から Jackson の主張を考察する. 設計者は、まず、仕様を読むために、適用領域の現象から見たデータ構造を理解し、設計を行う中で機械の内部状態に関するデータ構造を新たに定義していく. 実装者や評価者は、仕様書と設計書を参照するため、適用領域の現象から見たデータ構造と、機械の内部状態に関するデータ構造の2つのデータ構造を理解する必要がある. Jackson の主張から、両者のデータ構造に関連があることを期待することは難しい. 仕様策定、設計、実装、テストにおける開発効率は、関連性のない2つのデータ構造を定義するよりは、両者の間の関連性を許容した方が向上する. なぜなら、仕様策定工程において定義したデータ構造を、設計工程においても流用することができるからである. これにより、設計者が新たにデータ構造を

検討して設計書に記述する工数や,設計者や実装者や評価者が2つのデータ構造を理解するために必要な工数を削減することができる。また,データ構造を流用することで,仕様に基づいたテストと設計に基づいたテストの観点が近くなる。したがって,仕様に基づいたテストによって,設計に基づいたテストの一部を省略できる可能性がある。これにより,設計に基づいたテストに費やす工数を削減することができる。

本研究では、仕様策定工程において、機械の内部状態のデータ構造をある程度、限定することができる場合を前提とし、仕様で定義するデータ構造と、設計で定義するデータ構造の間に関連性を許容した。この上で、「実装の影響」を回避する方法を提案する。提案手法の概要を次に述べる。まず、データ構造を定義するための型を、仕様において規定する型と、仕様においては規定しない型に分類する。次に、仕様において規定しない型の定義・演算子を、関数を定義することにより隠蔽する。つまり、仕様において規定する型と、仕様において規定しない型を明確に区別することで、「実装の影響」を回避する。仕様において規定しない型を隠蔽することで、仕様書の読み手には、仕様において規定する型のみを提示することができる。Jacksonが述べた、適用領域に関するデータ構造と、機械の内部データ構造とが同じ場合は、仕様において規定する型となり、異なる場合は、仕様において規定しない型となる傾向がある。これらの型の分類は、仕様策定者と設計者が協議をすることにより行った。

型の隠蔽は、ソフトウェア開発で用いられている情報隠蔽 [Par72, Par79, PCW85] の技術であるので、現在は「当然の技術」としてソフトウェア開発において用いられている。本論文で提案する手法は、Jackson と Zave が述べた「実装の影響」に関する考え方と、開発現場において「当然の技術」として用いられている情報隠蔽の考え方を組み合わせたものである。これにより、実際の開発現場において浸透しやすい形式仕様記述の設計・構成法に関する提案であると考える。具体的な設計・構成法は 4.2 節で述べる。

### 第4章

## 仕様と設計を分離する実行可能仕様の設 計・構成法の提案

本章では、2章と3章において述べた研究課題のうち、2つの課題に対する解決方法を提案し、提案方法の評価を行う.1つ目の課題は、「伝えること」と「動かすこと」を目的とした実行可能仕様の課題である.この課題は、2.1.1節において考察し、3.2節においてHayes と Jones の指摘する「実行可能性の影響」の関連研究から議論した.2つ目の課題は、仕様と設計の分離に関する課題である.この課題は、2.1.2節において考察し、3.3節においてJacksonの「実装の影響」の関連研究から議論した.

以降の各節では、まず、それぞれの課題を解決する方法を提案し、次に、提案手法を用いた具体例を示すことで、それぞれの解決方法を評価する。最後に、FeliCa IC チップ開発へ本提案手法を適用した結果を考察する。

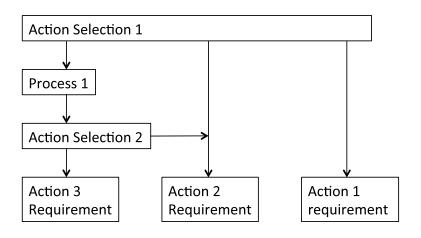

1つ目の「実行可能性の影響」に関する課題について、この課題を解決する仕様記述スタイルを提案する。まず、この課題をより具体的に議論するために、操作的な記述と宣言的な記述の観点と、仕様アニメーションによる動作検証の作業工数という2つの観点を加えて議論を進める。そして、これらの課題を解決する仕様記述スタイルを提案する。

2 つ目の仕様と設計の分離に関する課題について、仕様において定義するデータ構造と設計において定義するデータ構造に着目し、この課題を解決する形式仕様記述の設計・

図4.1 提案する形式仕様記述の設計・構成法の概略図

#### 構成法を提案する.

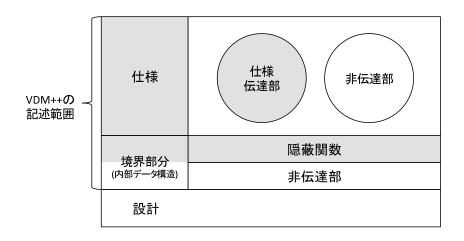

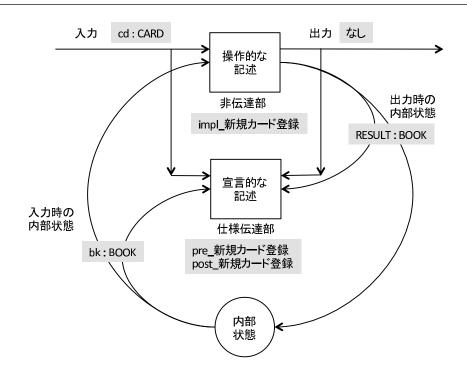

本章において提案する形式仕様記述の設計・構成法の概略図を**図 4.1** に図示する. 仕様と設計の記述を次の 3 層に分けた. 上から, 仕様の記述, 内部データ構造に着目した仕様と設計の境界部分の記述, 設計の記述である. VDM++ の記述範囲は, 設計より上の層になる. VDM++ の記述範囲に対して, 「伝えること」を目的とした記述範囲をグレーで塗りつぶした. VDM++ の記述範囲に対して, グレーで塗りつぶしていない範囲は「動かすこと」を目的とした記述範囲となる.

本章で扱う1つ目の課題である「実行可能性の影響」に関する課題を解決するために、図4.1に示した設計より上の層をさらに、仕様伝達部と非伝達部に分けた. 仕様伝達部と非伝達部については、4.1.2 節において後述する. 本章で扱う2つ目の課題である仕様と設計の分離に関する課題を解決するために、隠蔽関数により設計上の内部データ構造を隠蔽した. 隠蔽関数については、4.2 節において述べる.

まず、次節において1つ目の課題である「実行可能性の影響」を解決する仕様記述スタイルについて議論する.

# 4.1 「実行可能性の影響」を解決する仕様記述スタイルの提案と考察

2.1.1 節において、「伝えること」と「動かすこと」を目的とした実行可能仕様の課題について考察した。この課題は、次のようなものであった。従来からある既に開発現場に浸透しているテスト手法を用いて、仕様を検証するには、実行可能仕様を記述して、仕様アニメーションにより動作検証を行う必要があった。一方で、理解容易性に優れた仕様を記述するためには、「解決すべき問題」である What を仕様の読み手に明確に伝える必要があった。ここでの課題は、「動かすこと」を目的とした「問題の解決方法」であるHowを含んだ記述が、「伝えること」を目的とした仕様記述の理解容易性に影響を与えるということであった。結果、「問題の解決方法」であるHow の要素を含んだ記述が、設計者を過剰に制約し、実装の選択肢を狭めてしまう場合や、仕様の記述が複雑になる場合がある。これが「実行可能性の影響」に関する課題であった。

本研究では、この課題を解決する仕様記述スタイルを提案する. 提案の記述スタイルを用いることにより、宣言的な記述を用いて「解決すべき問題」である What を記述することができるようになる. さらに、この What の記述と、実行可能仕様として「動かすこと」を目的とした How の記述を明確に分離することができるようになるため、How の記述が What の記述の理解容易性を妨げることを避けることができる. その結果、What を記述した読みやすい仕様と、従来からあるテスト手法を用いて検証することができる 仕様を記述することができるようになる.

本節では、まず、「実行可能性の影響」について、操作的な記述と宣言的な記述という 観点と、仕様アニメーションによる動作検証の作業工数という観点を加えて、より具体的 に課題を考察する. 次に、これらの課題を解決する仕様記述スタイルを提案する. 最後に、 VDM++ を用いて提案の仕様記述スタイルを記述する場合の設計・構成法について議論 する.

図4.2 模式的に表した操作的な記述

#### 4.1.1 操作的な記述と宣言的な記述から見た実行可能仕様の課題

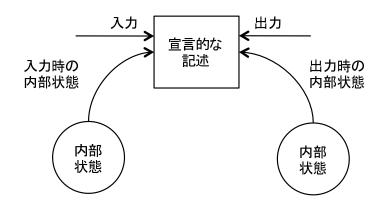

本節では、操作的な記述と宣言的な記述という側面から、「実行可能性の影響」の課題をより具体的に考察する。本論文では、操作的な記述と宣言的な記述を次のように定義することとする。図4.2 において操作的な記述を、図4.3 において宣言的な記述を模式的に表した。操作的な記述とは「入力」と「入力時の内部状態」を使用して、「出力」と「出力時の内部状態」を作成する過程を記述したものとする。一方、宣言的な記述とは「入力」と「入力時の内部状態」,「出力」と「出力時の内部状態」を使用して、入出力の関係を記述したものとする。4.1.3 節においても述べるが、平方根を求める場合、操作的な記述は「入力」からニュートン法などにより「出力」を求める過程を記述する。宣言的な記述の場合、「入力」と「出力」の関係を次のように記述する。

abs (

$$res**2 - x$$

) <= EPS

ここで、「abs」は絶対値を求める関数、「res」は実数型の「出力」を表す変数、「\*\*」はべき乗の演算子、「x」は「入力」を表す実数型の変数、「<=」は左辺より右辺の方が大きいか等しいときに true となる演算子、「EPS」は許容誤差を表す実数型の定数である。この記述は、「出力」を2乗した値と「入力」との差の絶対値は、許容誤差以内であることと読むことができる。このように、宣言的な記述は「入力」と「出力」を用いて入出力の関係を記述したものとする。

図4.3 模式的に表した宣言的な記述

操作的な記述の場合,「解決すべき問題」である What よりも「問題の解決方法」である How を多く含んだ記述となり, 仕様が過剰に設計者を制約し, さらに, 記述が複雑になる傾向がある. 一方, 宣言的な記述の場合, 記述方法にもよるが, 入出力の関係を条件式を用いて記述することで,「実行可能性の影響」を回避することができる.

しかし、宣言的な記述を用いて、実行可能仕様を記述した場合、実行するために必要な評価者の作業工数が課題となる場合がある。この作業工数の課題について考察する。操作的な記述の場合、図 4.2 に示すように、「入力」と「入力時の内部状態」から、仕様アニメーションにより仕様を動かし、「出力」と「出力時の内部状態」を得ることができる。一方、宣言的な記述の場合、図 4.3 に示すように、仕様アニメーションにより動かすためには、「入力」と「入力時の内部状態」に加え、「出力」と「出力時の内部状態」が必要になる。つまり、宣言的な記述を仕様アニメーションにより動かすためには、あかかじめ「出力」と「出力時の内部状態」を作成しておく必要がある。これは、「出力」と「出力時の内部状態」を作成しておく必要がある。これは、「出力」と「出力時の内部状態」を存成しておく必要がある。これは、「出力」と「出力時の内部状態」を容易に作成することができる場合は課題とはならないが、複雑な内部状態を持つ仕様の場合、評価者の作業工数が課題となる場合が多い。

作業工数の点で考察すると、操作的な記述の場合においても、あらかじめ「出力」と「出力時の内部状態」の一部を作成しておく必要がある. 仕様アニメーションを行う場合、実行結果とあらかじめ作成しておいた期待値とを比較することで、実行結果が正しいことを確認する. そのため、この期待値としての「出力」と「出力時の内部状態」をあらかじめ作成しておく必要がある. しかし、このとき、評価者は期待値として作成する「出力

時の内部状態」を,実行結果が変化した範囲だけとするのか,変化しない範囲も含めた全てとするのかを選択することができる.この選択は,検証対象としている関数の重要度や複雑度,内部状態を作成するのに必要な作業工数など,評価者が費用対効果を考慮して決めることができる.一方,宣言的な記述の場合,常に全ての「出力」と「出力時の内部状態」を作成しなければならないため,評価者の作業工数が課題となることが多い.

つまり、操作的な記述の場合は、「実行可能性の影響」を受けることが課題となり、宣言的な記述の場合、「実行可能性の影響」を回避することができるが、仕様アニメーションにより動かすときに、評価者の作業工数が課題となる。この課題を解決する仕様記述スタイルを次の 4.1.2 節において提案する.

#### 4.1.2 「実行可能性の影響」を解決する仕様記述スタイルの提案

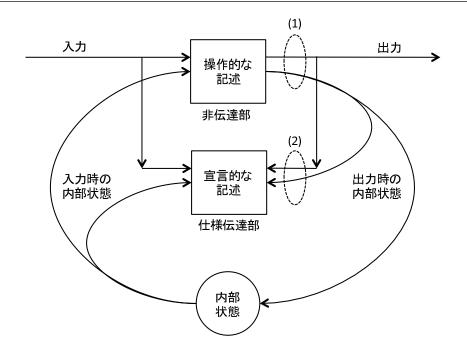

操作的な記述は、「出力」と「出力時の内部状態」を生成することができるが、「実行可能性の影響」を受ける.一方、宣言的な記述は、「実行可能性の影響」を回避することができるが、仕様アニメーションにより動かすときに、あらかじめ、「出力」と「出力時の内部状態」を生成しておく必要があるため、評価者の作業工数が課題であった.「実行可能性の影響」を回避して、さらに、評価者の作業工数の課題を解決するために、図4.4に示す仕様記述スタイルを提案する.この図は、操作的な記述を模式的に表した図4.2と、宣言的な記述を模式的に表した図4.3を組み合わせたものである.この記述スタイルは、宣言的な記述の箇所に「伝えること」を目的とした仕様記述を配置して、操作的な記述の箇所に「動かすこと」を目的とした記述を配置したものである.本論文では、図4.4の宣言的な記述箇所を仕様伝達部と呼び、操作的な記述箇所を非伝達部と呼ぶ.図4.4の操作的な記述の箇所において、「入力」と「入力時の内部状態」を使用して、「出力」と「出力時の内部状態」を作成する.図4.4中の(1)において、操作的な記述を仕様アニメーションにより動かすことで作成した「出力」と「出力時の内部状態」が出力される.この出力が、(2)において宣言的な記述への入力となっていることが分かる.つまり、「入力」と「入力時の内部状態」を操作的な記述を動かすこ

図4.4 模式的に表した「実行可能性の影響」を解決する仕様記述スタイル

とができるようになる. これにより、図 4.3 の宣言的な記述を、仕様アニメーションにより動かすときに課題であった、評価者の作業工数の課題を解決することができる.

以上により、「伝えること」と「動かすこと」を目的とした実行可能仕様の課題を解決することができる。つまり、宣言的な記述を用いて「解決すべき問題」である What を記述することができるようになる。さらに、この What の記述と実行可能仕様として「動かすこと」を目的とした How の記述を明確に分離することができるため、How の記述がWhat の記述の理解容易性を妨げることを避けることができる。また、仕様アニメーションによる仕様の動作検証における、評価者の作業工数の課題を解決することができる。

本節において定義した, 非伝達部に関して注意する点として, 操作的な記述箇所が非伝達部とはならないことがある. 例えば, 図 4.2 おいて, 操作的な記述箇所に, 仕様策定者が操作的な内容を「伝えること」を目的として記述した場合は, その記述は, 操作的な記述ではあるが, 仕様伝達部となり, 非伝達部とはならない. ただし, このとき仕様策定者は, 「問題の解決方法」である How の記述を行っていることを認識するか, あるいは, 「解決すべき問題」である What の記述を行っているのであれば, 「実行可能性の影響」を考慮しなければならない.

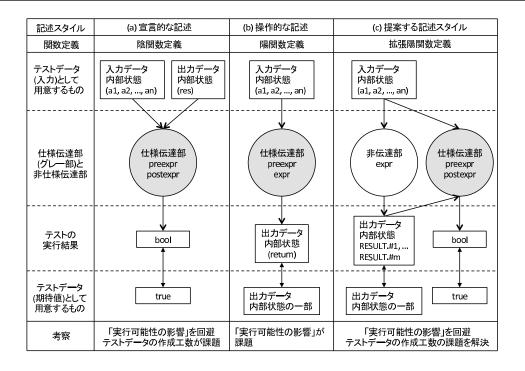

以降の各節では、図 4.2 と図 4.3 と図 4.4 に示した記述スタイルを VDM++ を用いて記 述する場合の設計・構成法ついて議論する.まず、図4.3で示した宣言的な記述に対応す る設計・構成法として、陰関数定義について考察し、次に、図4.2で示した操作的な記述 に対応する設計・構成法として、陽関数定義について考察する. 最後に、本研究において 提案する図4.4の記述スタイルに対応する設計・構成法として、拡張陽関数定義について 考察する. 図 4.5 は, これらの関数定義と記述スタイルの関係を模式的に表したものであ る. 図は, 最上段に図 4.2 と図 4.3 と図 4.4 に示した記述スタイル名を示した. 次の段に, 各記述スタイルに対応する VDM++ の言語仕様に示された関数定義名を示した. その 下に, 仕様アニメーションによる動作検証において, 評価者が入力として用意するテスト データを示した. 次に、その入力データについて、仕様伝達部と非伝達部におけるデータ の流れを示して、出力をその次の段に示した.ここでは、図4.1と同様に「伝えること」 を目的とした仕様伝達部をグレーで塗りつぶしている. そして次の段に, この出力が正し いことを確認するために、期待値として用意するテストデータを示した。最後の行に、記 述スタイルの考察をまとめた.この図を用いて、4.1.1節と本節において分析した、「実行 可能性性の影響」の課題と、実行するために必要な評価者の作業工数について、VDM++ の関数定義から議論する.

#### 4.1.3 陰関数定義に関する考察

陰関数定義を用いることで、図 4.3 に示した宣言的な記述を行うことができる. 陰関数定義は、事前条件 (pre) と事後条件 (post) から構成される. VDM++ の言語仕様として、陰関数定義の構文例を以下に示す.

```

f (a1:T1, a2:T2, ..., an:Tn) res : R

pre preexpr (a1, a2, ..., an)

post postexpr (a1, a2, ..., an, res)

```

ここで、f は関数名、T1,...,Tn はパラメータの型、a1,...,an はパラメータ名、R は戻り値の型であり、res は戻り値の識別子である。preexpr は入力の前提条件を定義した事前条

図 4.5 仕様記述スタイル

件であり、postexpr は関数 f 実行後に成立すべき条件を定義した事後条件である. 事後条件 postexpr の中で引数 a1,...,an と戻り値 res を用いて、関数実行前後の関係を記述する. 陰関数定義を用いて平方根を求める仕様記述の具体例を次に示す.

```

public sqrt (x : real) res : real

pre x >= 0

post abs (res**2 - x ) <= EPS; -- EPS は許容誤差</pre>

```

sqrt 関数は実数型 (real) のパラメータ (x) を受け取り, 実数型 (real) の結果 (res) を返す関数として定義している. 事前条件 (pre) では, 関数実行前にはパラメータ (x) が 0 以上でなければならないことを記述している. 事後条件 (post) では, 結果 (res) を二乗したものとパラメータ (x) の差の絶対値 (abs) が, 許容誤差 (EPS) 以下でなければならないことを記述している.

この仕様は VDMTools のインタープリタ機能を使用して, 仕様アニメーションにより 実行することができる. 実行をするためには, 関数名に「 pre\_」を付けて, pre\_sqrt (x) とすることで sqrt 関数の事前条件式を呼び出す. また, 関数名に「 post\_」を付けて, post\_sqrt (x,res) とすることで sqrt 関数の事後条件式を呼び出す. VDMTools のインタープリタ機能を用いて事前条件と事後条件を評価するには、以下のように行う. パラメータ (x) を 4 とし、結果 (res) を 2 とした例を次に示す.

> print pre\_sqrt(4)

true

> print post\_sqrt(4, 2)

true

「print」は実行結果の出力を指示する VDMTools のコマンドである。実行結果はbool型であり、期待値とするテストデータは true である。実行結果が期待値と異なりfalse であった場合は、入力のテストデータとして用意したパラメータ(x)の値もしくは結果 (res) の値が誤っているか、実行した pre\_sqrt、post\_sqrt の記述が誤っているかのいずれかであるため、デバッグを行って誤りを修正する必要がある。

図 4.5 (a) に, 4.1.1 節において述べた宣言的な記述に対応する模式図を示す. 宣言的な記述において, 「伝えること」を目的とした仕様伝達部は, 次に示す, 事前条件 (構文例の preexpr) と事後条件 (構文例の postexpr) である.

pre x >= 0

post abs (res\*\*2 - x ) <= EPS;

評価者が、仕様アニメーションにおいて入力のテストデータとして用意するものは、入力データであるパラメータ (x) と出力データである結果 (res) となる。図 4.5(a) の図中の preexpr と postexpr の実行結果は bool 型である。期待値とするテストデータは実行結果の true となる。

宣言的な記述を模式的に表した図 4.3 において「入力」と「入力時の内部状態」はパラメータ (x) に対応し、「出力」と「出力時の内部状態」は結果 (res) に対応する. つまり、テストデータとして「入力」と「入力時の内部状態」、「出力」と「出力時の内部状態」を用意する必要があることがこの例から分かる. そのため、4.1.1 節において述べたように、内部状態が複雑な仕様の場合、評価者の作業工数が課題となることがある.

陰関数定義を用いることで、入出力の関係を宣言的に記述することができるため、「解決すべき問題」である What を記述することができる. したがって、この宣言的な記述箇所において、操作的な記述を行わなければ、「実行可能性の影響」を回避することができる. さらに、前述の VDMTools のインタープリタ機能を用いて、仕様アニメーションにより動作検証を行うことができる. しかし、評価者は、「入力時の内部状態」と「出力時の内部状態」をあらかじめ作成しておく必要があるため、仕様アニメーションにより動かすときに、評価者の作業工数が課題となる.

#### 4.1.4 陽関数定義に関する考察

陽関数定義を用いることで、図 4.2 に示した操作的な記述を行うことができる. 陽関数定義は、事前条件 (pre) と、関数本体から構成される. VDM++ の言語仕様として、陽関数定義の構文例を以下に示す.

```

f: T1 * T2 * ... * Tn -> R1 * R2 * ... * Rm

f (a1, a2, ..., an) ==

expr

pre preexpr (a1, a2, ..., an)

```

ここで、f は関数名、T1,...,Tn はパラメータの型、R1,...,Rm は戻り値の型、a1,...,an はパラメータ名であり、expr は関数本体を表している。preexpr は入力の前提条件を定義した事前条件である。ニュートン法を用いて平方根の求め方を記述した例を次に示す。

```

public sqrt : real -> real

sqrt (x) ==

newton (x, x)

pre x >= 0;

private newton : real * real -> real

newton (x, t) ==

```

if abs (t \*\* 2 - x) <= EPS then

t

else</pre>

newton (x, (t + x/t)/2);

sqrt 関数は, 実数型 (real) のパラメータ (x) から実数型 (real) の結果を算出する. 算出方法を関数本体で記述している. 事前条件 (pre) は陰関数と同様である.

この仕様も VDMTools のインタープリタ機能を使用することで、仕様アニメーションにより実行することができる。 sqrt(x) を呼び出すことで、関数の戻り値として結果を得ることができる。 VDMTools のインタープリタ機能を用いて sqrt 関数を評価するには、以下のように行う。 許容誤差である EPS を 0.001 としてパラメータ (x) を 4 とした例を次に示す。

> print exp\_sqrt (4)

2.000000092922295

図 4.5 (b) に, 4.1.1 節において述べた操作的な記述に対応する模式図を示す. 「伝えること」を目的とした仕様伝達部は, 次の事前条件 (構文例の preexpr) である.

pre x >= 0

また, 次の関数本体 (構文例の expr) も仕様伝達部となる.

newton (x, x)

評価者が、仕様アニメーションにおいて入力のテストデータとして用意するものは、入力データであるパラメータ (x) となる。図 4.5(b) の図中の preexpr と postexpr の実行結果は、出力データとなる。

操作的な記述を模式的に表した図 4.2 において「入力」と「入力時の内部状態」はパラメータ (x) に対応し、「出力」と「出力時の内部状態」は関数の戻り値に対応する. つまり、テストデータとして「入力」と「入力時の内部状態」を用意すればよい. 「出力」

と「出力時の内部状態」のうち、期待値と比較して確認する範囲は、評価対象の関数の重 要度や複雑度、内部状態を作成する作業工数など、費用対効果を考慮して評価者が決める ことができる.

陽関数定義を用いることにより、4.1.1節において述べた、評価者の作業工数の課題を 解決することができる.しかし、図4.2の操作的な記述箇所に、「解決すべき問題」であ る What を記述しようとしたときに、入力から出力を作成する過程を記述した操作的な 記述となる. このため, 「問題の解決策」である How を含んだ記述が, 「解決すべき問 題」である What の記述の理解容易性を妨げるという、「実行可能性の影響」が課題と なる.

#### 拡張陽関数定義に関する考察 4.1.5

拡張陽関数定義を用いることで、図4.4に示した本研究において提案する記述スタイル を用いることができる. VDM++ の言語仕様として, 拡張陽関数定義の構文例を以下に 示す.

```

f : T1 * T2 * ... * Tn -> R1 * R2 * ... * Rm

f (a1, a2, ..., an) ==

expr

pre preexpr (a1, a2, ..., an)

post postexpr (a1, a2, ..., an, RESULT.#1, RESULT.#2, ..., RESULT.#m)

```

拡張陽関数定義には, 陽関数定義に陰関数の postexpr が追加され, 戻り値の識別子とし て RESULT.#1, RESULT.#2, ..., RESULT.#m を用いていることが分かる. 戻り値が 1つ の場合は、.#1 は不要である。平方根の例を用いた具体例を次に示す。

```

public sqrt : real -> real

sqrt(x) ==

newton (x, x)

pre x >= 0

```

post abs (RESULT\*\*2 - x ) <= EPS;</pre>

VDMTools のインタープリタ機能を使用することで、構文例において expr と示した関数本体と、事前条件と事後条件を実行することができる。 $\mathrm{sqrt}(x)$  を呼び出すことで、関数の戻り値として結果を得ることができる。許容誤差である EPS を 0.001 としてパラメータ (x) を 4 とした例を次に示す。

> print exp\_sqrt (4)

2.000000092922295

図 4.5 (c) に, 4.1.2 節において述べた提案の記述スタイルに対応する模式図を示す. 「伝えること」を目的とした仕様伝達部は、次に示す事前条件 (構文例の preexpr) と事後条件 (構文例の postexpr) である

pre x >= 0

post abs (res\*\*2 - x ) <= EPS;</pre>

「伝えること」ではなく「動かすこと」を目的とした非伝達部は、関数本体 (構文例の expr) となり、次の式である.

newton (x, x)

拡張陽関数定義が、陰関数定義や陽関数定義と異なる点は、関数本体の実行結果である戻り値が RESULT に入り、「post\_sqrt (4, RESULT)」として、事後条件を評価することができる点である。このため、評価者が、仕様アニメーションにおいて入力のテストデータとして用意するものは、陽関数と同様に入力データであるパラメータ (x) となり、陰関数の実行もできるようになる。図 4.4 に表した、本研究において提案する記述方法において「入力」と「入力時の内部状態」はパラメータ (x) に対応し、「出力」と「出力時の内部状態」はパラメータ (x) に対応し、「出力」と「出力時の内部状態」は関数の戻り値に対応する。つまり、陽関数定義と同様に、テストデータとして「入力」と「入力時の内部状態」を用意すればよく、4.1.1 節において述べた評価者の作業工数の課題を解決することができる。

拡張陽関数定義を用いることで、仕様伝達部と非伝達部を分離して、仕様伝達部において入出力の関係を宣言的に記述することができるため、「解決すべき問題」である What を記述することができる。したがって、この宣言的な記述箇所において、操作的な記述を行わなければ、「実行可能性の影響」を回避することができる。

次の4.2節では、2つ目の研究課題である、仕様と設計の分離の課題を解決する形式仕様記述の設計・構成法を提案する。その次の4.3節において、本節において述べた、記述スタイルの提案手法について、具体的な仕様記述例を用いて評価する。

#### 4.2 データ構造の隠蔽による仕様と設計の分離方法の提案

本節では、本章において扱う 2 つ目の課題である、仕様と設計の分離に関する課題を解決する形式仕様記述の設計・構成法を提案する.

2.1.2節で述べたように、仕様と設計の分離とは、「解決すべき問題」を定義した仕様と、「問題の解決方法」を定義した設計を分けて考えるということである。一般に、仕様策定工程では、何を作るべきかという「解決すべき問題」を検討し、設計工程では、「問題の解決方法」を検討することで、仕様策定者と設計者が分業して組織的に開発を行うことができると言われている。仕様と設計の分離は広く言われていることではあるが、実際に、仕様と設計を分離することは容易ではない。仕様と設計の境界が曖昧であるために、形式仕様記述から仕様として規定している範囲と、形式仕様記述には記述してはあるが、設計者が自由に規定できる範囲を、設計者が読み取ることが難しいという課題がある。

本研究では、仕様と設計の分離を行うために、開発対象の内部状態を表す内部データ構造に着目した.形式仕様記述言語には、集合や写像などの内部データ構造を抽象化するための型が用意されている.しかし、集合や写像を用いて内部データ構造を表現したとしても、型の特性から設計者に仕様と設計の責任範囲を伝えることはできない.以下に、この課題に関する具体的な例を示す.例えば、名前(NAME型)とアドレス(ADDRESS型)からなるアドレス帳(BOOK型)について考える.名前(NAME型)とアドレス(ADDRESS型)を次のように定義する.

NAME = seq of char;

ADDRESS = seq of char;

ここで、名前 (NAME 型) とアドレス (ADDRESS 型) は仕様策定者が仕様として規定している型とし、アドレス帳 (BOOK 型) の保持方法は設計者が規定すべきことと仮定する. つまり、仕様と設計が分離された仕様記述であるためには、上記の、仕様として規定している型と、設計者が規定すべき型の仮定が、仕様記述から読み取れなければならない. 実行可能仕様を記述するためには、アドレス帳 (BOOK 型) の型を決める必要がある. BOOK 型を、内部データ構造を抽象化するために用意された集合と写像の型を用いて規定した例を示す. 写像を用いた場合を BOOK1 型とし、集合を用いた場合を BOOK2 型とすると、次のような記述になる.

BOOK1= map NAME to ADDRESS;

BOOK2= set of CARD;

ここで、CARD 型はレコード型である. レコード型は複数の型をまとめて管理することができる. CARD 型の型定義を次に示す.

CARD ::

Name : NAME

Address : ADDRESS;

この型の値は、レコード型の構成子を用いて次の表に定義する。

mk\_CARD ("name", "name@a.co.jp")

このようにして、Name に "name" という文字列を保持し、Address に "name@a.co.jp" という文字列を保持した CARD 型の値を定義することができる.ここでは、CARD 型 も BOOK 型と同様に、形式仕様記述には記述してあるが、設計者が自由に決めることができる型とする.

次に, 名前とアドレスをアドレス帳 (BOOK 型) へ新規に登録する仕様を考える. 前述の BOOK1 型であっても BOOK2 型であっても, 新規に名前とアドレスを登録する仕様

を記述することができる. 事後条件は, 登録後のアドレス帳 (BOOK1 型, BOOK2 型) に指定した登録対象の名前とアドレスが存在していることとした. 事前条件として, 既に同一の名前 (NAME 型) がアドレス帳に登録されていないこととした.

写像を用いて定義した BOOK1 型を用いると次のような記述になる.

```

public 新規カード登録 1: BOOK1 * NAME * ADDRESS -> BOOK1 新規カード登録 1 (bk, name, addr) == bk munion {name |-> addr} pre name not in set dom bk post RESULT = bk munion {name |-> addr};

```

次に、CARD 型の集合を用いた BOOK2 型を用いた場合、次のような記述となる.

```

public 新規カード登録 2: BOOK2 * NAME * ADDRESS -> BOOK2 新規カード登録 2 (bk, name, addr) == bk union {mk_CARD (name, addr)} pre forall c in set bk & c.Name <> name post mk_CARD (name, addr) in set RESULT;

```

ここでは、いずれの型定義であっても、仕様が記述可能であることを示すまでにとどめておいて、詳細な VDM++ の言語仕様の説明は省略する。BOOK1 型を用いた場合も、BOOK2 型を用いた場合も、事前条件と事後条件において記述している内容は同じである。しかし、設計者はどちらの表現であっても、NAME 型と ADDRESS 型は仕様において規定する型であることを読み取ることができない。同様に、CARD 型と BOOK 型は設計者が自由に定義することが許された型であることを読み取ることができない。

この課題を解決するために、本論文では、仕様と設計の境界部分として内部データ構造に着目し、仕様として規定しない型を隠蔽することで、仕様策定者が仕様として規定する型と、仕様策定者が仕様としては規定せずに、設計者の責任範囲として規定すべき型の違いを明示する方法を提案する.型を隠蔽した場合と、隠蔽しない場合を比較し、可読性の違いを比較する.

型を隠蔽するために、以下のような型の仕様記述のルールを定めた。まず、型を2つに分類した。仕様で定義する「仕様の型」と、仕様では定義しない「隠蔽対象の型」である。「仕様の型」とは、工程が仕様策定と設計工程とに分かれる中で、仕様策定者が仕様として規定する型である。そのため、設計者はこの型の定義に従うべき型である。この型は、仕様策定者の責任範囲とする型である。一方、「隠蔽対象の型」とは、設計に自由度を持たせるために、仕様策定者が仕様策定工程では規定しない型である。この型は、設計工程で設計者の責任範囲として規定すべき型である。次に、「隠蔽対象の型」の定義・演算子を隠蔽するための関数を導入した。この関数を「隠蔽関数」と呼ぶこととする。図4.4の仕様伝達部から「隠蔽対象の型」の値を使用する場合は、必ず「隠蔽関数」を経由するルールとした。このルールにより、「隠蔽対象の型」の型の定義と型演算子を仕様伝達部から直接参照する記述を排除することができた。また、「仕様の型」と「隠蔽対象の型」を区別する型の命名ルールを定めることで、設計者をはじめとする仕様記述の読み手が「仕様の型」と「隠蔽対象の型」を区別できるようにした。4.3 節において、具体的な記述例を用いて説明し、提案手法の評価を行う。

#### 4.3 本提案手法を用いた具体的な記述例による評価

名前とメールアドレスからなるカードを管理するアドレス帳の具体例を用いて,これまで述べた2つの手法を評価する.

1つ目の評価は、4.1 節において述べた、「実行可能性の影響」の課題を解決する仕様記述スタイルの提案に関する評価である。図 4.4 において示した、提案の仕様記述スタイルを用いて、具体的な仕様記述例を示す。まず、この記述例を用いて、宣言的な記述により「実行可能性の影響」の課題を解決できることを示す。次に、仕様伝達部と非伝達部を分離することで、理解容易性に優れた仕様を記述することができることを示す。最後に、VDM++によるテストスクリプトを具体的に示す。この具体例を用いて、4.1.1 節において述べた、仕様アニメーションによる動作検証時に課題となる、評価者の作業工数の課題を具体的に示す。そして、提案する記述スタイルを用いて、この課題が解決できるこ

と示す.

2 つ目の評価は、4.2 節において述べた、仕様と設計の分離に関する課題を解決する形式仕様記述の設計・構成法の提案に関する評価である。評価において、提案の手法を用いた場合と、用いなかった場合の記述例を比較し、本提案手法の有効性を示す。

以降の本節では、具体例として、**図 4.6** に示したアドレス帳の例を用いる.この記述例の詳細は、各節の中で述べる.

## 4.3.1 「実行可能性の影響」を解決する仕様記述スタイルの評価

まず、図 4.6 に示した具体例について、「新規カード登録」関数を例に、「実行可能性の影響」の課題を解決する仕様記述スタイルについて議論する. 「新規カード登録」関数を次に示す.

public 新規カード登録: BOOK \* CARD -> BOOK 新規カード登録(bk, cd) == impl\_新規カード登録(bk, cd) pre cd.Name not in set 名前集合(bk) post カード集合(RESULT) = カード集合(bk) union {cd};

「新規カード登録」関数は、引数としてアドレス帳を表す BOOK 型、および名前とアドレスからなる登録対象の CARD 型を受け取り、戻り値として登録後の BOOK 型を返す、「新規カード登録」関数の事前条件 (pre) は次の条件式である.

pre cd.Name not in set 名前集合 (bk)

これは、登録対象のカードが登録済みではないことを示している. 以降では、この事前条件を「pre\_新規カード登録」と表記する. 事後条件 (post) は次の条件式である.

post カード集合 (RESULT) = カード集合 (bk) union {cd};

これは、次のように読むことができる. 登録後のアドレス帳のカード集合は、登録前のアドレス帳のカード集合に、登録対象のカードを加えたものとなっていること、という条件

```

types

```

public NAME = seq of char; -- 仕様の型

public ADDRESS = seq of char; -- 仕様の型

public CARD :: -- 仕様の型

Name : NAME

Address : ADDRESS;

public BOOK = BOOK\_IMPL; -- 隠蔽対象の型 public BOOK\_IMPL = map NAME to CARD; -- 非伝達部の型

### functions

-- 拡張陽関数定義による機能仕様の記述

public 新規カード登録 : BOOK \* CARD -> BOOK

新規カード登録 (bk, cd) ==

impl\_新規カード登録 (bk, cd) -- 非伝達部 pre cd.Name not in set 名前集合 (bk) -- 仕様伝達部 post カード集合 (RESULT)

= カード集合 (bk) union {cd}; -- 仕様伝達部

-- 「隠蔽対象の型」BOOK の「隠蔽関数」

public カード集合: BOOK -> set of CARD

カード集合(bk) ==

rng bk;

public 名前集合: BOOK -> set of NAME

名前集合(bk) ==

dom bk;

-- 新規カード登録の非伝達部

private impl\_新規カード登録 : BOOK \* CARD -> BOOK impl\_新規カード登録 (bk, cd) ==

bk munion {cd.Name |-> cd}

図4.6 本研究において提案する方法を用いた仕様記述の例

図4.7 「実行可能性の影響」を解決する仕様記述スタイルと仕様記述例との対応関係

式である. 以降では、この事後条件を「post\_新規カード登録」と表記する. 「新規カード登録」関数の関数本体は次の記述である.

impl\_新規カード登録 (bk, cd)

以降では、この関数本体を「impl\_新規カード登録」と表記する.

「新規カード登録」関数は、本研究において提案した図 4.4 の記述スタイルを用いた. 提案の記述スタイルと「新規カード登録」関数との対応関係を**図 4.7** に示す. 「入力」は、「新規カード登録」関数の引数である「cd: CARD」である. 図中では、関数内の該当箇所を指し示すために「変数名:型」という表記を用いることとする. 「入力時の内部状態」も関数の引数である「bk: BOOK」となる. 非伝達部は「impl\_新規カード登録」となる. 非伝達部であることを明確にするために、implementation を表す「impl\_」を関数の先頭に付ける命名ルールとした. 仕様伝達部は、事前条件と事後条件の「pre-新規カード登録」と「post\_新規カード登録」となる. 仕様伝達部では、「出力」と「出力時の内部状態」を使用して、入出力の関係を宣言的に記述することができる. 以上から、「実行可能性の影響」を回避することができる.「実行可能性の影響」とは「解決すべき問題」である What を記述するべき仕様に、「問題の解決方法」である How の要素を多く含んだ記述が影響を及ぼし、設計者を過剰に制約し、仕様が複雑になるというものであった.宣言的な記述により、「問題の解決方法」である How の要素を含まない仕様を記述することができる.また、「動かすこと」を目的とした記述を、図 4.7 に示した非伝達部にのみ記述し、非伝達部のみから呼び出す関数には、implementation を表す「impl\_」を関数名の先頭に付ける命名ルールとした.これにより、「動かすこと」を目的にした記述と、「伝えること」を目的にした記述を区別し、理解容易性に優れた仕様を記述することができることを示した.

次に、仕様アニメーションによる動作検証時に課題となる、評価者の作業工数の課題について、図4.4において提案した記述スタイルを用いて、この課題が解決できること示す。まず、図4.3の記述スタイルの場合に、VDM++ を用いたテストスクリプトの記述から、評価者の作業工数が課題となる具体例を示す。次に、既に示した「新規カード登録」関数と図4.7に関するテストスクリプトの記述から、この課題が解決できることを示す。

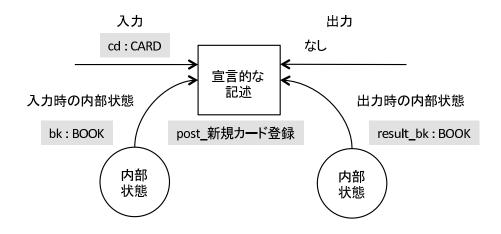

評価者の作業工数が課題となるケースは、図 4.3 に示した宣言的な記述を行った場合であった.この宣言的な記述スタイルは、前述の「新規カード登録」関数の事後条件「post」新規カード登録」の記述に対応している. 対応関係を**図 4.8** に示す. 4.1.3 節において述べたように、関数の事後条件は VDMTools のインタープリタ機能を使用して、次のように呼び出すことができる.

post\_新規カード登録 (bk, cd, result\_bk)

ここで、bk は実行前のアドレス帳を表す BOOK 型、cd は登録対象のカードを表す CARD型、result\_bk は「新規カード登録」関数の戻り値の BOOK 型である.この「 post\_新規カード登録」関数に対するテストスクリプトの記述から、評価者の作業工数が課題となる具体例を示す.

VDM++ を用いて記述したテストスクリプトを示す. まず, 「post\_新規カード登録」 関数のテストを行うために, テスト対象のアドレス帳である BOOK 型を作成するための

図4.8 宣言的な記述スタイルと仕様記述例との対応関係

### 関数は次のようになる.

```

public MakeAddressBook : () -> BOOK

MakeAddressBook () ==

let

a = mk\_CARD ("a", "a@a.a"),

b = mk\_CARD ("b", "b@a.a"),

c = mk_CARD ("c", "c@a.a"),

d = mk_CARD ("d", "d@a.a"),

e = mk_CARD ("e", "e@a.a"),

f = mk\_CARD ("f", "f@a.a")

in{

a.Name |-> a,

b.Name |-> b,

c.Name \mid -> c,

d.Name \mid -> d,

e.Name |-> e,

f.Name \mid -> f

};

```

MakeAddressBook 関数では、名前が a から f で、アドレスが a@a.a から f@a.a の 6 人のカードを保持したアドレス帳を作成している。次に、テストスクリプトの一部を取り出すと以下のようになる。

let

address\_book = MakeAddressBook (),

new\_card = mk\_CARD ("new\_name", "new@address.test"),

expected\_book = address\_book munion {new\_card.Name |-> new\_card}

in

post\_新規カード登録(address\_book, new\_card, expected\_book)= true; address\_book は、前述の MakeAddressBook 関数により作成されたテスト対象とするアドレス帳の値を保持し、new\_card は、新規に登録するカードの値を保持している。 expected\_book は、写像の munion (併合) 演算子を用いて、テスト実行前の address\_book に new\_card を登録した値を保持している。 let 式中で作成した変数を用いて、「 post\_新規カード登録」関数のテストを in 式中で実施している。このように、図 4.3 に示した宣言的な記述を評価するためには、新規カード登録後のアドレス帳のテストデータ (expected\_book) が必要である。このデータを作るために、「新規カード登録」関数で実施すべきことと同様の処理をテストスクリプト側で実施している。つまり、あらかじめ登録後のアドレス帳を作成しておかなければ、宣言的な記述である事後条件を評価することができない。このため、宣言的な記述は、評価者の作業工数が課題となることが多い。内部状態の構造として、BOOK 型は簡単な例であったが、内部状態が複雑な仕様において特に課題となることが多い。

次に、既に示した「新規カード登録」関数と図 4.7 に関する、テストスクリプトの記述から、この課題が解決できることを示す。

テストスクリプトの一部を取り出すと以下のようになる.

let

address\_book = MakeAddressBook (),

```

new_card = mk_CARD ("new_name", "new@address.test"),

actual_result_book = 新規カード登録 (address_book, new_card)

in

actual_result_book (new_card.Name) = new_card;

```

let 式中の address\_book と new\_card は前述の例と同様である. actual\_result\_book にはテスト対象の「新規カード登録」関数を実行した結果のアドレス帳の値が入る. in 式内では,次のように実行結果と期待値を比較している. 「新規カード登録」関数の実行結果を格納した actual\_result\_book から,登録時に指定した名前 (new\_card.Name) をキーにしてカードを取得している. そして,取得したカードと期待値である new\_card が一致することを確認している. 期待値の確認範囲として,変化した範囲のみを確認する場合は,期待値として作成するテスト用のデータは new\_card のみでよい. 一方,全ての変化しない範囲も含めて確認する場合は,次に示すように,期待値 (expected\_book) を作成し, in 式内で実行結果 (actual\_result\_book) と期待値 (expected\_book) の比較を行うことができる.

let

```

address_book = MakeAddressBook (),

new_card = mk_CARD ("new_name", "new@address.test"),

actual_result_book = 新規カード登録 (address_book, new_card)

expected_book = address_book munion {new_card.Name |-> new_card}

in

actual_result_book = expected_book;

```

ここで示した expected\_book は, 前述の宣言的な記述のテストスクリプトにおいて示した方法と同様である. 図 4.3 の記述スタイルを用いた宣言的な記述スタイルの場合は, 常に新規カード登録後の実行結果であるアドレス帳のデータ (expected\_book) が必要であった.

このように、提案の記述スタイルを用いた場合は、期待値として作成する実行結果について、変化した範囲だけとするべきか、変化しない範囲も含めた全てとするべきかを評価者が選択することができる。この選択は、検証対象としている関数の重要度や複雑度、内部状態を作成する作業工数など、評価者が費用対効果を考慮して決めることができる。一方、図 4.3 に示した宣言的な記述の場合は、常に変化しない範囲も含めた全ての実行結果の期待値が必要となり、評価者が費用対効果を考慮して決めることができない点において課題となる。

簡単な記述例ではあるが、図4.4において提案した記述スタイルを拡張陽関数定義に適用した具体例を示した。まず、具体例の中で、事前条件と事後条件を仕様伝達部として、宣言的な記述を行うことで「実行可能性の影響」を回避した。また、「impl\_」のような命名ルールを定めることで、仕様伝達部と非伝達部を明確に分離できることを示した。次に、仕様アニメーションによる動作検証時に課題となる、評価者の作業工数の課題を、テストスクリプトから具体的に示した。これにより、提案した記述スタイルを用いることで、評価者の作業工数の課題が解決できることを示した。

### 4.3.2 仕様と設計の分離に関する課題を解決する形式仕様記述の評価

本節において、4.2節で述べた、仕様と設計の分離に関する課題を解決する仕様記述の 設計・構成法を評価する.評価において、提案の手法を用いた場合と、用いなかった場合 の記述例を比較し、本提案手法の有効性を示す.

図4.6のアドレス帳の仕様記述例において、次の5つの型を定義した.

```

public NAME = seq of char;

public ADDRESS = seq of char;

public CARD ::

Name : NAME

Address : ADDRESS;

public BOOK = BOOK_IMPL;

```

public BOOK\_IMPL = map NAME to CARD;

まず、仕様記述に用いる型を「仕様の型」と「隠蔽対象の型」とに分類する. ここでは、NAME型、ADDRESS型、CARD型を仕様において規定する「仕様の型」とした. BOOK型を仕様では規定しない内部データ構造を表す「隠蔽対象の型」と仮定する. BOOK型をBOOK\_IMPL型として再定義する型の定義ルールによって、BOOK型は「隠蔽対象の型」であることを明示した. 「IMPL」を型名の後ろに付けることで、再定義したBOOK型は「隠蔽対象の型」であることを示した. これにより、形式仕様には記述してあるが、設計に自由度を持たせるために仕様策定者が仕様策定工程では規定しない型であるため、設計工程で設計者の責任範囲として規定すべき型であることを示すことができた.

次に、「隠蔽対象の型」を「隠蔽関数」を定義することにより、型の定義、演算子を隠蔽する。BOOK 型を隠蔽する「隠蔽関数」を次に示す。

public カード集合: BOOK -> set of CARD カード集合(bk) ==

rng bk;

public 名前集合 : BOOK -> set of NAME

名前集合(bk)==

dom bk;

このように、「カード集合」「名前集合」といった BOOK 型を操作する「隠蔽関数」を用意した. 仕様伝達部では「隠蔽関数」を用いて BOOK 型の値を使用することで、BOOK 型の型定義と型演算子を隠蔽した. このため、形式仕様の読者が仕様伝達部を読んでいる限りは、「隠蔽対象の型」の型定義、型演算子を参照することはない.

最後に、仕様の理解容易性を評価する.以下に、型の隠蔽を行わない記述と、型の隠蔽を行った記述例を示す.

-- 型の隠蔽を行わない記述

public 新規カード登録 : BOOK \* CARD -> BOOK

新規カード登録 (bk, cd) ==

impl\_新規カード登録 (bk, cd)

pre cd.Name not in set dom bk

post rng RESULT = rng bk union {cd};

-- 型の隠蔽を行った記述

public 新規カード登録 : BOOK \* CARD -> BOOK

新規カード登録 (bk, cd) ==

impl\_新規カード登録 (bk, cd)

pre cd.Name not in set 名前集合 (bk)

post カード集合 (RESULT) = カード集合 (bk) union {cd};

型の隠蔽を行わない記述では、事前条件 (pre) と事後条件 (post) の仕様伝達部において、写像の型演算子を用いて仕様を記述した.この型の隠蔽を行わない記述と、行った記述を比較することで、内部データ構造の隠蔽が、仕様と設計の規定範囲の観点で理解容易性を向上させる効果があることが分かる.また、3.3 節において述べた「実装の影響」の観点で考察する.型を隠蔽する隠蔽関数名として、「カード集合」や「名前集合」といった、Jackson が述べた機械の内部の状態ではなく、適用領域の用語を用いることができた.このため、ドメインエンジニアや仕様策定者から見ても、読みやすい仕様となっていることが分かる.

# 4.4 本提案手法の FeliCa IC チップ開発への適用の結果と 考察

4.3 節で述べた具体例は、説明のための簡単な例であるため、実際の開発現場における 有効性を示すには十分ではない. 筆者らは、本論文で提案した手法を FeliCa IC チップ開 発プロジェクトにおいて適用した. FeliCa IC チップ開発プロジェクトのうち、次に示す 2 つの製品開発プロジェクトにおいて形式仕様記述手法を適用した. 2004 年から 2007

### functions

```

public コマンド実行: PACKET_DATA * FILE_SYSTEM * STATE

-> PACKET_DATA * FILE_SYSTEM * STATE

コマンド実行 (cmnd_pkt, fs, state) ==

is subclass responsibility

pre

post

コマンド仕様 (cmnd_pkt, fs, state, RESULT.#1, RESULT.#2, RESULT.#3);

public コマンド仕様: PACKET_DATA * FILE_SYSTEM * STATE *

PACKET_DATA * FILE_SYSTEM * STATE -> bool

コマンド仕様 (cmnd_pkt, old_fs, old_state, res_pkt, new_fs, new_state) ==

is subclass responsibility;

```

### 図4.9 各コマンドの仕様を記述するテンプレートの記述例

年までフェリカネットワークス株式会社にてモバイル FeliCa IC チップ開発プロジェクトに形式仕様記述手法を用い、その後、2007年中頃から約4年間、ソニー株式会社にてFeliCa IC チップ開発に形式仕様記述手法を適用した。前者を第1世代の適用、後者を第2世代の適用と呼ぶ。本提案手法は、第1世代の適用において課題となったため、第1世代の適用が終了した後に提案手法の検討を行ったものである。そして、第2世代の適用において実際に用いた。

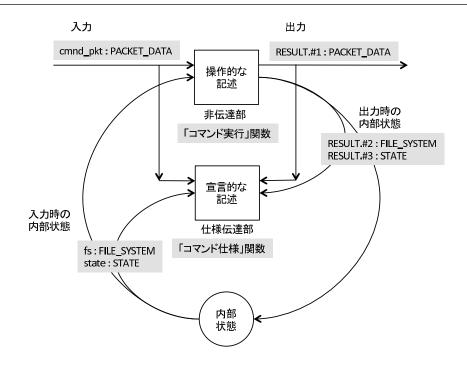

第2世代の適用において、提案手法を用いた記述例として、コマンド機能の仕様記述を示す。コマンド機能は、仕様記述全体の約7割を占め、主要な仕様記述モジュールとなっている。コマンド機能は数十のコマンド群からなり、各コマンドの仕様を記述するために、テンプレートが必要であった。この各コマンドの仕様を記述するためのテンプレートを図4.9に示す。テンプレートは、「コマンド実行」関数と「コマンド仕様」関数からなり、図4.4に示した本章において提案した記述スタイルを用いている。また、図4.5 (c) に示した拡

図4.10 提案の仕様記述スタイルと仕様記述例との対応関係

張陽関数定義を使用している. 「コマンド実行」関数の is subclass responsibility となっている箇所の内容が非伝達部である. 「コマンド仕様」関数の is subclass responsibility の箇所の内容が仕様伝達部となる. これらの is subclass responsibility の内容は, このクラスを継承した子クラスにおいて記述した.

図 4.9 のテンプレートの記述例と、図 4.4 において示した提案手法との対応関係を、図 4.10 に示す。対応関係について、図 4.9 と図 4.10 を用いて説明する。図 4.10 に示すように、「コマンド実行」関数は非伝達部となり、「コマンド仕様」関数は仕様伝達部となる。「コマンド実行」関数の引数は、FeliCa IC チップへの「入力」である PACKET\_DATA 型と、「入力時の内部状態」を定義した FILE\_SYSTEM 型と STATE 型からなる。「コマンド実行」関数の戻り値は、FeliCa IC チップの「出力」である PACKET\_DATA 型と、「出力時の内部状態」を定義した FILE\_SYSTEM 型と STATE 型からなる。「コマンド仕様」関数の引数は、「コマンド実行」関数の引数と戻り値(RESULT)とした。RESULT.#1は 1 つ目の「コマンド実行」関数の戻り値、つまり PACKET\_DATA 型の戻り値である。同様に RESULT.#2 と RESULT.#3 は 2 つ目と 3 つ目の「コマンド実行」関数の戻

り値として示した FILE\_SYSTEM 型と STATE 型である. また, FILE\_SYSTEM 型と STATE 型は, 4.2 節で述べた「隠蔽対象の型」とした.

このように、「コマンド仕様」関数と「コマンド実行」関数を用いて、仕様伝達部と非伝達部を分離し、仕様伝達部において、入出力の関係を宣言的に記述することができた。宣言的な記述により、「解決すべき問題」である What を記述することができ、「実行可能性の影響」を回避することができた。さらに、仕様アニメーションにより動作検証を行う場合、非伝達部において「出力」と「出力時の内部状態」を作成することで、評価者の作業工数の課題を解決することができた。FILE\_SYSTEM 型と STATE 型を「隠蔽対象の型」として、隠蔽関数を用い、設計において定義するデータ構造を隠蔽した。これにより、仕様において定義する「仕様の型」と区別し、仕様と設計を分離することができた。

表 4.1 に、VDM++ で記述したソースコードの有効行数をモジュール単位で示す.ここでいう有効行数とは、総行数からコメント行と空行を除いた行数である.コマンド機能は、記述例として示したテンプレートの中身を記述したものである.これは、全体の約7割を占める主要なモジュールである.ファイルシステム機能と状態管理機能は、内部データ構造を含む機能仕様である.フレームワークとは仕様を記述する枠組みを提供し、図4.9 に示したコマンド仕様を記述するテンプレートもフレームワークの一部である.汎用ライブラリは、ビット演算などの汎用的なライブラリである.

フレームワークと汎用ライブラリを除く全ての機能仕様は,図4.5(c)の拡張陽関数定義を用い,図4.4に示した本研究において提案した記述スタイルを用いた.フレームワークと汎用ライブラリは,図4.5(b)の陽関数定義を用い,図4.7に示した操作的な記述スタイルを用いた.

図4.4 に示した本研究において提案した記述スタイルの課題は, 宣言的な記述と操作的な記述という2つの記述が必要な点である. 例えば, 図4.7 に示した「新規カード登録」の例を用いて説明する. 操作的な記述箇所である「impl\_新規カード登録」では, アドレス帳にカードを「登録する」というアドレス帳への操作を記述し, 宣言的な記述箇所である「post\_新規カード登録」では, アドレス帳にカードが「存在する」という条件を記述している. これは, 仕様を代入として記述するか, 条件式として記述するかの違いであ

| モジュール名     | 有効行数   |

|------------|--------|

| コマンド機能     | 11,460 |

| ファイルシステム機能 | 1,716  |

| 状態管理機能     | 428    |

| セキュリティ機能   | 1,120  |

| フレームワーク    | 425    |

| 汎用ライブラリ    | 648    |

| 合計         | 15,797 |

表 4.1 適用対象の規模 (有効行数)

る. 仕様記述の観点では、この違いの重要性を考慮する必要がある. なぜなら、この違いが仕様と設計の違いであるからである. つまり、「解決すべき問題」である What の記述と、「問題の解決方法」である How の記述の違いであるからである. 一方で、実際に提案手法を適用するときにおいて、仕様記述の観点では重要な違いかもしれないが、「同じような」記述を 2 箇所において記述する必要があるため、作業効率の観点から課題となった. 図 4.2 の操作的な記述と、図 4.3 の宣言的な記述と、図 4.6 の提案手法の記述を比較すると、提案手法の記述量が最も多くなる. 提案手法において、操作的な記述箇所と宣言的な記述箇所について、記述の共通化を行わなかった場合、提案手法の記述量は、操作的な記述量と宣言的な記述量の総和となる. 筆者らの適用において、操作的な記述箇所と宣言的な記述箇所の共通部分を抜き出して関数化することで、記述量の増加を抑えた. 表 4.2 にコマンド機能モジュールの仕様伝達部と非伝達部の構成比を示す. 共通部が、操作的な記述箇所と宣言的な記述箇所において、共通部分を関数化した部分である. この表において示すように、67%のソースコードを共通化した.

実際に適用するときの課題として、仕様記述者が陰関数を用いて宣言的に仕様を記述するには、陰関数の記述経験が必要である点がある。拡張陽関数定義の記述スタイルであれば、陰関数と陽関数を同時に書きながらテストを行い、宣言的な仕様を完成させることができる。最初に陽関数の記述を行い、開発対象の仕様と、形式仕様記述手法に対する理

| コマンド機能モジュールの構成 | 有効行数   | 比率  |

|----------------|--------|-----|

| 共通部            | 7,680  | 67% |

| 仕様伝達部          | 1,691  | 15% |

| 非伝達部           | 2,089  | 18% |

| 合計             | 11,460 |     |

表 4.2 仕様伝達部と非伝達部の構成 (有効行数)

解を深め、その後、仕様アニメーションにより仕様を動作させることで、動作検証を行い ながら陰関数を記述することができる. 本提案手法の適用において、仕様記述の経験を積 みながら徐々に記述スタイルを改善していくことが重要である.

### 仕様と設計を分離する実行可能仕様のまとめ 4.5

本章では、2 章と3 章において述べた研究課題のうち2 つの課題に対する解決方法を 提案し、 提案方法の評価を行った. 1つ目の課題は、 「伝えること」と「動かすこと」を 目的とした実行可能仕様の課題であった.この課題は、2.1.1節において考察し、3.2節に おいて Haves と Jones の指摘する「実行可能性の影響」の関連研究から議論したもので ある. 2 つ目の課題は、仕様と設計の分離に関する課題であった. この課題は、2.1.2 節に おいて考察し、3.3 節において Jackson の「実装の影響」の関連研究から議論したもので ある.

1つ目の「実行可能性の影響」に関する課題について、この課題を解決する仕様記述ス タイルを提案した. まず、次の 2 つの観点から仕様記述スタイルを議論した. 操作的な記 述と宣言的な記述の観点と, 仕様アニメーションによる動作検証の作業工数の観点であ る. この中で, 仕様伝達部と非伝達部からなる仕様記述スタイルを提案した. 次に, 具体 的な仕様記述例を用いて、提案の仕様記述スタイルを評価し、次の3つのことを示した.

「解決すべき問題」である What を記述するために. 仕様を宣言的な記述箇所に記 述することができること.

- 仕様伝達部と非伝達部を分離することで、理解容易性に優れた仕様を記述することができること.

- 仕様アニメーションによる動作検証時に課題となる, 評価工数の課題が解決できる こと.

2 つ目の仕様と設計の分離に関する課題について、仕様において定義するデータ構造と設計において定義するデータ構造に着目し、この課題を解決する形式仕様記述の設計・構成法を提案した. 仕様策定者が決める「仕様の型」と、設計者が決める、「隠蔽対象の型」に分類し、「隠蔽対象の型」を「隠蔽関数」により隠蔽する方法を提案した. この手法の評価において、提案の手法を用いた場合と、用いなかった場合の記述例を比較し、本提案手法の有効性を示した.

最後に、提案した手法を FeliCa IC チップ開発プロジェクトにおいて適用した結果について述べ、適用における知見を考察した.

# 第5章

# レビューとテストの用途を考慮した仕様 記述フレームワークの提案

1章において、Parnas が指摘した、フォーマルメソッドがありふれた「当然の技術」として産業界に浸透していないという課題を述べた。本研究が扱うフォーマルメソッドの適用の段階は、証明などは行わないで、形式仕様記述を行うレベル 0 の段階である。このレベル 0 の段階を、レベル 0-a とレベル 0-b に分けることで、Parnas が指摘した課題を分析した。レベル 0-a は、形式仕様の記述者が、形式仕様記述手法を用いて仕様を厳密に記述し、早期に仕様の曖昧さに起因する不具合を見つけることができる適用の段階とした。レベル 0-b は、形式仕様の記述者以外である、ドメインエンジニアや設計者、実装者、評価者が、形式仕様記述を参照し、形式仕様記述に基づいて設計と実装とテストを行う適用の段階とした。形式仕様を参照する人は、レベル 0-a では形式仕様の記述者に限定されるが、レベル 0-b ではドメインエンジニア、設計者、実装者、評価者といった、ほぼ全ての工程の人となる。これらの人たちが、形式仕様記述手法をあらかじめ習得していることは少なく、形式仕様記述手法の専門家ではない人が、形式仕様記述を読み、理解し、活用していく必要がある。つまり、これらの人たちが、読みやすいと感じ、形式仕様記述手法を利用することにメリットを感じることが重要であり、そのような、形式仕様を記述するための技術と、活用するための技術が必要である。この課題を解決することで、形式仕様

記述手法がありふれた「当然の技術」として、開発プロジェクトにおいて広く活用されるようになり、さらには、産業界においても広く活用されることにつながると考える.

本研究では,前述のレベル 0-b の段階に到達するために必要な,形式仕様を記述するための技術と,活用するための技術を研究課題として設定した.記述するための技術として,ドメインエンジニア,設計者,実装者,評価者といった様々な役割を担った開発者にとって,理解容易性に優れた仕様を記述する技術が必要である.活用するための技術としては,従来からある既に開発現場に浸透しているレビューやテスト手法といった検証技術を主体として,その中で形式仕様記述手法を活用していく技術が必要である.

以上のような課題認識から、2章では、本研究において扱う次の3つの課題について述べた.

- 実行可能仕様における仕様と設計の分離に関する課題

- レビューとテストの用途として形式仕様記述を利用する場合の課題

- 形式仕様記述手法では取扱いが容易でない動的な振る舞いに関する課題

1つ目の課題の解決方法として,4章では,「実行可能性の影響」を回避する形式仕様の記述スタイルと,内部データ構造に着目した仕様と設計の分離方法を提案した.

本章では、2つ目の課題を解決するレビューとテストの用途を考慮した仕様記述フレームワークを提案する。また、実際に、形式仕様記述から体系的にテスト項目を作成し、テスト項目とテストスクリプトの網羅性を機械的に検証する方法を提案する。レビューとテストの用途として形式仕様記述を利用する場合の課題は、2.2節において考察した。

レビューにおける課題は、次のような課題であった.形式仕様記述手法の専門家ではない、ドメインエンジニア、仕様策定者、設計者、実装者、評価者といった、様々な読者が形式仕様をレビューに用いる場合を考える.この時、レビューの目的によって、読者が必要とする仕様の詳細度が異なる.例えば、ドメインエンジニアが、仕様が要求を満たしていることを確認するレビューと、実装者が、実装コードが仕様を満たしていることを確認するレビューとでは、必要となる仕様の詳細度は異なる.ドメインエンジニアが必要とする仕様の詳細度に比べ、設計者と実装者と評価者はより詳細度の細かい仕様を必要とする

ことが多い. このような仕様の詳細度の分析から, 様々なレビューの目的を持った読者にとって. 読みやすい仕様書を次のように考えた.

- 概要と詳細を階層化して明確に区別して記述してあり、概要のみを読むことで、仕 様の全体像を理解することができる仕様記述.

- 概要から詳細へと即座にたどることができる仕様記述.

- 形式仕様記述手法の専門家ではない人であっても、仕様を読み進めることができるように、特に概要の記述は簡潔な構造を持つ仕様記述.

このような仕様であれば、ドメインエンジニアが仕様をレビューする場合は、まず概要を 読み進め、必要に応じて概要から詳細を読むことができる。設計者と実装者と評価者は、 概要を把握した上で、概要と詳細を往き来しながら仕様を読み進めることができる。本章 では、以上のような課題を解決する仕様記述フレームワークを提案する。

仕様に基づくテストにおける課題は、次のような課題であった. 仕様に基づくテストとは、実装のコードが仕様を満たしていることを確認するテストのことであった. 仕様に基づくテストの工程において、形式仕様記述手法を活用することで、メリットを感じることができるように、本研究では次の 2 つの課題を設定した.

- まず、仕様に基づくテストにおいて前提とする品質目標を決める. その上で、品質目標を満たす体系的なテスト項目の作成方法を研究課題とした. これは、体系的にテスト項目を作成することができるような、形式仕様記述の設計を行わなければならないことでもある.

- テスト項目とテストスクリプトが品質目標を満たしていることを,形式仕様記述を 用いた機械的な処理により確認する方法を研究課題とした.

以上の課題設定から、本研究において定めた仕様に基づくテストの品質目標と、体系的に テスト項目を作成するためのテスト設計および、そのための仕様記述フレームワークを 提案する. そして、テスト項目とテストスクリプトが、品質目標を満たしていることを確 認するために、ログ出力による機械的な検証方法を提案する. 5.1 節では、まず、レビューとテストの用途を考慮した仕様記述フレームワークを提案する. ここでは、ディシジョンテーブルとラベル付き条件がフレームワークの中心的な概念となる. これらの概念については、5.1 節において述べる. 次に、レビューの用途から、仕様記述フレームワークの理解容易性を考察することにより、前述のレビューにおける課題への解決方法を示す. 5.2 節では、5.1 節において述べた仕様記述フレームワークを、仕様に基づくテストに活用する方法を提案することにより、前述のテストにおける課題への解決方法を示す.

まず、次節において、本章において提案する仕様記述フレームワークについて述べる.

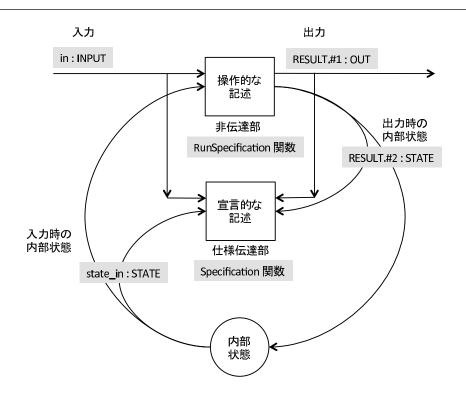

# 5.1 ラベル付き条件による仕様記述フレームワークの提案

本章において提案する仕様記述フレームワークは、4.1節において述べた宣言的な記述 を行うためのフレームワークである.つまり, 図 4.3 または, 図 4.4 に示した模式的な図 において、宣言的な記述と示した箇所に提案のフレームワークを用いることができる. 本 章では、図 4.4 の記述スタイルを用いて説明する. この記述スタイルを、VDM++ を用 いて記述した例を  $\mathbf{図 5.1}$  に示す. この例は、 $\mathbf{図 4.9}$  に示した、コマンド仕様を記述する ためのテンプレートの例を簡略化したものである.この VDM++ の記述例を用いて仕 様記述フレームワークを説明していく. この VDM++ の記述例と, 図 4.4 の対応関係を 図 5.2 に示す. 図 5.1 に示した RunSpecification 関数は実行可能仕様の最上位の関数で あり、RunSpecification 関数を実行することで仕様の動作検証を行う. RunSpecification 関数の関数本体に記述した「 is not yet specified 」は, 図 5.2 に示す操作的な記述箇所に 対応するため非伝達部となる. Specification 関数の内容は, 図 5.2 の宣言的な記述箇所に 対応するため仕様伝達部となる. 4.1.2節で述べたように、非伝達部と仕様伝達部は、「実 行可能性の影響」を回避するために、「動かすこと」を目的とした記述と「伝えること」 を目的とした記述を分離するための仕組みであった.図 5.2 に示す「入力」と「入力時 の内部状態」は、図 5.1 においては、それぞれ「 in: INPUT 」と「 state\_in: STATE 」 である. ここでは、「変数名:型名」という表記を用いることとする. 「出力」と「出力時

RunSpecification : INPUT \* STATE -> OUT \* STATE

RunSpecification (in, state\_in) ==

is not yet specified

post

Specification (in, state\_in, RESULT.#1, RESULT.#2);

**図 5.1** 図 4.9 を簡略化した図 4.4 に示した提案の記述スタイルの記述例

の内部状態」は、「RESULT.#1:OUT」と「RESULT.#2:STATE」である.