# 九州大学学術情報リポジトリ Kyushu University Institutional Repository

# YMn0\_3誘電体薄膜の作成とその特性

島ノ江, 憲剛 九州大学大学院総合理工学研究科物質理工学専攻

**梶原, 保** 九州大学大学院総合理工学研究科材料開発工学専攻 | リコー (株)

三浦, 則雄 九州大学先端科学技術共同研究センター

## 山添, 曻

九州大学大学院総合理工学研究科物質理工学専攻

https://doi.org/10.15017/16558

出版情報:九州大学大学院総合理工学報告. 21 (2), pp.167-171, 1999-09. 九州大学大学院総合理工学 研究科

バージョン: 権利関係:

# YMnO<sub>3</sub> 誘電体薄膜の作製とその特性

島ノ江 憲 剛\* ・梶 原 保\*\*

三 浦 則 雄\*\*\*・山 添 曻\*

(平成11年5月28日 受理)

### Properties and Preparation of YMnO<sub>3</sub> Dielectric Thin Film

Kengo SHIMANOE\*, Tamotsu KAJIHARA\*\*, Norio MIURA\*\*\*

and Noboru YAMAZOE\*

Dielectric YMnO $_3$  thin-film was prepared by spin-coating method. The spin-coating solution contained manganese ( $\rm III$ ) acetate and yttrium ( $\rm III$ ) acetate in a mixed solvent of 2-methoxyethnol and diethaxnolamine at the volume ratio of 94.7 : 5.3. XRD analysis revealed that the obtained thin-film consisted of single-phasic and (001)-oriented perovskite YMnO $_3$ . The dielectric constant of the film was estimated to be 24 from the capacitance-voltage measurements.

### 1. 緒 言

文字、映像、音声などのメディアの発達に伴い、 そ の記録媒体 (メモリ) に対する要求も年々厳しくなっ てきている. 1995年には 1Gb の DRAM (Dynamic Random Access memory) が試作されたが、その構造 の複雑さと工程の多さなどから見ると、あといくつか の世代で限界に達すると考えられている. つまり, 現 在の形の DRAM はその電気容量 (キャパシタンス) がスケーリング則いに沿わないという原理的な構造を 有しているため、その集積化が世代ごとに困難になっ てきている.スケーリング則とは寸法等を 1/K にし たときに他の物理量の変化について一次の近似理論で 表したものであり、寸法を 1/K にするとキャパシタ ンスも 1/K になる. この DRAM の記憶キャパシタン スとしては、寸法を小さくしても数十 fF が必要であ り、そのためトレンチ構造や積層などの立体化により 面積を増やしている. これにより工程が急増し、いず れこの方法には限界が現れると云われている. これを 解決する方法として誘電率が高い Ta<sub>2</sub>O<sub>5</sub> 等の使用が 提案され、1Gb-DRAM もこれらの材料を用いて実現 された. 強誘電体を用いたメモリは、高速書き換えが 可能な不揮発性メモリで, 低電力, 低電圧, 耐放射線 等の特徴も有する.

強誘電体の分極電荷を用いて初めて半導体表面の電荷を制御したのは、Moll ら<sup>3</sup>であり、誘電体には単結晶 TGS (Trigricine Sulfate)、半導体には CdS が用い

られている.これ以後,(Ba, Sr) $TiO_3$ <sup>0</sup>, $PbTiO_3$ <sup>0</sup>,PZT(Pb(Zr, Ti) $O_3$ )<sup>0</sup>,PLZT((Pb, La)(Zr, Ti) $O_3$ )<sup>n</sup>などの高い誘電率の材料について検討がなされている.しかし,これらの材料を用いて直接 Si 半導体の上に RAM を形成する場合,誘電体材料の一部が基板である Si あるいは周囲の  $SiO_2$  と反応し,キャリアの注入が起こったり<sup>8</sup>,界面で材料の混合,界面準位やトラップが増加する<sup>9</sup>ことが多い.そのため Si 基板上に絶縁層を形成し,その上に電極で挟み込んだ誘電体を形成しなければならず,工程が複雑化する傾向にある.これまで誘電体材料を Si 基板に直接形成した例として  $BaMgF_4$  <sup>10</sup>があり,工程の簡略化に有効と考えられる.この場合,Siとの反応をいかに抑えられるかが鍵であり,新しい材料の探索が必要である.

一方、半導体基板上に誘電体薄膜を形成する方法としては、スパッタリング、化学気相成長 (CVD)、レーザーアブレーションなどの乾式法や、スピンコーティング、ディップコーテイングなどの湿式法が行われているが、一般に強誘電体薄膜の製膜法において要求される条件としては次のものが挙げられ、

- (1) 膜組成や結晶性の制御性

- (2) 電気的特性の制御性

- (3) 成長速度が速い

- (4) 製膜温度が低い

- (5) ステップカバレージ

- (6) SiのLSIプロセスとの整合性

- (7) 大規模化や量産性

乾式法スッパタリング法は(1)(3)(5)の点に,レーザーアブレーションは(5)~(7)に関して問題があるしかし,湿式法は(5)の点に関して多少工夫が必要で

<sup>\*</sup>物質理工学専攻

<sup>\*\*</sup>材料開発工学専攻修士課程(現在リコー(株))

<sup>\*\*\*</sup>先端科学技術共同研究センター

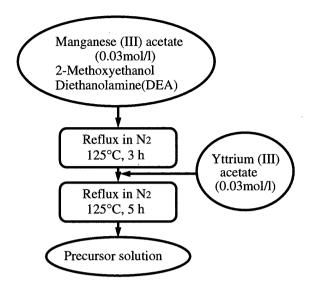

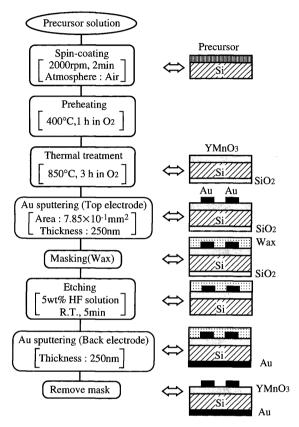

Fig. 1 Scheme of preparation for YMnO<sub>3</sub> precursor solution

あるが、その他の条件は満足しており、実用性が期待 されている.

以上のことから本研究では,工程の簡略化を考慮し,シリコンと強誘電体を直接接合させる方式について,Si との反応が起こりにくいと考えられる YMnO<sub>3</sub> を強誘電体材料として選択し,その湿式法による製膜について検討を行った.YMnO<sub>3</sub> 薄膜の作製については,これまで主に大阪府立大のグループによって,スパッタリング法<sup>111</sup>による YMnO<sub>3</sub> 薄膜粉体の作製,およびその誘電特性の評価が報告されているが,ゾルーゲル法については詳しい YMnO<sub>3</sub> 薄膜の作製条件や,誘電特性についてはまだ十分な検討がなされていない<sup>121</sup>. そこで本研究では,その調製条件等を詳しく検討するとともに,得られた YMnO<sub>3</sub> 薄膜の誘電特性の評価を行った.

#### 2. 実 験

酢酸マンガン( $\square$ )にキレート剤であるジエタノールアミン (DEA) と 2-メトキシエタノール (2ME) の混合溶媒を添加して,窒素雰囲気下,130℃で 3 時間 還流した後,この溶液に酢酸イットリウム( $\square$ )を加え,再び130℃で 5 時間 還流することにより,最終濃度 0.03Mの前駆体溶液を得た( $\mathbf{Fig.1}$ ). この溶液を単結晶  $\mathbf{P}$ 型シリコン基板 ((100),10Ω・ $\mathbf{cm}$ ) 上に滴下し, 2000rpm で 2 分間スピンコーティングした後,酸素流通下で400℃,1 時間乾燥した.この工程を $1\sim12$  回繰り返した後,最後に酸素雰囲気下で850℃,3 時間焼成し,酸化物薄膜を得た.薄膜の結晶構造はX線回折分析 (XRD) により調べた.

薄膜の誘電率については、インピーダンスアナライザー (Solartron-SI 1260, -SI 1287) を用いて、Metal/Insulator/Semiconductor (MIS) 構造の電気容量―電

Fig. 2 X-ray diffraction patterns of spin-coated film as correlated with a quantity of DEA in precursor solution.

圧 (C-V) 特性を測定することにより求めた. その際, 上部 Au 電極に直流電圧を-5~+5V 印加し, 掃引 速度20mV/s, 交流電圧周波数100kHz で行った. また, YMnO<sub>3</sub> の 膜 抵 抗 を 評 価 た め に, Metal/Insulator/ Matal (MIM) 構造を Pt を電極として作製した.

誘電体薄膜及び電極の厚さと誘電体薄膜の表面モルフォルジーは、原子間力顕微鏡(AFM, NanoScope Ⅲa)を用いて測定した.

#### 3. 結果と考察

### 3.1 酸化物薄膜の作製条件

まず、酸化物粉末の結晶構造に及ぼす前駆体溶液の溶媒混合比の影響を調べた。前駆体溶液を室温で2時間加水分解させた後、100℃で2時間乾燥させ、熱処理を850℃で3時間施して試料とし、そのXRD測定からDEAの最適添加量を決定した(Fig. 2)。これより、2ME に比べて DEA の含有量が多い混合溶液を用いた場合、 $YMn_2O_5$  と  $YMnO_3$  の混合相が見られるが、DEA の含有量が少なくなるにつれて  $YMn_2O_5$  が減少し、5.3vol%のときに  $YMnO_3$  単相が得られることがわかった。

そこで、5.3vol%DEAを含む前駆体溶液を用いて、スピンコーティング法により $20\times20$ mm²の(100)配向 p 型 Si 基板上に薄膜を形成した。その作製フロー

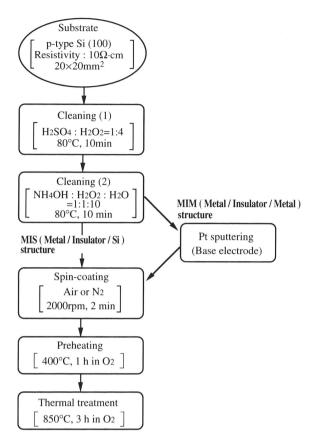

Fig. 3 Scheme of preparation for YMnO<sub>3</sub> thin film.

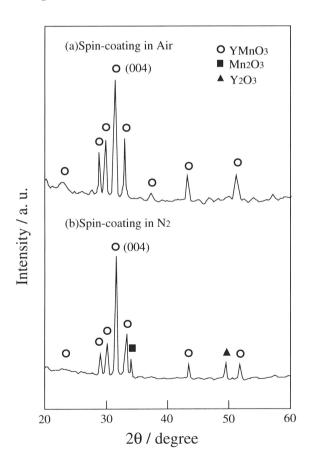

Fig. 4 X-ray diffraction patterns of film spi-ncoated in (a) air and (b)  $N_2$ .

チャートを Fig. 3 に示す. ここで、硫酸—過酸化水素水洗浄並びにアンモニア—過酸化水素水洗浄は表面の有機物およびパーティクル(微小なゴミ)の除去のためにそれぞれ行った. また、MIS 構造を作製する場合はそのままスピンコーティングを行い、MIM 構造を作製する場合は、スピンコーティングの前にスパッタリングを行った. このときスピンコーティングを大気中で行った場合には、C軸に配向したペロブスカイト構造を有する  $YMnO_3$  の単相が得られたが、窒素中でスピンコーティングしたものは、 $YMnO_3$  以外の $Y_2O_3$  や  $Mn_2O_3$  によるピークが含まれていることが明らかとなった(Fig. 4). これは、大気中でスピンコーティングを行った場合では、大気中の水分や酸素により、前駆体溶液の加水分解が均一に進行するためと考えられる.

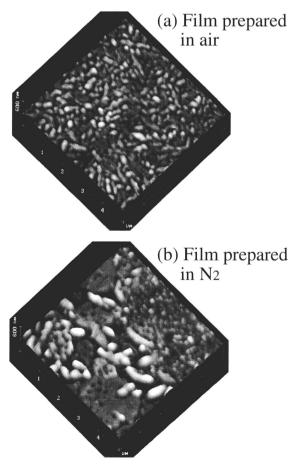

そこで、大気中および窒素中でスピンコーティングを8回繰り返した試料について AFM 観察を行った (Fig. 5). 空気中で成膜し、乾燥、熱処理した薄膜は比較的均一な組織を有しているが、窒素中で成膜後、乾燥、熱処理したものは、不均一な組織が含まれることがわかった。このことから大気中におけるスピン

Fig. 5 — AFM images of YMnO $_3$  thin film spin-coated in (a) air and (b) N $_2$  (5 $\mu$ m imes 5 $\mu$ m).

コーティングが, 薄膜作製に有効にであることが明らかとなった.

#### 3.2 誘 電 特 性

誘電率測定用の Metal/YMnO<sub>3</sub>/Si 構造の作製フロー

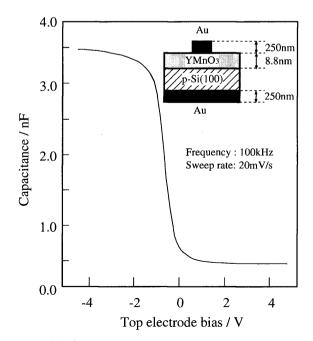

Fig. 6 Scheme of preparation for  $Au/YMnO_3$  /semiconductor structure.

Fig. 7 MIS capacitance-voltage curve for Au/YMnO<sub>3</sub>/semiconductor structure.

チャートを Fig. 6 に示す. Si 基板に前駆体溶液をスピンコーティングし、乾燥、熱処理を施した後、その形成された YMnO3 薄膜上に厚さ250nm、面積7.85× $10^{-1}$ mm²の Au 上部電極をマスクを通じて、スパッタリング法により形成した. 次に、Au 電極上を電子工業用のワックスでマスキングし、Si 基板裏面に形成された熱酸化膜を 5wt% フッ化水素酸水で除去した. その裏面には、厚さ250nm の Au 電極を、スパッタリング法により、全面に形成し、その後上部電極をマスキングしていたワックスを有機溶剤により取り除き、誘電率測定用試料とした.

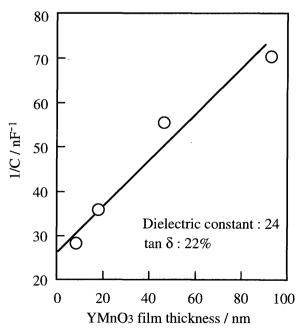

Fig. 7 には膜厚 8.8nm の酸化物薄膜の MIS 構造と C-V 特性を, また Fig. 8 には容量の膜厚依存性を示 す. 一般的に高周波容量測定では、上部電極に負電圧 を印加すると、ホールが半導体表面に蓄積して、最大 電気容量が得られるが、電圧を正方向に印加すると ホールが半導体バルクに拡散して, 空乏層が形成され るため電気容量が急激に低下する. しかし, 膜中に電 荷がある場合には C-V 曲線が+または-側に大きく シフトし, 界面反応層がある場合にはその空乏層領域 において、電荷が反応層でトラップされ、容量 C は ゆるやかに変化することが知られている. 本研究で作 製した YMnO₃ の C-V 特性は,曲線がわずかに左側 にシフトしており、膜中に正電荷を有するが、ほぼ理 想的な MIS 構造の C-V 曲線を示しており、界面反応 層はほとんど存在しないことがわかる. さらに、異な る厚さを有する薄膜の最大電気容量の逆数を膜厚に対 してプロットすると、Fig. 8 のようにほぼ直線関係が

Fig. 8 Reciprocal capacitance at 100KHz against the film thickness for Au/YMnO<sub>3</sub>/semiconductor structure.

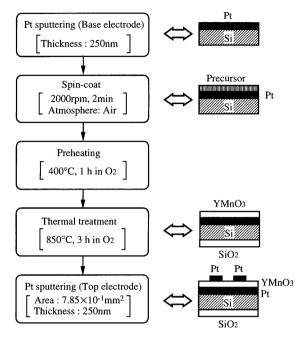

Fig. 9 Scheme of preparation for Pt/YMnO<sub>3</sub>/Pt structure.

Fig. 10 Leakage current density vs. electric field for Pt/YMnO<sub>3</sub>/Pt structure.

得られ、この直線の傾きから比誘電率を求めると、本研究の YMnO<sub>3</sub> 膜は約24の比誘電率を有することが明らかとなった。なお、この値はスパッタリング法で作製された YMnO<sub>3</sub> 薄膜や、バルク体とほぼ同じレベルの値である。しかし、この最大電気容量を示す電圧において誘電損失( $\tan\delta$ )は22%と大きく、膜そのものの電気抵抗が小さいことが伺える。そこで、誘電損失の大きい原因を調べるため、MIM 構造における YMnO<sub>3</sub> の膜抵抗を評価した。

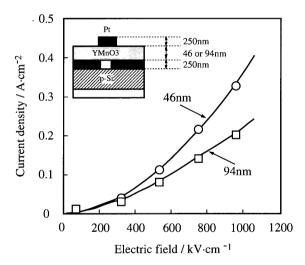

**Fig. 9** に膜抵抗測定のための  $Pt/YMnO_3/Pt$  (MIM) 構造の作製フローチャートを, **Fig. 10** には作製した素子の電流一電圧特性を示す. 電界強度が増えるに従い, 電流密度も増加し, また電界強度が300 $kV \cdot cm^{-1}$

以上から電流密度の差が大きくなることがわかった.そこで,膜厚によらず電流密度がほぼ一定である直線の傾きより,YMnO $_3$ の抵抗率をもとめたところ, $_3$ ~ $_5$  M $_2$ ·cmと,膜の電気抵抗が低いことが明らかとなった.したがって,**Fig. 8** に見られた誘電損失が高い原因は,YMnO $_3$  薄膜の電気抵抗が小さいことに起因するものと考えられる.この誘電損失を小さくするためには,他元素の導入などによる改善が必要である.

#### 4. 結 論

本研究では、工程の簡略化を考慮し、シリコンと強誘電体を直接接合させる方式について、Si との反応が起こりにくいと考えられる  $YMnO_3$  をゾルーゲル法により作製し、薄膜の作製条件や誘電特性について評価を行った。その結果、以下の結論が得られた。

- 5.3vol% DEA を含む前駆体溶液を用いて単相の YMnO<sub>3</sub> 薄膜を作製できた.

- (2) 空気中でスピンコート法を用いることにより、 単相で均一な  $YMnO_3$  薄膜を得ることができた. このときの最小膜厚は8.8nm であった.

- (3) YMnO<sub>3</sub> の比誘電率は24であり, バルク体や乾 式法薄膜と同程度の値を得ることができた.

- (4) C-V 測定において、電荷のトラップがみられないことから、界面反応層は存在しないと考えられる.

- (5) YMnO<sub>3</sub> の誘電損失は22%程度であり、これは 膜の電気抵抗が低いことに起因する.

#### 参考文献

- 1) R.H. Dennar, F.H. Gaensslen, H.-N. Yu, V.L. Rideout, E. Bassous and A.R. LeBlanc, IEEE J. Solid-State Circuits, SC-9(5), 256(1974).

- 2) K. Ohta, K. Yamada, K. Shimizu and Y. Tarui, IEEE Trans. E. D., ED-29(3), 368(1982).

- 3) J.L. and Y. Tarui, IEEE Trans. Electron Devices, ED-10, 338(1963).

- 4) M. Yoshida, H. Yamaguchi, T. Sakuma and Y. Miyasaka, J. Electrochem. Soc., 142, 244 (1995).

- H. Tanaka, H. Tabata, T. Kawai and S. Kawai, Jpn.

J. Appl. Phys., 33, L451(1994).

- 6) J. Carrano, C. Sudhama, J. Lee, A. Tasch, W. Miller, IEEE IEDM Tech. Dig., 255 (1989).

- 7) 岡田 勝, 永富浩二, 応用物理, 第61巻, 1152(1992).

- 8) S.-Y. Wu, IEEE Trans. Electron Devices, ED-21(8), 499(1974).

- 9) J.L. Moll and Y. Tarui, IEEE Trans. Electron Devices, ED-10, 338(1963).

- 10) S. Sinharoy, H. Buhay, M.H. Francombe, W.J. Takei, N.J. Doyle, J.H. Riger, D.R. Lampe and E. Stepke, J. Vac. Sci. Tech., A9(3), 409(1991).

- N. Fujimura, T. Ishida, T. Yoshimura and T. Ito, Appl. Phys. Lett., 69, 1011 (1996).

- 12) 藤村, 伊藤, 田中, 忠永, 南, 第56回応用物理学会学術 講演会予稿集, II, 440(1996).